1. assign c = log2(a); // 行为级描述 chisel systemC

2. assign c = a + b; // RTL级描述

SOC内存

- 存储空间:NAND FLASH / BOOT-ROM //存放程序

- 运行/执行空间:DRAM

代码风格

- 代码中的模块不能没有output端口,可以没有input端口

- 两个反相器的输出接在一起,会造成不定态x

- 没有电平驱动的状态是高阻态z

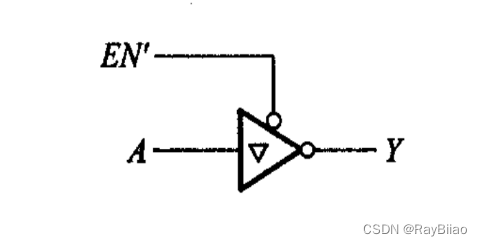

门控时钟

https://blog.csdn.net/eefresher/article/details/119516487

门控时钟电路

心中有电路

考虑PPA (0,1) 好的设计就是1,除此之外都是0(垃圾)

参考资料:VCS、DC、ICC、PT的user guide

尽可能使用always,不使用assign

always @(*)

if(a)

c = b;

else

c = c

always @(*)

if(a)

c = b;

// 会生成latch

同步复位和异步复位的电路

工艺库中只存在异步复位寄存器,同步复位是通过与门连接输入D实现的

为了系统的稳定性和确定性,尽可能使用异步复位,避免同步复位

电路优先级

alawys @(posedge clk) begin

if()

else if()

else if()

else

end

case(xx)

2'b00:

2'b01:

2'b10:

2'b11:

endcase

//具有相同的电路结构

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?