A.5 赋值语句、结构语句和程序块

阻塞和非阻塞赋值语句

- 阻塞赋值

前面语句执行完,才可执行下一条语句。

always @(posedge clk) begin

b = a;

c = b;

end

上面代码综合后产生1个触发器,在时钟clk上升沿到来时进行触发,此时会先将输入端a的值赋给输出端b,然后等待赋值完成后,将输出端b的新值再赋给c,最终相当于将a的值同时赋给了b和c。

- 非阻塞赋值

语句同时执行。

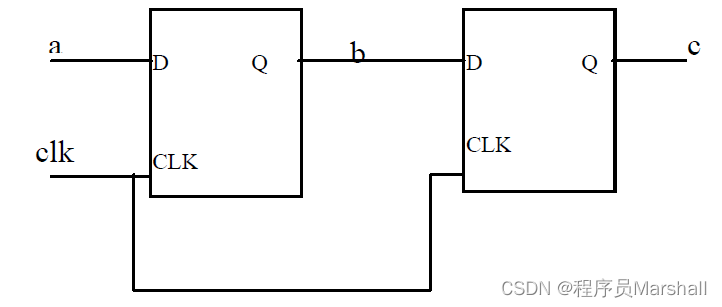

always @( posedge clk ) begin

b <= a;

c <= b;

end

上面代码综合后产生两个触发器,在时钟clk上升沿到来时进行触发,此时输入端a的值会赋给输出端b,从而使b的旧值更新为新值(b的新值为a),与此同时输出端b的旧值会赋给输出端c。

程序块语句

- 顺序执行

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

11万+

11万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?