iverilog是一个非常好的开源仿真器,可以直接在命令行中操作,结合vscode使用起来非常方便。但必须要强调的是,iverilog仿真器局限性很大,对systemverilog等新特性支持性不佳,仅能满足最基本的一些仿真编译需求,不过在一些小项目中还是比较有优势的,不需要再在modelsim中新建一个工程,省去了不少麻烦。

下载安装iverilog这里就不说了,不算很难,官网下载然后添加path就好了。

这里举例一个乘法模块的编写与仿真。

功能概述

FPGA中实现乘法并不容易,有时直接用*需要调用开发板自身的运算IP,这里自己写一个纯算法乘法,并进行tb仿真。

乘法模块

module multiplication(

input [3:0] a,

input [3:0] b,

output [7:0] product

);

integer i;

reg [7:0] multiplication;

always @(a or b) begin

multiplication = 0;

for (i = 0; i < 4; i = i + 1) begin

if (b[i]) begin

multiplication = multiplication + (a << i);

end

end

end

assign product = multiplication;

endmodule

tb模块

`timescale 1ns/1ps

module multiplication_tb;

reg [3:0] a;

reg [3:0] b;

wire [7:0] product;

multiplication uut(

.a(a),

.b(b),

.product(product)

);

initial begin

$dumpfile("multiplier_tb.vcd");

$dumpvars(0, multiplication_tb);

a = 4'b0000;

b = 4'b0000;

// 应用测试向量

#10 a = 4'b0011; b = 4'b0010; // 3 * 2 = 6

#10 a = 4'b0101; b = 4'b0011; // 5 * 3 = 15

#10 a = 4'b1111; b = 4'b1111; // 15 * 15 = 225

#10 a = 4'b0110; b = 4'b0100; // 6 * 4 = 24

#10 a = 4'b1001; b = 4'b0010; // 9 * 2 = 18

#10 $finish;

end

endmodule

注意,这里面的

$dumpfile("multiplier_tb.vcd");

$dumpvars(0, multiplication_tb);

必须要加,和Linux下使用vcs仿真一样,这两句是为了产生波形文件,后缀采用.vcd,(Linux下vcs一般采用.fsdb后缀文件,注意区别)

iverilog编译与仿真

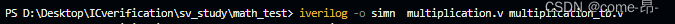

程序建立好后,直接在vscode中打开终端,按照

iverilog -o 你想要生成的仿真名称 仿真文件.v

的格式输入,例如,我这里是

之后会生成一个simn文件,

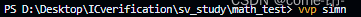

接着,执行这个文件:

vvp 你想要生成的仿真名称

例如,我这里是

如果程序正确没有报错,此时会产生一个.vcd文件,文件名就是你在$dumpfile("multiplier_tb.vcd");中命名的。

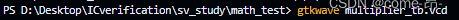

之后想要看波形,直接按照:

gtkwave vcd文件名称.vcd

例如我这里是

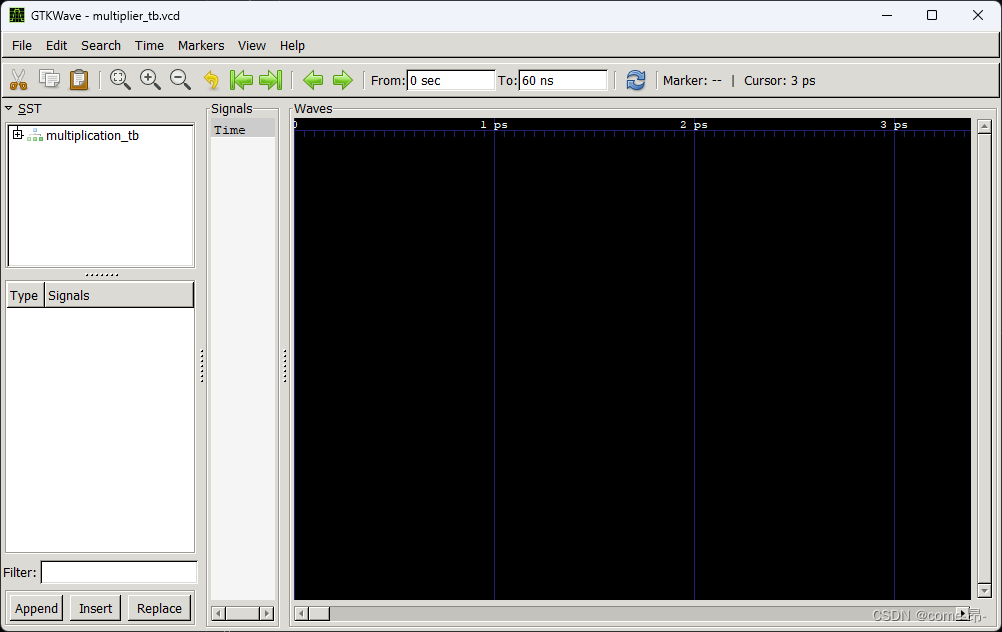

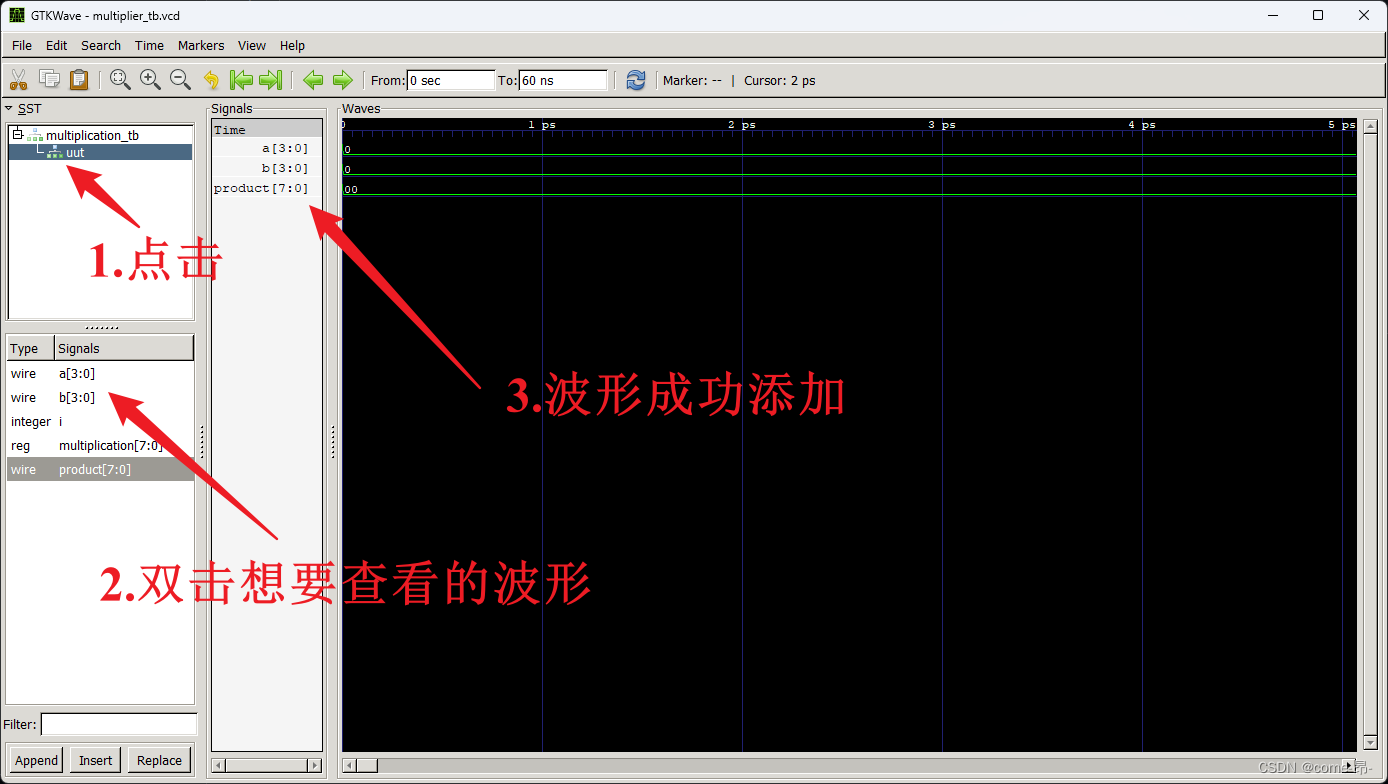

此时,桌面会弹出gtkwave波形查看程序,刚开始打开应该像下面的样子:

界面里什么都没有,不要急,像modelsim一样把信号添加进去就可以了。

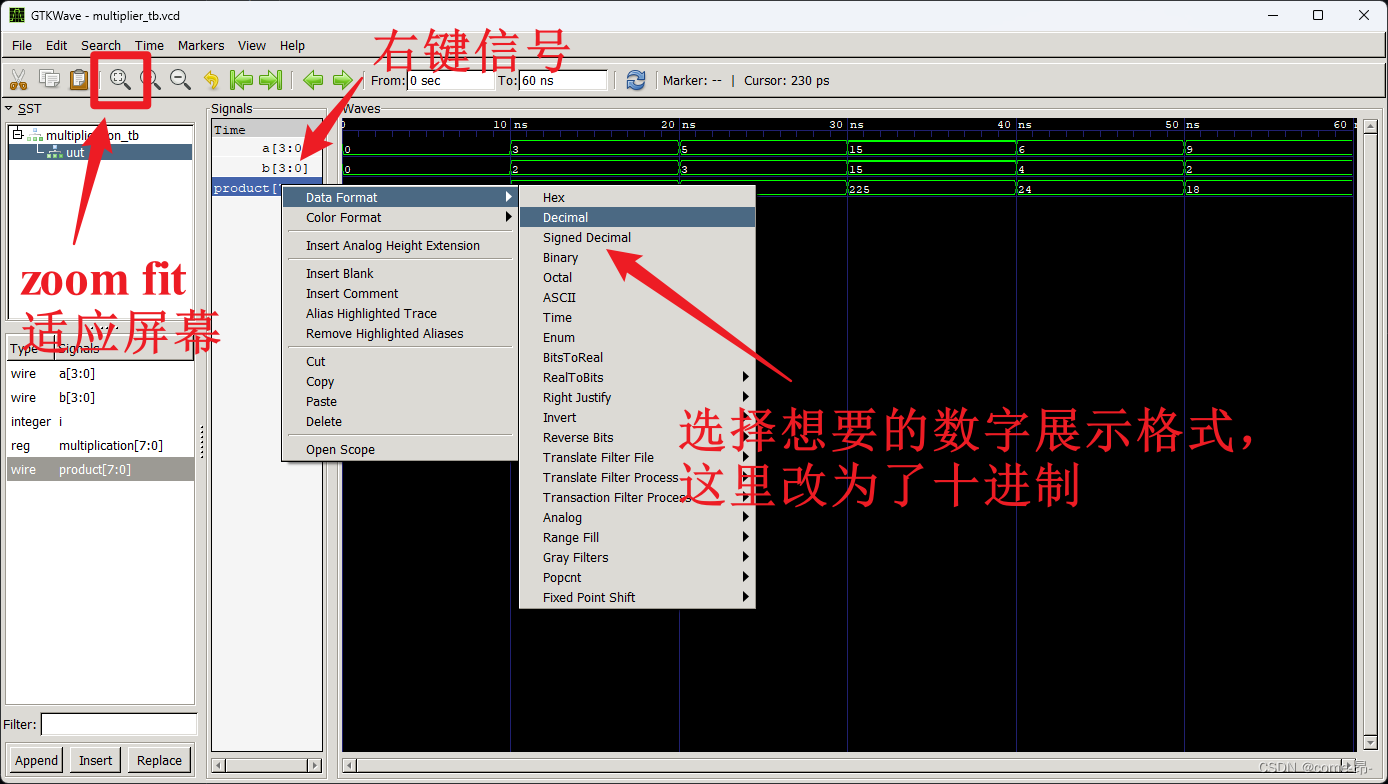

信号添加进来之后,这里并不像modelsim一样还需要点一次执行,这里加进来之后信号就已经跑出来了,可以点击下面的zoom fit适应窗口,就可以看到完整的波形了。也可以右键信号名称选择想要的数字展示格式。

完毕,一个完整的基于iverilog仿真编译的小程序成功测试。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?