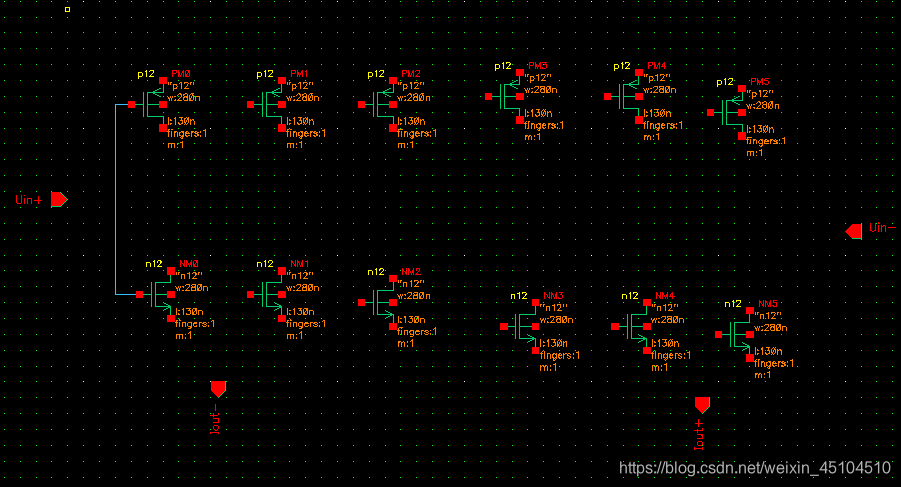

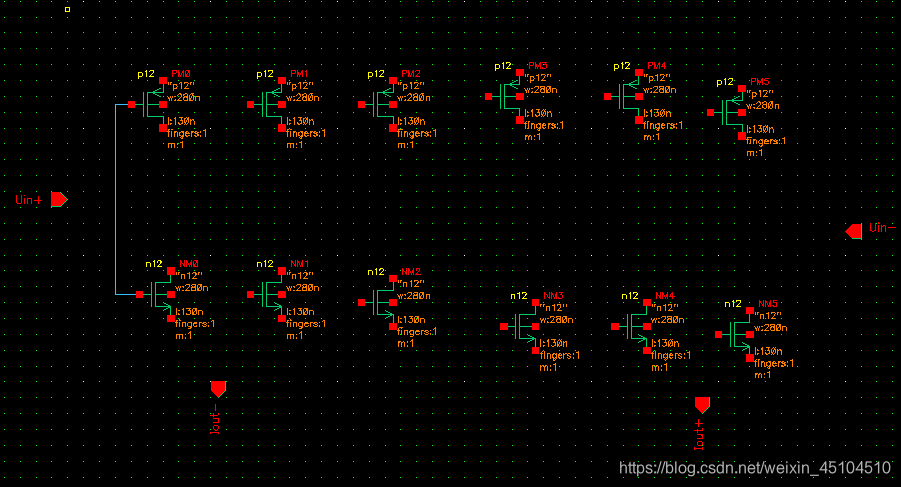

今天仿真一个运算放大器的时候忘记了器件镜像翻转快捷键,因为电路涉及到电流镜器件不镜像就很丑

找了很久找到了器件镜像快捷键:

找了很久找到了器件镜像快捷键:

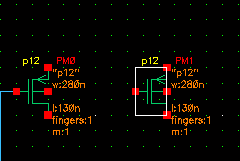

首先选中需要镜像的器件,如下图所示:

然后按 M 键,然后按shift+R

然后按 M 键,然后按shift+R

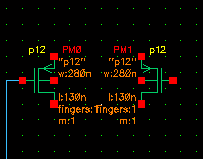

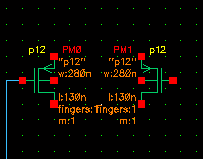

镜像完成。

镜像完成。

非常推荐大家关注我刚开通的 公众号【FPGA开发笔记】,我每天都会更新分享发布自己在FPGA开发过程中的心得和收货,也会分享一些硬件电路、模拟IC设计、电子DIY、嵌入式软件相关的文章。

今天仿真一个运算放大器的时候忘记了器件镜像翻转快捷键,因为电路涉及到电流镜器件不镜像就很丑

找了很久找到了器件镜像快捷键:

找了很久找到了器件镜像快捷键:

首先选中需要镜像的器件,如下图所示:

然后按 M 键,然后按shift+R

然后按 M 键,然后按shift+R

镜像完成。

镜像完成。

非常推荐大家关注我刚开通的 公众号【FPGA开发笔记】,我每天都会更新分享发布自己在FPGA开发过程中的心得和收货,也会分享一些硬件电路、模拟IC设计、电子DIY、嵌入式软件相关的文章。

5075

5075

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?