文章目录

前言

在数字设计、验证中经常接触的到断言,比如,验证中覆盖率收集就包含:代码覆盖率、功能覆盖率和断言覆盖率。最近正好在学习相关内容,整理笔记仅供参考。

一、断言是什么?

断言作为语言本身的组成部分,在功能模拟中不断监视,从而得知设计功能是否正确。可以认为是个“观测员”,可以观测程序的状态,但不会改变代码本身。SystemVerilog中的断言还可以用来提供功能覆盖。

相比硬件设计语言Verilog、SV,SVA是一种描述性语言,可以完美的描述时序相关的状况,语言的描述性本质提供了对时间卓越的控制,且语言容易维护,并且提供了内嵌函数,和构造函数自动收集功能覆盖率。

断言assertion被放在设计中,方便在仿真时查看异常情况。当异常出现时,断言会报警。一般在数字电路设计中都要加入断言,断言占整个设计的比例应不少于30%。

断言大概形式如下,

二、断言是设计属性的描述

1.如果一个在模拟中被检查的属性(property)不像我们期望的那样表现,那么这个断言失败。

2.如果一个被禁止在设计中出现的属性在模拟过程中发生,那么这个断言失败。

三、断言的语法结构主要分五个部分

第一层:布尔表达式,这个和Verilog中没有差别;

第二层:序列(sequence),其中包含一些新的操作符,如##时隙延迟、重复操作符、序列操作符等,序列是一个封装格式,采用序列封装后可以在不同地方使用,一个序列会被评估为真或者假;

第三层:属性(property),这是重要的封装方式,其中最重要的特点是属性内部可以定义蕴涵操作符(|->、|=>);

第四层:断言指示层(assert),也就是采用assert对特定属性或者序列做行为检查,或者采用cover做统计等;

第五层:封装(module、program、interface),断言的最后封装,只有通过最后封装成一个单元的断言才可以在不同的地方重用,就如同一个可以例化模块或者类,通常这一层可以通过module或者program、interface来封装。

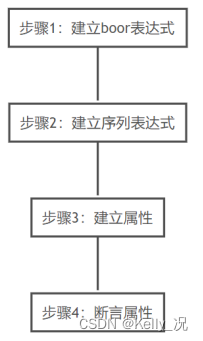

对应断言的构建过程如下,

四、断言操作符和系统函数

断言的操作符包含:##n、##[m:n]、

、

[

∗

n

]

、

[

∗

m

:

n

]

、

[

=

m

]

、

[

=

m

:

n

]

、

∣

−

>

、

∣

=

>

、

a

n

d

、

i

n

t

e

r

s

e

c

t

、

o

r

、

f

i

r

s

t

m

a

t

c

h

、

t

h

r

o

u

g

h

o

u

t

、

w

i

t

h

i

n

、

i

f

;

调

用

函

数

包

含

:

边

沿

检

查

函

数

(

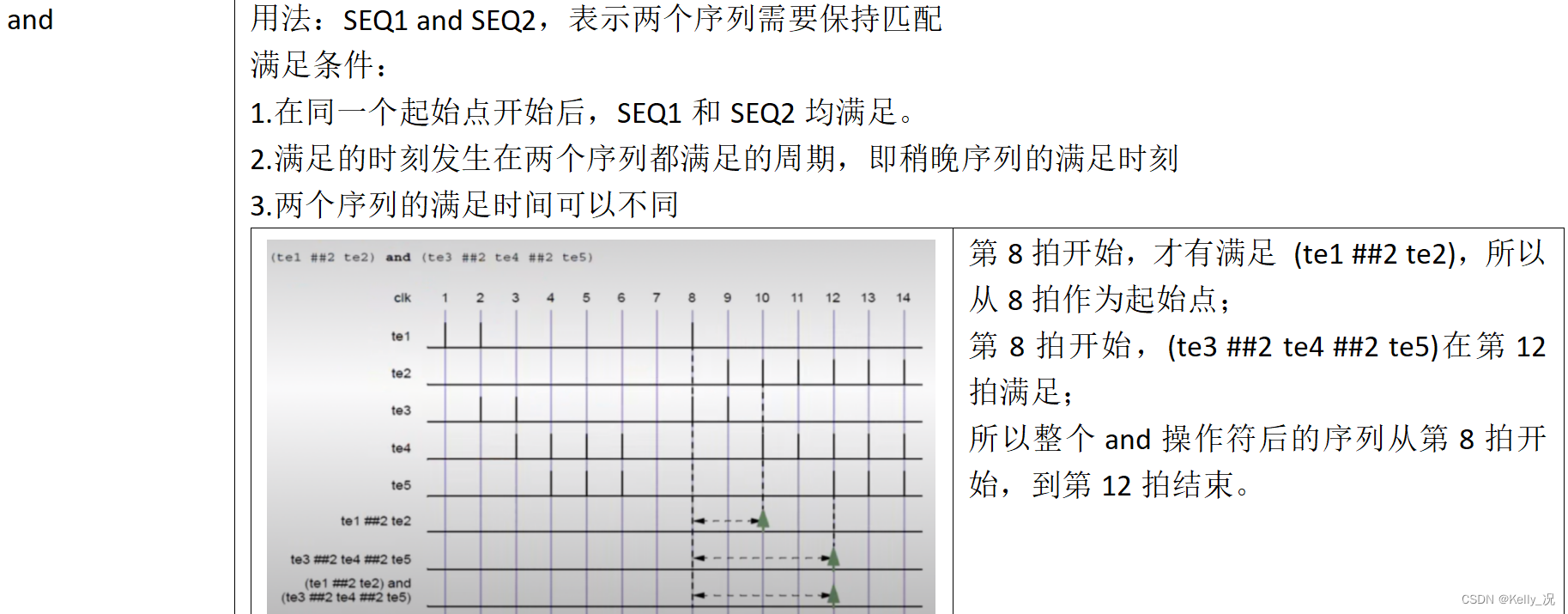

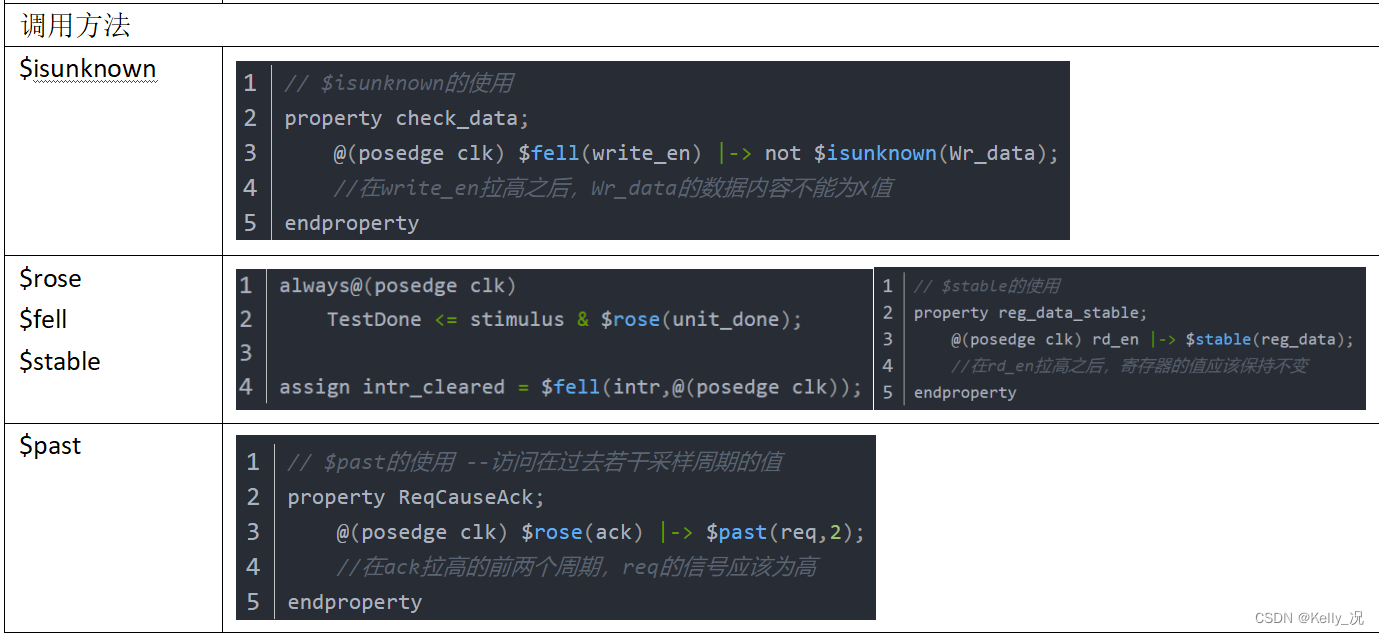

、[*n]、[*m:n]、[=m]、[=m:n]、|->、|=>、and、intersect、or、first_match、throughout、within、if; 调用函数包含:边沿检查函数(

、[∗n]、[∗m:n]、[=m]、[=m:n]、∣−>、∣=>、and、intersect、or、firstmatch、throughout、within、if;调用函数包含:边沿检查函数(rose、

f

e

l

l

、

fell、

fell、stable)、

i

s

u

n

k

n

o

w

n

、

isunknown、

isunknown、past等/

五、并发断言和立即断言

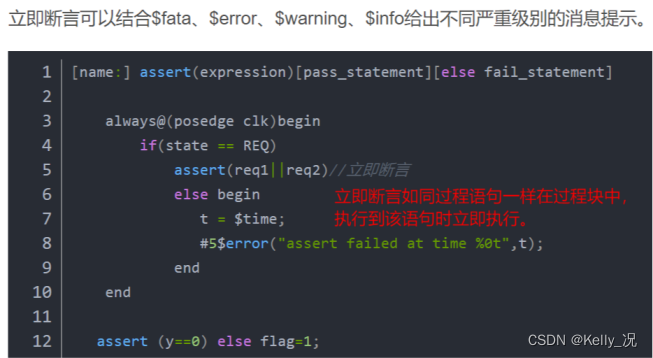

1. 立即断言

非时序的。

执行时如同过程语句。

它在程序执行到这个程序块时立即执行。

可以在过程块或者函数与方法中调用。

2. 并发断言

时序性的。

之所以称为并行,是指他们与设计模块一同并行执行。

关键词property用来区分立即断言和并行断言。

并行断言只会在时钟的边沿激活,变量的值是采样到的值。

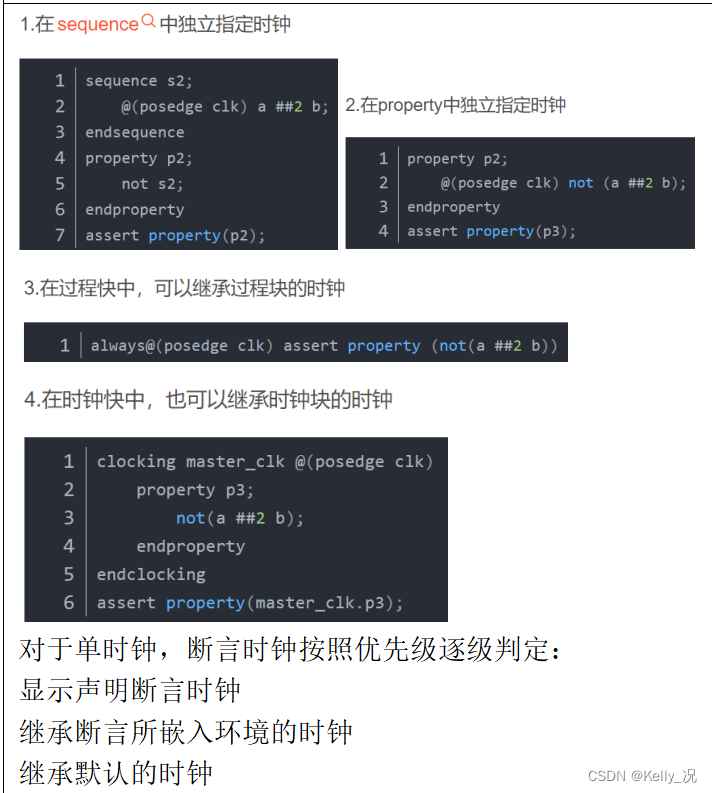

六、断言中的时钟声明

对于并行断言,其必须要具备时钟,property中可能具有单个时钟,也有可能是包括多个时钟。

1. 单时钟

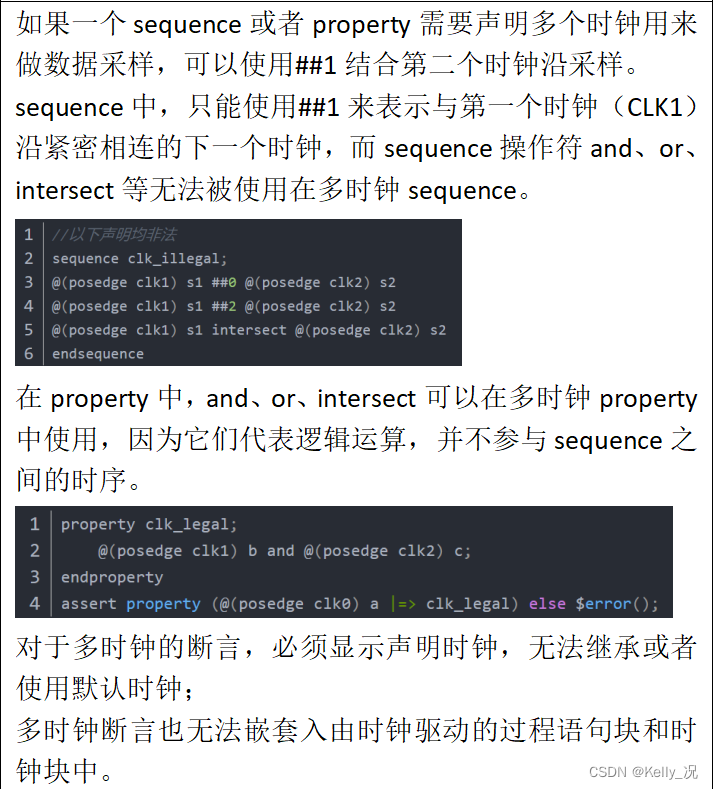

2. 多时钟

七、断言的绑定

断言既可以嵌入到设计中,也可以在设计外部定义。但是嵌入到设计内部,就需要考虑是否可以综合的问题,需要考虑添加编译定向。而在设计外部定义,不需要担心可综合的问题。

采用bind方法可以满足在设计外部定义断言,将断言绑定到设计内部或者接口上面;

bind 可以将包含断言的模块与设计模块或者实例进行绑定,既可以满足对设计信号的可视性,又能满足断言模块的独立性;

使用方法:bind design_block_or_instance_name block_with_assertion

使用绑定的优势:无需修改原有设计代码,也不需要添加监测信号,就可以实现断言的添加。

r1相当于range这个interface 的实例,将DUT的端口或者内部信号与它相连;

但是这个接口与验证环境TB中的interface有所不同之处:

(1)TB中的interface想看DUT内部层次以下的信号,可以访问DUT内部层次的方式,访问内部信号,例如tb.dut.a.b.sig1。但是绑定时的接口是看不到DUT的层次,只能看到DUT的端口和这一层的内部信号,看不到层次以下的信号;

(2)TB中的interface在例化后,其实体是存在于TB下的;而绑定时的接口例化后的实体是放在DUT内部。

291

291

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?