1.6.芯片设计趋势

我们将希望在未来的SoC项目中使用我们的原型环境,但是这些项目会是什么样子的呢?

了解芯片设计的八个主要趋势将导致对未来的项目的更好的准备和更灵活的内部原型方法。

推动半导体设计需求的八个主要趋势是:

- 进一步小型化到更小的技术节点。

- 整体设计的减少就开始了。

- 可编程性结合了嵌入式软件内容的快速增加。

- IP重用。

- 应用程序的特异性。

- 采用多核架构。

- 低功率。

- 芯片的模拟/混合信号部分的增加。

所有这些都对原型需求产生了深远的影响,我们将快速地查看它们及其支持的趋势数据

1.6.1.小型化到更小的技术节点

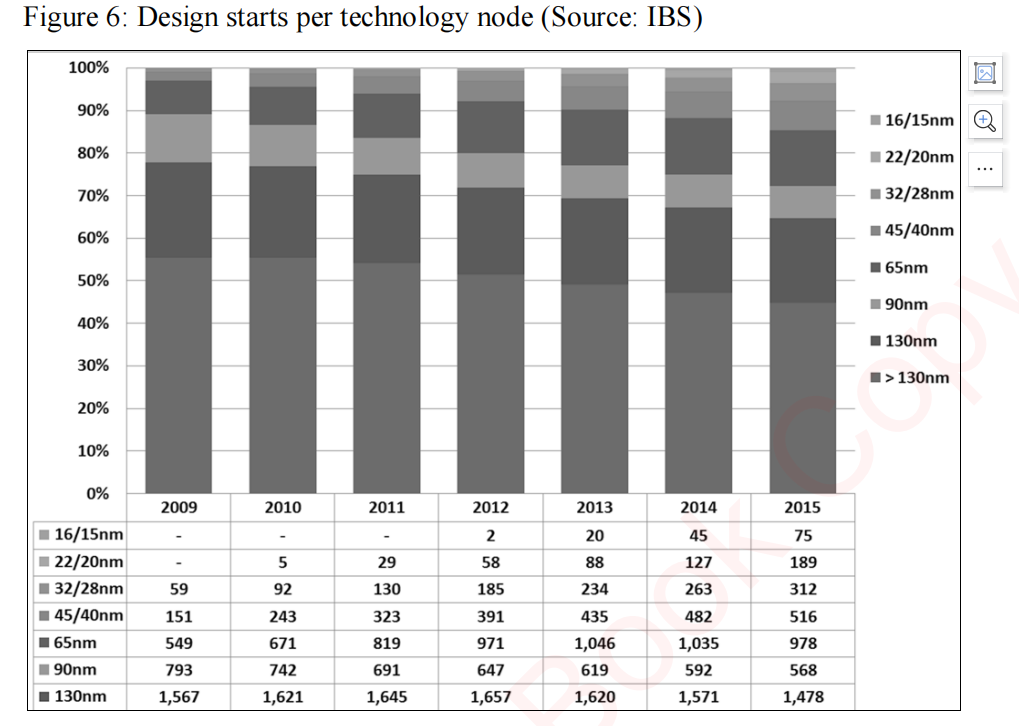

在处理器设计中,晶体管的数量从1979年定义X86的29,000个晶体管增加到2005年定义双核离子的17.2亿个晶体管。这比26年增长了近6万倍。这一趋势一直持续,并且可能在未来继续,从较小的技术节点开始进行的设计数量将会增加,如图6所示。该图表(由加州洛斯加托斯的国际商业战略公司(IBS)的行业分析师提供)显示了每个节点占所有ASIC和SoC设计开始的百分比。

65nm和45nm节点的设计始于2007年,现在已成为主流。因此,需要形成原型的设计的规模稳步增加,对基于软件和硬件的原型都需要越来越多的容量。

基于软件的原型的速度自然受到传统软件串行执行的限制。这进一步增加了提高软件模拟速度的压力,特别是对于处理器模型。

虽然自20世纪90年代末以来

订阅专栏 解锁全文

订阅专栏 解锁全文

328

328

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?