声明:

- 文章目的在于学习记录,知识分享。因个人能力有限:如有错误之处,请帮忙指出;如有疑问,欢迎随时交流。

在硅后的测试过程中,经常会遇到会遇到:在bootrom正常启动,完成初始化PCIe子系统,但其是无法正常link up。导致这个结果的可能性非常多,现在让我们站在Spec的角度,来逐一进行分析。

首先,肯定要通过查看主状态机来判断当前的变换轨迹,最简单的方式就是通过状态机轨迹进行初步方向的定位。

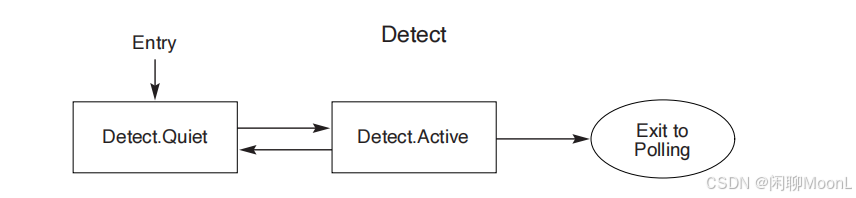

先看Detect状态。

如果发现状态机一直处于Detect状态,无法跳转至Poll,大概率问题有:

Receiver detect失败: 这种问题很常见,因为其不仅涉及板级的可靠性设计,也包括芯片内部电路设计的准确性。那如何进行隔离呢?

1. 一般设计都会支持Receiver detect Bypass功能。即:允许状态机忽略detect的结果,让状态机继续向后走。如果配置该功能后,可正常建链,问题得以证明。就需要检查相关设计是否可靠。

2.那如果第一步设置后,状态机仍然无法跳转到Poll状态,而是在Detect.quiet和detect.active状态只来来回跳转呢?那就需要来排查芯片内部的正确性。一般来说,可以通过(如果芯片支持的话。当然,强烈建议在设计之初就要添加足够多定位手段。)

2.1 确认SerDes是否支持local loopback模式,可进行LPBK测试,看是否正常;

2.2 确认PCIe 控制器是否支持PIPE looopback模式,可进行LPBK测试,看是否正常;

若以上都没有问题,这说明芯片设计本身存在问题的可能性较小,仍需进一步查看板级设计是否准备。比如:阻抗是否满足要求等等。

101

101

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?