一、设置页面

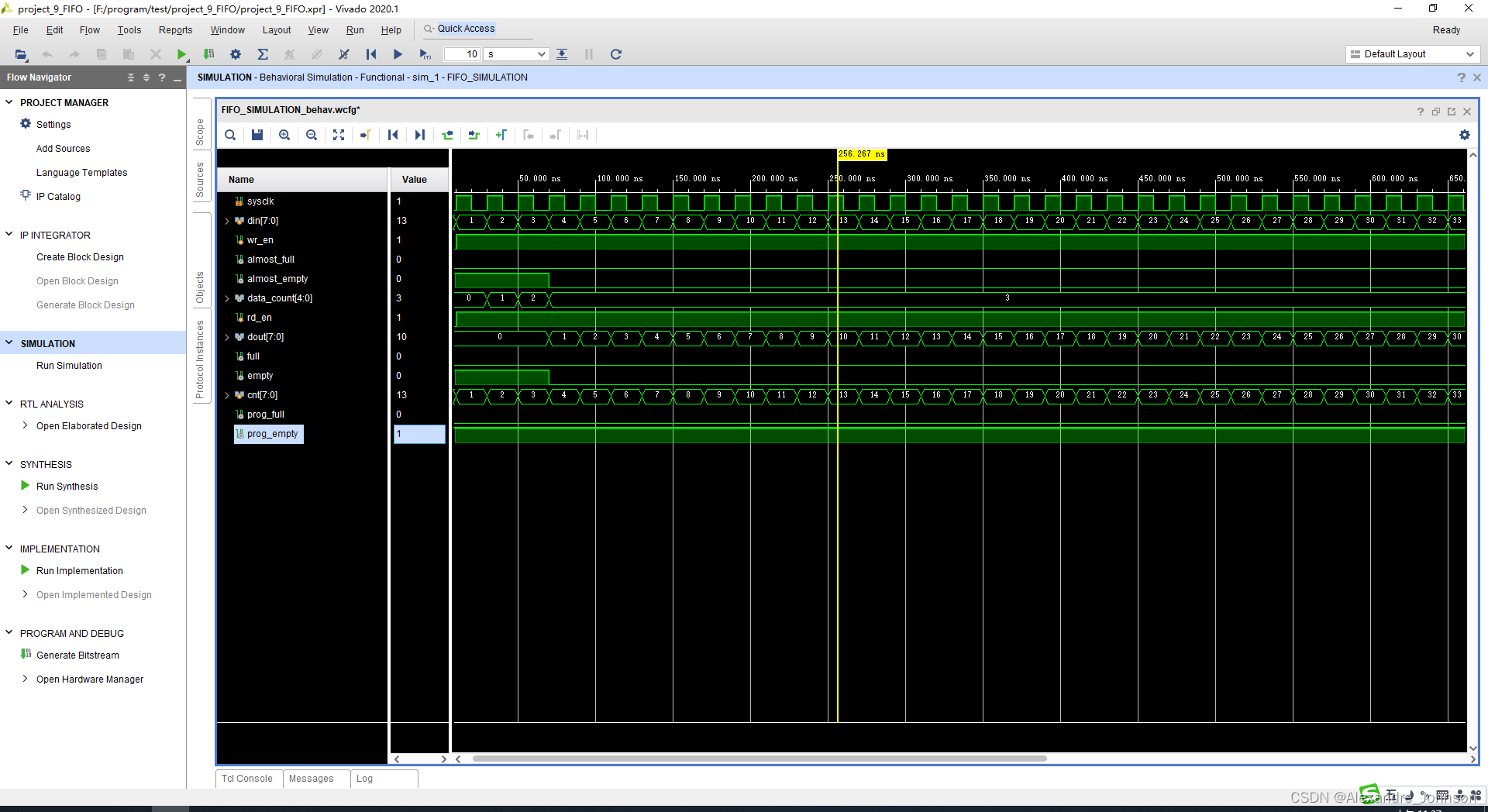

二、查看波形图

二、查看波形图

上测试代码

`timescale 1ns / 1ps

module fifo_study_simulation(

input sysclk

);

reg [7:0]din=0;

reg wr_en=0;

wire almost_full;

wire almost_empty;

wire [4:0] data_count;

reg rd_en=0;

wire [7:0]dout;

wire full;

wire empty;

reg [7:0]cnt=0;

wire prog_full;

wire prog_empty;

always@(posedge sysclk)

if(cnt<=190)

begin

wr_en<=1;

rd_en<=1;

din<=din+1;

cnt<=cnt+1;

end

else

begin

wr_en<=0;

end

fifo_study sdfsd (

//==============写端========================

.clk(sysclk), // input wire clk

.din(din), // input wire [7 : 0] din

.wr_en(wr_en), // input wire wr_en

/=============读端==========================

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [7 : 0] dout

.full(full), // output wire full

.almost_full(almost_full), // output wire almost_full

.empty(empty), // output wire empty

.almost_empty(almost_empty), // output wire almost_empty

.data_count(data_count), // output wire [4 : 0] data_count

.prog_full(prog_full),

.prog_empty(prog_empty)

);

endmodule

从上图中可以看到,虽然给了读信号,但是直到empty拉低的时候才开始读取

三、更改prog_empty信号,assert value改成6、negate value改成8

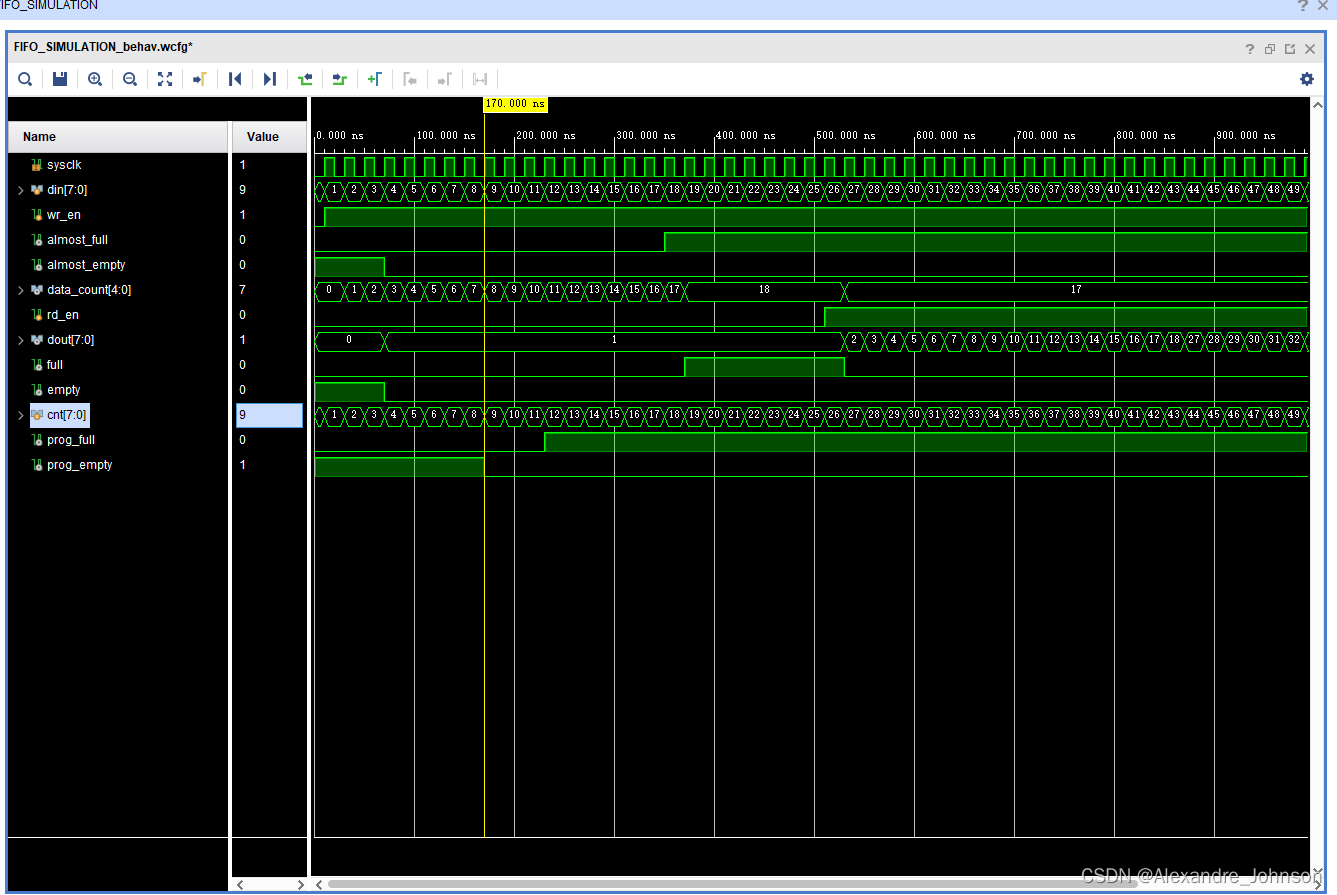

查看波形图

三、更改prog_empty信号,assert value改成4、negate value改成6

查看波形图

从二、三的波形图可以看出,pro_empty周期延迟了2个周期才拉低

从二、三的波形图可以看出,pro_empty周期延迟了2个周期才拉低

四、结合UART,查看波形

上测试代码

`timescale 1ns / 1ps

module fifo_uart(

input sysclk,

input rst_n,

input [7:0]din,

output [7:0]dout

);

reg wr_en;

reg rd_en;

wire full;

wire empty;

wire data_count;

always@(posedge sysclk)

if(!rst_n)

begin

wr_en<=0;

rd_en<=0;

end

else if(din)

begin

wr_en<=1;

rd_en<=1;

end

else

begin

wr_en<=0;

rd_en<=0;

end

fifo_generator_uart fifo_u (

.clk(sysclk), // input wire clk

.din(din), // input wire [7 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [7 : 0] dout

.full(full), // output wire full

.empty(empty), // output wire empty

.data_count(data_count) // output wire [3 : 0] data_count

);

endmodule

887

887

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?