4.1 Cortex-M 中断

4.1.1 中断简介

中断是微控制器一个很常见的特性,中断由硬件产生,当中断产生以后 CPU 就会中断当前的流程转而去处理中断服务,Cortex-M 内核的 MCU 提供了一个用于中断管理的嵌套向量中断控制器(NVIC)。

Cotex-M3 的 NVIC 最多支持 240 个 IRQ(中断请求)、1 个不可屏蔽中断(NMI)、1 个 Systick(滴答定时器)定时器中断和多个系统异常。

4.1.2 中断管理控制

Cortex-M 处理器有多个用于管理中断和异常的可编程寄存器, 这些寄存器大多数都在NVIC 和系统控制块(SCB)中, CMSIS 将这些寄存器定义为结构体。以 STM32F103 为例,打开core_cm3.h,有两个结构体, NVIC_Type 和 SCB_Type,如下:

typedef struct

{

__IO uint32_t ISER[8]; /*!< Offset: 0x000 Interrupt Set Enable Register */

uint32_t RESERVED0[24];

__IO uint32_t ICER[8]; /*!< Offset: 0x080 Interrupt Clear Enable Register */

uint32_t RSERVED1[24];

__IO uint32_t ISPR[8]; /*!< Offset: 0x100 Interrupt Set Pending Register */

uint32_t RESERVED2[24];

__IO uint32_t ICPR[8]; /*!< Offset: 0x180 Interrupt Clear Pending Register */

uint32_t RESERVED3[24];

__IO uint32_t IABR[8]; /*!< Offset: 0x200 Interrupt Active bit Register */

uint32_t RESERVED4[56];

__IO uint8_t IP[240]; /*!< Offset: 0x300 Interrupt Priority Register (8Bit wide) */

uint32_t RESERVED5[644];

__O uint32_t STIR; /*!< Offset: 0xE00 Software Trigger Interrupt Register */

} NVIC_Type; typedef struct

{

__I uint32_t CPUID; /*!< Offset: 0x00 CPU ID Base Register */

__IO uint32_t ICSR; /*!< Offset: 0x04 Interrupt Control State Register */

__IO uint32_t VTOR; /*!< Offset: 0x08 Vector Table Offset Register */

__IO uint32_t AIRCR; /*!< Offset: 0x0C Application Interrupt / Reset Control Register */

__IO uint32_t SCR; /*!< Offset: 0x10 System Control Register */

__IO uint32_t CCR; /*!< Offset: 0x14 Configuration Control Register */

__IO uint8_t SHP[12]; /*!< Offset: 0x18 System Handlers Priority Registers (4-7, 8-11, 12-15) */

__IO uint32_t SHCSR; /*!< Offset: 0x24 System Handler Control and State Register */

__IO uint32_t CFSR; /*!< Offset: 0x28 Configurable Fault Status Register */

__IO uint32_t HFSR; /*!< Offset: 0x2C Hard Fault Status Register */

__IO uint32_t DFSR; /*!< Offset: 0x30 Debug Fault Status Register */

__IO uint32_t MMFAR; /*!< Offset: 0x34 Mem Manage Address Register */

__IO uint32_t BFAR; /*!< Offset: 0x38 Bus Fault Address Register */

__IO uint32_t AFSR; /*!< Offset: 0x3C Auxiliary Fault Status Register */

__I uint32_t PFR[2]; /*!< Offset: 0x40 Processor Feature Register */

__I uint32_t DFR; /*!< Offset: 0x48 Debug Feature Register */

__I uint32_t ADR; /*!< Offset: 0x4C Auxiliary Feature Register */

__I uint32_t MMFR[4]; /*!< Offset: 0x50 Memory Model Feature Register */

__I uint32_t ISAR[5]; /*!< Offset: 0x60 ISA Feature Register */

} SCB_Type; NVIC 和 SCB 都位于系统控制空间(SCS)内, SCS 的地址从 0XE000E000 开始, SCB 和 NVIC的地址也在 core_cm3.h 中有定义,如下:

#define SCS_BASE (0xE000E000) /*!< System Control Space Base Address */

#define NVIC_BASE (SCS_BASE + 0x0100) /*!< NVIC Base Address */

#define SCB_BASE (SCS_BASE + 0x0D00) /*!< System Control Block Base Address */

#define SCB ((SCB_Type *) SCB_BASE) /*!< SCB configuration struct */

#define NVIC ((NVIC_Type *) NVIC_BASE) /*!< NVIC configuration struct */

4.1.3 优先级分组定义

多个中断来临的时候,处理器要处理哪个是由中断的优先级来决定的。优先级编号小的优先级高,会先得到响应,而且高优先级的中断可以抢占低优先级的中断,这个就是中断嵌套。

· Cortex-M 处理器有三个固定优先级和 256 个可编程的优先级,最多有 128 个抢占等级,但是实际的优先级数量是由芯片厂商来决定的。但是,绝大多数的芯片都会精简设计的,以致实际上支持的优先级数会更少,如 8 级、 16 级、 32 级等, 比如 STM32 就只有 16 级优先级。在设计芯片的时候会裁掉表达优先级的几个低端有效位,以减少优先级数,所以不管用多少位来表达优先级,都是 MSB 对齐的,如图就是使用三位来表达优先级。

在图中, Bit0~Bit4 没有实现,所以读它们总是返回零,写如它们的话则会忽略写入的值。因此,对于 3 个位的情况,可是使用的优先级就是 8 个: 0X00(最高优先级)、 0X20、 0X40、0X60、 0X80、 0XA0、 0XC0 和 0XE0。 注意,这个是芯片厂商来决定的!不是我们能决定的,比如 STM32 就选择了 4 位作为优先级!

有读者可能就会问,优先级配置寄存器是 8 位宽的,为什么却只有 128 个抢占等级? 8 位不应该是 256 个抢占等级吗?为了使抢占机能变得更可控, Cortex-M 处理器还把 256 个优先级按位分为高低两段:抢占优先级(分组优先级)和亚优先级(子优先级), NVIC 中有一个寄存器是“应用程序中断及复位控制寄存器(AIRCR)”, AIRCR 寄存器里面有个位段名为“优先级组”,如表所示:

| 位段 | 名称 | 类型 | 复位值 | 描述 |

| [31:16] | VECTKEY | RW | - | 访问钥匙:任何对该寄存器的写操作,都必须同时 0X05FA 写入此段,否则写操作被忽略。如读取此半字,则读回值为0XFA05 |

| 15 | ENDIANESS | R | - | 指示端设置: 1==大端(BE8), 0==小端,此值是在复位时确定的,不能更改。 |

| [10:8] | PRIGROUP | R/W | 0 | 优先级分组 |

| 2 | SYSRESETREQ | W | - | 请求芯片控制逻辑产生一次复位。 |

| 1 | VECTCLRACTIVE | W | - | 清零所有异常的活动状态信息,通常只在调试时用,或者在 OS 从错误中恢复时用。 |

| 0 | VECTRESET | W | - | 复位微控制器内核(调试逻辑除外),但此复位不影响芯片上在内核以外的电路 |

PRIGROUP 就是优先级分组, 它把优先级分为两个位段: MSB 所在的位段(左边的)对应抢占优先级, LSB 所在的位段(右边的)对应亚优先级,如表 所示:

| 分组位置 | 表达抢占优先级的位段 | 表达亚优先级的位段 |

| 0(默认) | [7:1] | [0:0] |

| 1 | [7:2] | [1:0] |

| 2 | [7:3] | [2:0] |

| 3 | [7:4] | [3:0] |

| 4 | [7:5] | [4:0] |

| 5 | [7:6] | [5:0] |

| 6 | [7:7] | [6:0] |

| 7 | 无 | [7:0] |

看一下 STM32 的优先级分组情况,我们前面说了 STM32 使用了 4 位,因此最多有 5 组优先级分组设置,这 5 个分组在 msic.h 中有定义,如下:

#define NVIC_PriorityGroup_0 ((uint32_t)0x700) /*!< 0 bits for pre-emption priority

4 bits for subpriority */

#define NVIC_PriorityGroup_1 ((uint32_t)0x600) /*!< 1 bits for pre-emption priority

3 bits for subpriority */

#define NVIC_PriorityGroup_2 ((uint32_t)0x500) /*!< 2 bits for pre-emption priority

2 bits for subpriority */

#define NVIC_PriorityGroup_3 ((uint32_t)0x400) /*!< 3 bits for pre-emption priority

1 bits for subpriority */

#define NVIC_PriorityGroup_4 ((uint32_t)0x300) /*!< 4 bits for pre-emption priority

0 bits for subpriority */

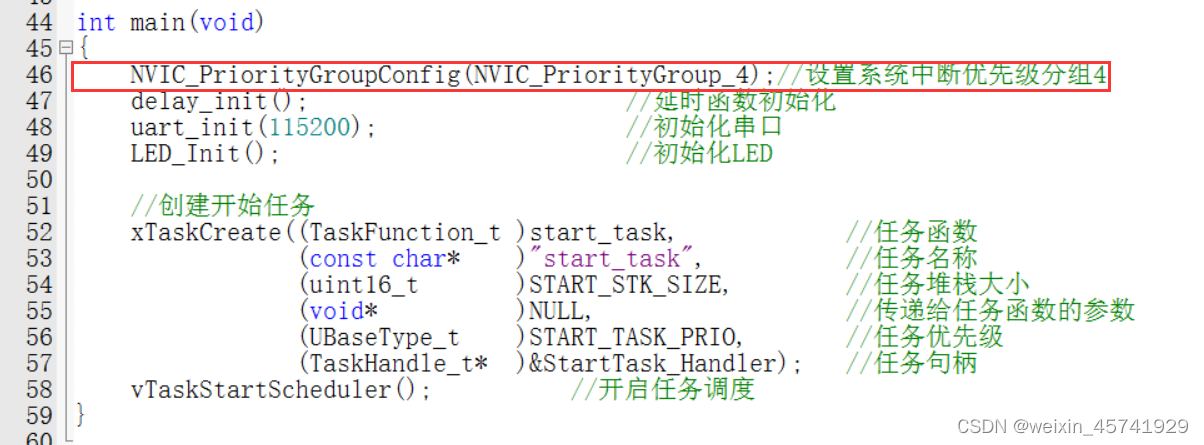

可以看出 STM32 有 5 个分组,但是一定要注意! STM32 中定义的分组 0 对应的值是 7!如果我们选择分组 4,即 NVIC_PriorityGroup_4 的话,那 4 位优先级就都全是抢占优先级了,没有亚优先级,那么就有 0~15 共 16 个优先级。而移植 FreeRTOS 的时候我们配置的就是组 4,如图所示:

主要是 FreeRTOS 的中断配置没有处理亚优先级这种情况,所以只能配置为组 4,直接就 16 个优先级,使用起来也简单!

4.1.4 优先级设置

每个外部中断都有一个对应的优先级寄存器,每个寄存器占 8 位,因此最大宽度是 8 位,但是最小为 3 位。 4 个相临的优先级寄存器拼成一个 32 位寄存器。如前所述,根据优先级组的设置,优先级又可以分为高、低两个位段,分别抢占优先级和亚优先级。 STM32 我们已经设置位组 4,所以就只有抢占优先级了。优先级寄存器都可以按字节访问,当然也可以按半字/字来访问,有意义的优先级寄存器数目由芯片厂商来实现,如表 4.1.4.1 和 4.1.4.2 所示:

| 名称 | 类型 | 地址 | 复位值 | 描述 |

| PRI_0 | R/W | 0xE000_E400 | 0(8 位) | 外中断#0 的优先级 |

| PRI_1 | R/W | 0xE000_E401 | 0(8 位) | 外中断#1 的优先级 |

| ... | ... | ... | ... | ... |

| PRI_239 | R/W | 0xE000_E4EF | 0(8 位) | 外中断#239 的优先级 |

4.1.5 用于中断屏蔽的特殊寄存器

我们在 STM32 上移植 FreeRTOS 的时候需要重点关注 PRIMASK、FAULTMASK 和 BASEPRI 这三个寄存器,本节就来学习一下这三个寄存器。

1、 PRIMASK 和 FAULTMASK 寄存器

在许多应用中,需要暂时屏蔽所有的中断一执行一些对时序要求严格的任务,这个时候就可以使用 PRIMASK 寄存器, PRIMASK 用于禁止除 NMI 和 HardFalut 外的所有异常和中断,汇编编程的时候可以使用 CPS(修改处理器状态)指令修改 PRIMASK 寄存器的数值:

CPSIE I; //清除 PRIMASK(使能中断)

CPSID I; //设置 PRIMASK(禁止中断)PRIMASK 寄存器还可以通过 MRS 和 MSR 指令访问,如下:

MOVS R0, #1

MSR PRIMASK, R0 ;//将 1 写入 PRIMASK 禁止所有中断以及:

MOVS R0, #0

MSR PRIMASK, R0 ;//将 0 写入 PRIMASK 以使能中断 UCOS 中的临界区代码代码保护就是通过开关中断实现的(UCOSIII 也可以使用禁止任务调度的方法来实现临界区代码保护,这里不讨论这种情况),而开关中断就是直接操作 PRIMASK寄存器的,所以在 UCOS 中关闭中断的时候时关闭了除复位、 NMI 和 HardFault 以外的所有中断!

FAULTMASK 比 PRIMASK 更狠, 它可以连 HardFault 都屏蔽掉,使用方法和 PRIMASK 类似, FAULTMASK 会在退出时动清零。汇编编程的时候可以利用 CPS 指令修改 FAULTMASK 的当前状态:

CPSIE F ;清除 FAULTMASK

CPSID F ;设置 FAULTMASK还可以利用 MRS 和 MSR 指令访问 FAULTMASK 寄存器:

MOVS R0, #1

MSR FAULTMASK, R0 ;将 1 写入 FAULTMASK 禁止所有中断以及:

MOVS R0, #0

MSR FAULTMASK, R0 ;将 0 写入 FAULTMASK 使能中断2、 BASEPRI 寄存器

PRIMASK 和 FAULTMASK 寄存器太粗暴了,直接关闭除复位、 NMI 和 HardFault 以外的其他所有中断,但是在有些场合需要对中断屏蔽进行更细腻的控制, 比如只屏蔽优先级低于某一个阈值的中断。那么这个作为阈值的优先级值存储在哪里呢?在 BASEPRI 寄存器中,不过如果向 BASEPRI 写 0 的话就会停止屏蔽中断。 比如,我们要屏蔽优先级不高于 0X60 的中断,则可以使用如下汇编编程:

MOV R0, #0X60

MSR BASEPRI, R0如果需要取消 BASEPRI 对中断的屏蔽,可以使用如下代码:

MOV R0, #0

MSR BASEPRI, R0注意! FreeRTOS 的开关中断就是操作 BASEPRI 寄存器来实现的!它可以关闭低于某个阈值的中断,高于这个阈值的中断就不会被关闭!

4.2 FreeRTOS 中断配置宏

4.2.1 configPRIO_BITS

此宏用来设置 MCU 使用几位优先级, STM32 使用的是 4 位,因此此宏为 4!

4.2.2 configLIBRARY_LOWEST_INTERRUPT_PRIORITY

此宏是用来设置最低优先级,前面说了, STM32 优先级使用了 4 位,而且 STM32 配置的使用组 4,也就是 4 位都是抢占优先级。 因此优先级数就是 16 个,最低优先级那就是 15。 所以此宏就是 15,注意!不同的 MCU 此值不同,具体是多少要看所使用的 MCU 的架构,本教程只针对 STM32 讲解!

4.2.3 configKERNEL_INTERRUPT_PRIORITY

此宏用来设置内核中断优先级, 此宏定义如下:

#define configKERNEL_INTERRUPT_PRIORITY

( configLIBRARY_LOWEST_INTERRUPT_PRIORITY << (8 - configPRIO_BITS) )宏 configKERNEL_INTERRUPT_PRIORITY 用来设置 PendSV 和滴答定时器的中断优先级,port.c 中有如下定义:

#define portNVIC_PENDSV_PRI ( ( ( uint32_t ) configKERNEL_INTERRUPT_PRIORITY ) <<16UL )

#define portNVIC_SYSTICK_PRI ( ( ( uint32_t ) configKERNEL_INTERRUPT_PRIORITY ) <<24UL )可 以 看 出 , portNVIC_PENDSV_PRI 和 portNVIC_SYSTICK_PRI 都 是 使 用 了 configKERNEL_INTERRUPT_PRIORITY , 为 什 么 宏 portNVIC_PENDSV_PRI 是 宏configKERNEL_INTERRUPT_PRIORITY 左移 16 位呢?宏 portNVIC_SYSTICK_PRI 也同样是左移 24 位。 4.1.4 小节讲过了, PendSV 和 SysTcik 的中断优先级设置是操作 0xE000_ED20 地址的, 这样一次写入的是个 32 位的数据, SysTick 和 PendSV 的优先级寄存器分别对应这个 32位数据的最高 8 位和次高 8 位,不就是一个左移 16 位,一个左移 24 位了。

PendSV 和 SysTick 优先级是在哪里设置的呢?在函数 xPortStartScheduler()中设置,此函数在文件 port.c 中,函数如下:

BaseType_t xPortStartScheduler( void )

{

configASSERT( configMAX_SYSCALL_INTERRUPT_PRIORITY );

configASSERT( portCPUID != portCORTEX_M7_r0p1_ID );

configASSERT( portCPUID != portCORTEX_M7_r0p0_ID );

#if( configASSERT_DEFINED == 1 )

{

volatile uint32_t ulOriginalPriority;

volatile uint8_t * const pucFirstUserPriorityRegister = ( uint8_t * )

( portNVIC_IP_REGISTERS_OFFSET_16 +

portFIRST_USER_INTERRUPT_NUMBER );

volatile uint8_t ucMaxPriorityValue;

ulOriginalPriority = *pucFirstUserPriorityRegister;

*pucFirstUserPriorityRegister = portMAX_8_BIT_VALUE;

ucMaxPriorityValue = *pucFirstUserPriorityRegister;

configASSERT( ucMaxPriorityValue == ( configKERNEL_INTERRUPT_PRIORITY &

ucMaxPriorityValue ) );

ucMaxSysCallPriority = configMAX_SYSCALL_INTERRUPT_PRIORITY &

ucMaxPriorityValue;

ulMaxPRIGROUPValue = portMAX_PRIGROUP_BITS;

while( ( ucMaxPriorityValue & portTOP_BIT_OF_BYTE ) == portTOP_BIT_OF_BYTE )

{

ulMaxPRIGROUPValue--;

ucMaxPriorityValue <<= ( uint8_t ) 0x01;

}

ulMaxPRIGROUPValue <<= portPRIGROUP_SHIFT;

ulMaxPRIGROUPValue &= portPRIORITY_GROUP_MASK;

*pucFirstUserPriorityRegister = ulOriginalPriority;

}

#endif /* conifgASSERT_DEFINED */

portNVIC_SYSPRI2_REG |= portNVIC_PENDSV_PRI; //设置 PendSV 中断优先级

portNVIC_SYSPRI2_REG |= portNVIC_SYSTICK_PRI; //设置 SysTick 中断优先级

vPortSetupTimerInterrupt();

uxCriticalNesting = 0;

prvStartFirstTask();

return 0;

}portNVIC_SYSPRI2_REG 是个宏,在文件 port.c 中由定义,如下:

#define portNVIC_SYSPRI2_REG ( * ( ( volatile uint32_t * ) 0xe000ed20 ) )4.2.4 configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY

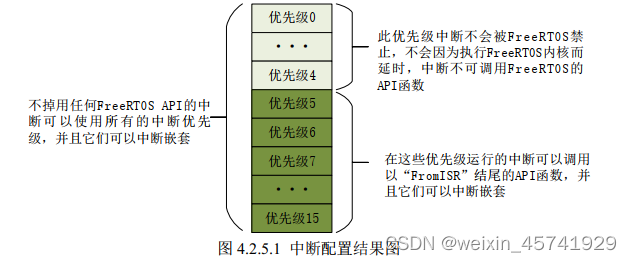

此宏用来设置 FreeRTOS 系统可管理的最大优先级,也就是我们在 4.1.5 小节中讲解BASEPRI 寄存器说的那个阈值优先级,这个大家可以自由设置,这里我设置为了 5。也就是高于 5 的优先级(优先级数小于 5)不归 FreeRTOS 管理!

4.2.5 configMAX_SYSCALL_INTERRUPT_PRIORITY

此宏是 configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY 左移 4 位而来的,原因和宏 configKERNEL_INTERRUPT_PRIORITY 一样。此宏设置好以后,低于此优先级的中断可以安全的调用 FreeRTOS 的 API 函数,高于此优先级的中断 FreeRTOS 是不能禁止的,中断服务函数也不能调用 FreeRTOS 的 API 函数!

以 STM32 为例,有 16 个优先级, 0 为最高优先级, 15 为最低优先级,配置如下:

● configMAX_SYSCALL_INTERRUPT_PRIORITY==5

● configKERNEL_INTERRUPT_PRIORITY==15

结果如图 4.2.5.1 所示:

由于高于 configMAX_SYSCALL_INTERRUPT_PRIORITY 的优先级不会被 FreeRTOS 内核屏蔽,因此那些对实时性要求严格的任务就可以使用这些优先级,比如四轴飞行器中的壁障检测。

4.3 FreeRTOS 开关中断

FreeRTOS 开关中断函数为 portENABLE_INTERRUPTS ()和 portDISABLE_INTERRUPTS(),这两个函数其实是宏定义,在 portmacro.h 中有定义,如下:

#define portDISABLE_INTERRUPTS() vPortRaiseBASEPRI()

#define portENABLE_INTERRUPTS() vPortSetBASEPRI(0)可以看出开关中断实际上是通过函数 vPortSetBASEPRI(0)和 vPortRaiseBASEPRI()来实现的,这两个函数如下:

static portFORCE_INLINE void vPortSetBASEPRI( uint32_t ulBASEPRI )

{

__asm

{

msr basepri, ulBASEPRI

}

}

/*-----------------------------------------------------------*/

static portFORCE_INLINE void vPortRaiseBASEPRI( void )

{

uint32_t ulNewBASEPRI = configMAX_SYSCALL_INTERRUPT_PRIORITY;

__asm

{

msr basepri, ulNewBASEPRI

dsb

isb

}

} 函数 vPortSetBASEPRI()是向寄存器 BASEPRI 写入一个值,此值作为参数 ulBASEPRI 传递进来, portENABLE_INTERRUPTS()是开中断,它传递了个 0 给 vPortSetBASEPRI(),根据我们前面讲解 BASEPRI 寄存器可知,结果就是开中断。

函 数 vPortRaiseBASEPRI() 是 向 寄 存 器 BASEPRI 写 入 宏configMAX_SYSCALL_INTERRUPT_PRIORITY , 那 么 优 先 级 低 于configMAX_SYSCALL_INTERRUPT_PRIORITY 的中断就会被屏蔽!

4.4 临界段代码

临界段代码也叫做临界区,是指那些必须完整运行,不能被打断的代码段,比如有的外设的初始化需要严格的时序,初始化过程中不能被打断。 FreeRTOS 在进入临界段代码的时候需要关闭中断,当处理完临界段代码以后再打开中断。 FreeRTOS 系统本身就有很多的临界段代码,这些代码都加了临界段代码保护,我们在写自己的用户程序的时候有些地方也需要添加临界段

代码保护。

FreeRTOS 与 临 界 段 代 码 保 护 有 关 的 函 数 有 4 个 : taskENTER_CRITICAL() 、taskEXIT_CRITICAL() 、 taskENTER_CRITICAL_FROM_ISR() 和taskEXIT_CRITICAL_FROM_ISR(),这四个函数其实是宏定义,在 task.h 文件中有定义。 这四个函数的区别是前两个是任务级的临界段代码保护,后两个是中断级的临界段代码保护。

4.4.1 任务级临界段代码保护

taskENTER_CRITICAL()和 taskEXIT_CRITICAL()是任务级的临界代码保护,一个是进入临界段,一个是退出临界段, 这两个函数是成对使用的,这函数的定义如下:

#define taskENTER_CRITICAL() portENTER_CRITICAL()

#define taskEXIT_CRITICAL() portEXIT_CRITICAL()而 portENTER_CRITICAL()和 portEXIT_CRITICAL()也是宏定义,在文件 portmacro.h 中有定义,如下:

#define portENTER_CRITICAL() vPortEnterCritical()

#define portEXIT_CRITICAL() vPortExitCritical()函数 vPortEnterCritical()和 vPortExitCritical()在文件 port.c 中,函数如下:

void vPortEnterCritical( void )

{

portDISABLE_INTERRUPTS();

uxCriticalNesting++;

if( uxCriticalNesting == 1 )

{

configASSERT( ( portNVIC_INT_CTRL_REG & portVECTACTIVE_MASK ) == 0 );

}

}

/*-----------------------------------------------------------*/

void vPortExitCritical( void )

{

configASSERT( uxCriticalNesting );

uxCriticalNesting--;

if( uxCriticalNesting == 0 )

{

portENABLE_INTERRUPTS();

}

}可以看出在进入函数 vPortEnterCritical()以后会首先关闭中断,然后给变量 uxCriticalNesting加一, uxCriticalNesting 是个全局变量,用来记录临界段嵌套次数的。函数 vPortExitCritical()是退出临界段调用的,函数每次将 uxCriticalNesting 减一,只有当 uxCriticalNesting 为 0 的时候才会调用函数 portENABLE_INTERRUPTS()使能中断。这样保证了在有多个临界段代码的时候不会因为某一个临界段代码的退出而打乱其他临界段的保护,只有所有的临界段代码都退出以后才会使能中断!

任务级临界代码保护使用方法如下:

void taskcritical_test(void)

{

while(1)

{

taskENTER_CRITICAL(); (1)

total_num+=0.01f;

printf("total_num 的值为: %.4f\r\n",total_num);

taskEXIT_CRITICAL(); (2)

vTaskDelay(1000);

}

}(1)、进入临界区。

(2)、退出临界区。

(1)和(2)中间的代码就是临界区代码,注意临界区代码一定要精简!因为进入临界区会关闭中断,这样会导致优先级低于 configMAX_SYSCALL_INTERRUPT_PRIORITY 的中断得不到及时的响应!

4.4.2 中断级临界段代码保护

函数 taskENTER_CRITICAL_FROM_ISR()和 taskEXIT_CRITICAL_FROM_ISR()中断级别临 界 段 代 码 保 护 , 是 用 在 中 断 服 务 程 序 中 的 , 而 且 这 个 中 断 的 优 先 级 一 定 要 低 于configMAX_SYSCALL_INTERRUPT_PRIORITY!原因前面已经说了。这两个函数在文件 task.h中有如下定义:

#define taskENTER_CRITICAL_FROM_ISR() portSET_INTERRUPT_MASK_FROM_ISR()

#define taskEXIT_CRITICAL_FROM_ISR( x ) portCLEAR_INTERRUPT_MASK_FROM_ISR( x )接 着 找 portSET_INTERRUPT_MASK_FROM_ISR() 和 portCLEAR_INTERRUPT_MASK_FROM_ISR(),这两个在文件 portmacro.h 中有如下定义:

#define portSET_INTERRUPT_MASK_FROM_ISR() ulPortRaiseBASEPRI()

#define portCLEAR_INTERRUPT_MASK_FROM_ISR(x) vPortSetBASEPRI(x)vPortSetBASEPRI()前面已经讲解了,就是给 BASEPRI 寄存器中写入一个值。函数 ulPortRaiseBASEPRI()在文件 portmacro.h 中定义的,如下:

static portFORCE_INLINE uint32_t ulPortRaiseBASEPRI( void )

{

uint32_t ulReturn, ulNewBASEPRI = configMAX_SYSCALL_INTERRUPT_PRIORITY;

__asm

{

mrs ulReturn, basepri (1)

msr basepri, ulNewBASEPRI (2)

dsb

isb

}

return ulReturn; (3)

}(1)、 先读出 BASEPRI 的值,保存在 ulReturn 中。

(2)、将 configMAX_SYSCALL_INTERRUPT_PRIORITY 写入到寄存器 BASEPRI 中。

(3)、返回 ulReturn,退出临界区代码保护的时候要使用到此值!

中断级临界代码保护使用方法如下:

//定时器 3 中断服务函数

void TIM3_IRQHandler(void)

{

if(TIM_GetITStatus(TIM3,TIM_IT_Update)==SET) //溢出中断

{

status_value=taskENTER_CRITICAL_FROM_ISR(); (1)

total_num+=1;

printf("float_num 的值为: %d\r\n",total_num);

taskEXIT_CRITICAL_FROM_ISR(status_value); (2)

}

TIM_ClearITPendingBit(TIM3,TIM_IT_Update); //清除中断标志位

} (1)、进入临界区。

(2)、退出临界区。

2478

2478

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?