一、Cadence介绍

Cadence 公司的 Allegro SPB 17.4 软件对 PCB 级电路系统设计流程,包括原理图输入,数字、模拟及混合电路仿真,FPGA 可编程逻辑器件设计,自动布局、布线,印制电路板图及生产制造数据输出,以及针对高速 PCB 的信号完整性分析与电源完整性分析等,从前到后提供了完整的输入、分析、板图编辑和制造的全线 EDA 辅助设计工具。

整个软件系统包含18个功能模块:

(1)Design Entry CIS: Design Entry CIS 是世界上领先的在 Windows 操作系统上实现的原理图输入解决方案,直观、简单易用且具有先进的部件搜索机制,是迅速完成原理图设计的最佳选择。Design Entry CIS 对应于以前版本的 Capture 和 Capture CIS,是 Cadence 公司收购原 OrCAD 公司的产品,是国际上通用的标准的原理图输入工具,设计快捷方便,图形美观,与 Allegro实现了无缝连接

(2)Design Entry HDL: Design Entry HDL提供了一个原理图设计和版图设计并行的工作环境,支持设计复用,并与数字、模拟和信号完整性前仿真器集成,可以灵活地进行多团队协作设计,减少设计返工。

(3)Design Entry HDL Rules Checker: Design Entry HDL的规则检查工具。

(4)FPGASystem Planner:缩减当今复杂的FPGA协同设计的时间。

(5)OrCADPCBEditor:原OrCAD 公司的PCB设计工具。(6)OrCADPCB Router: OrCADPCB的布线工具(Smart Route)。(7)Library Explorer:进行数字设计库管理的软件,可以调用 Design Entry HDL、PCBLibrarian、PCB Designer、Allegro System Architect 等工具建立元件符号和模型。(8)Cadence Help:在线帮助文档。

(9)ModelIntegrity:模型编辑与验证工具。(10)Package Designer: 片和封装的设计分析软件,它把芯片级的 I/0 可行性和规划功能与业界领先的集成电路封装设计工具组合到一起,形成一种强大的协同设计方法。该产品家族包括一个嵌入式、经过验证的 3D 场计算器,允许工程师在电气与物理设计要求之间做出折中选择,以满足成本和性能目标。

(11)PCB Editor:一个完整的高性能印制电路板设计软件。通过顶尖的技术,为创建和编辑复杂、多层、高速、高密度的印制电路板提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住最关键的设计问题。

(12)PCB Router: CCT 布线器

(13)PCB SI:提供了一个集成的高速设计与分析环境。它能流水线化完成高速数字印制电路板系统和高级集成电路封装设计,方便电气工程师在设计周期的所有阶段探究、优化和解决与电气性能相关的问题。约束驱动的设计流程提高了首次成功的概率并降低了产品的整体成本。

(14)Physical Viewer: Allegro 浏览器模块。

(15)Project Manager: Design Entry HDL 的项目管理器

(16)SigXplorer:网络拓扑的提取和仿真。

(17)AMS Simulator:工业标准的模拟、数字及模拟/数字混合信号仿真系统,仿真速度快,精度高,功能强大。仿真库内所含器件种类丰富,数量众多。

(18)PCB Editor Utilities: 包含 Pad Designer、DB Doctor 和 Batch DRC 等工具

二、新建工程:

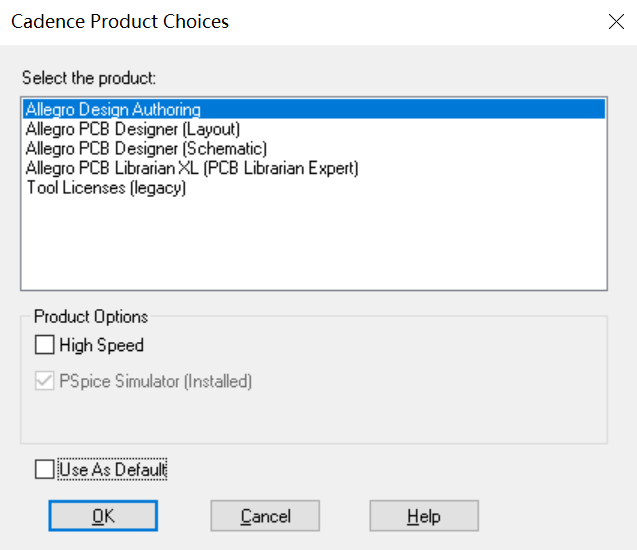

启动项目管理其界面

左下角“Use As Default”可勾选,下次不再弹出。

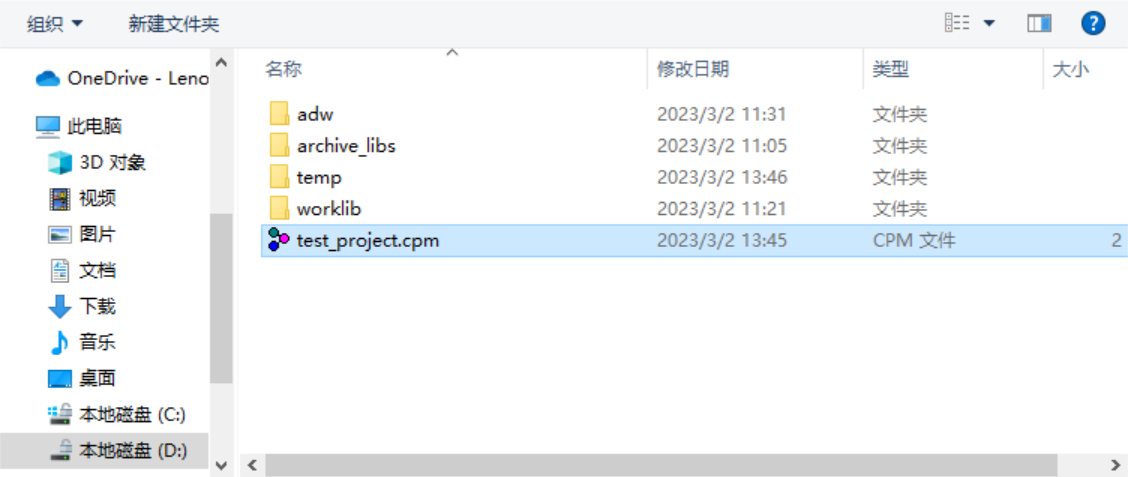

打开工程

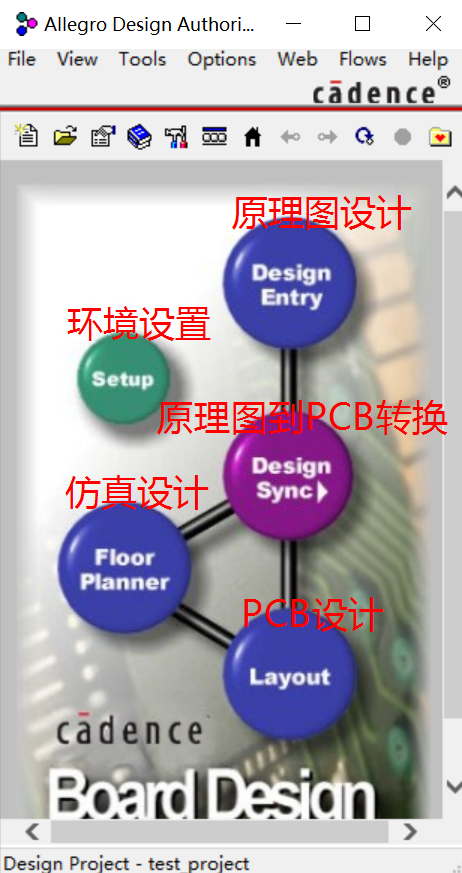

进入设计界面

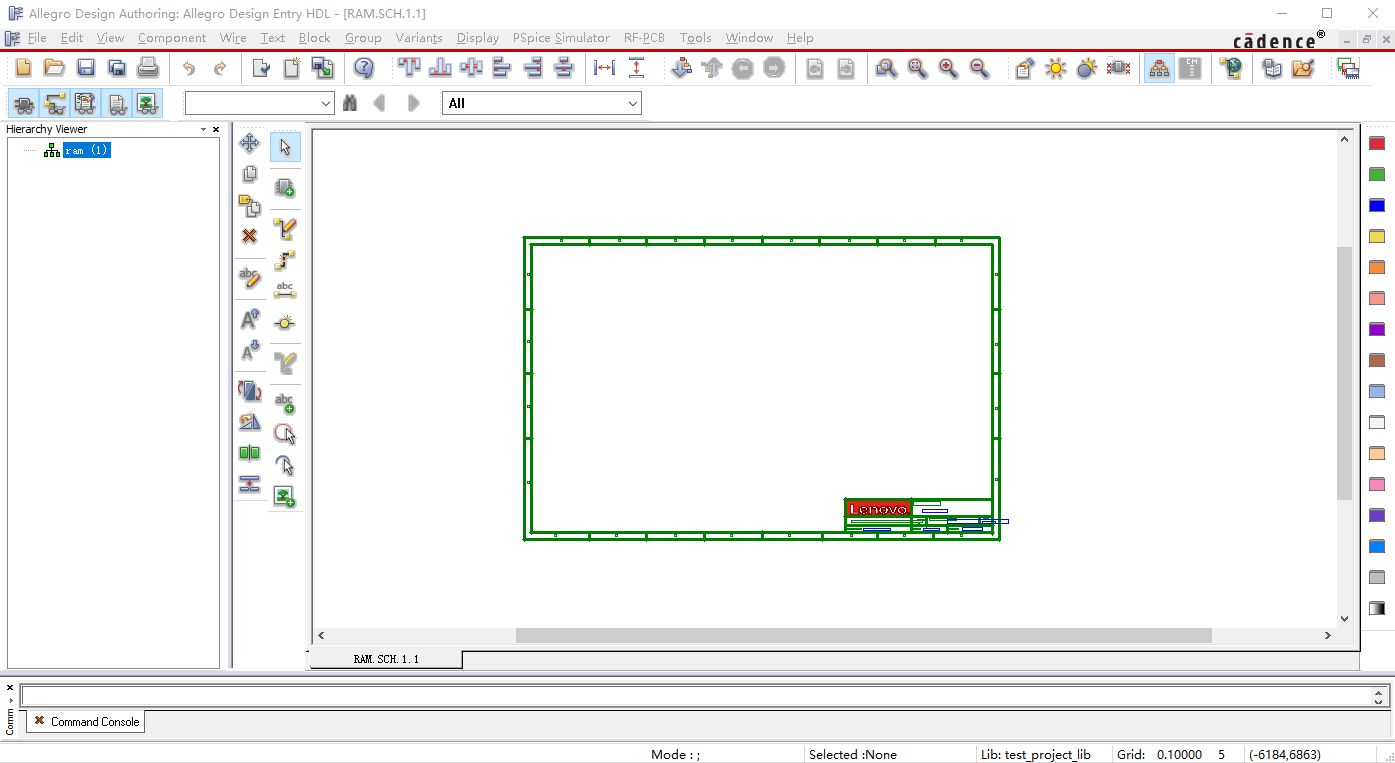

View->Hierarchy Viewer,确保层次窗口开启

View->Global Navigate,确保全局导航窗口关闭

3、页面转换

两个页面进行切换

4、显示未连接引脚

5、放大与缩放

放大原理图(F11/F12)

F5刷新视图

缩放局部原理图

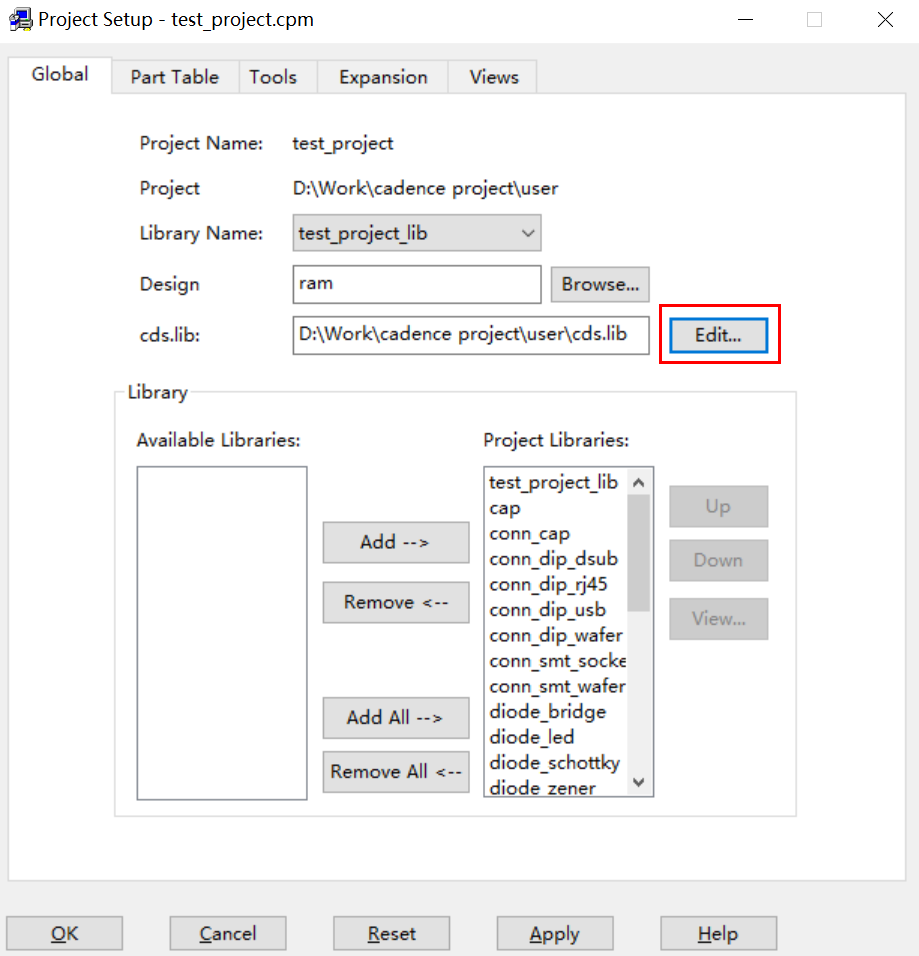

6、项目设置

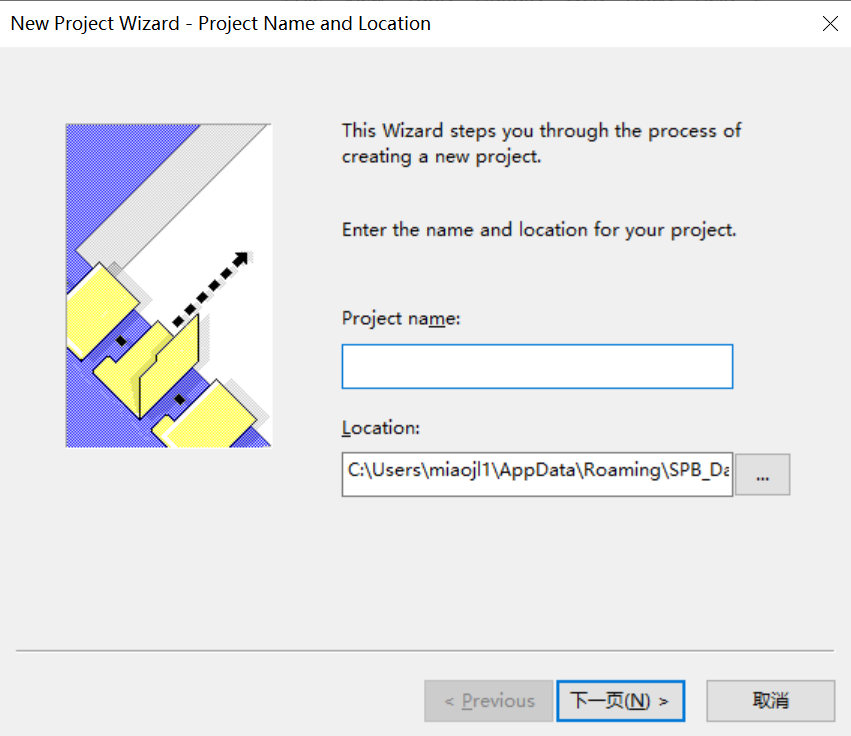

输入项目名称和保存位置

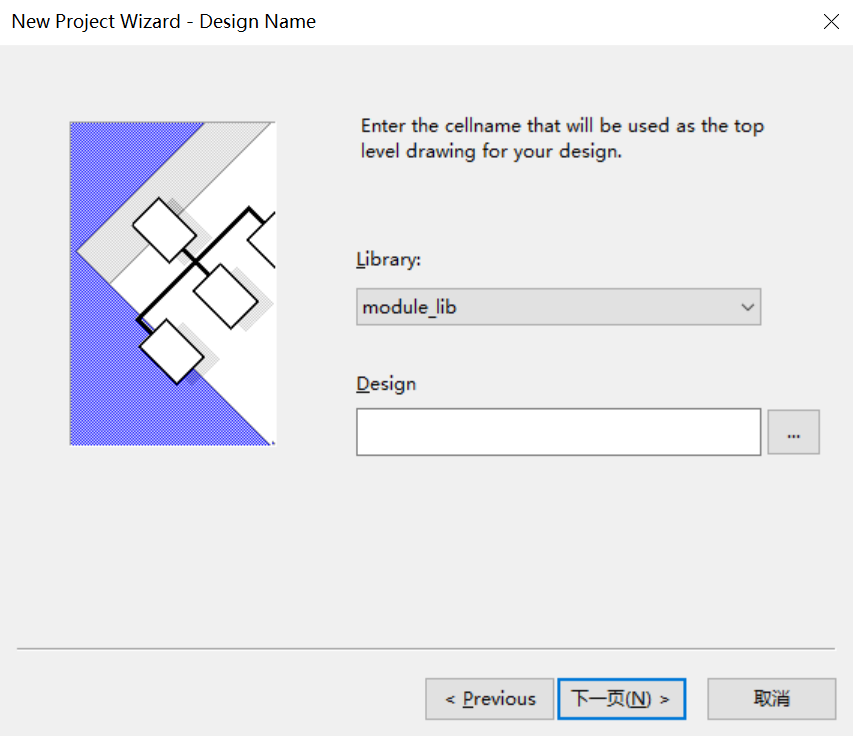

键入原理图图层名字

弹出“New project creation successful”新建工程成功

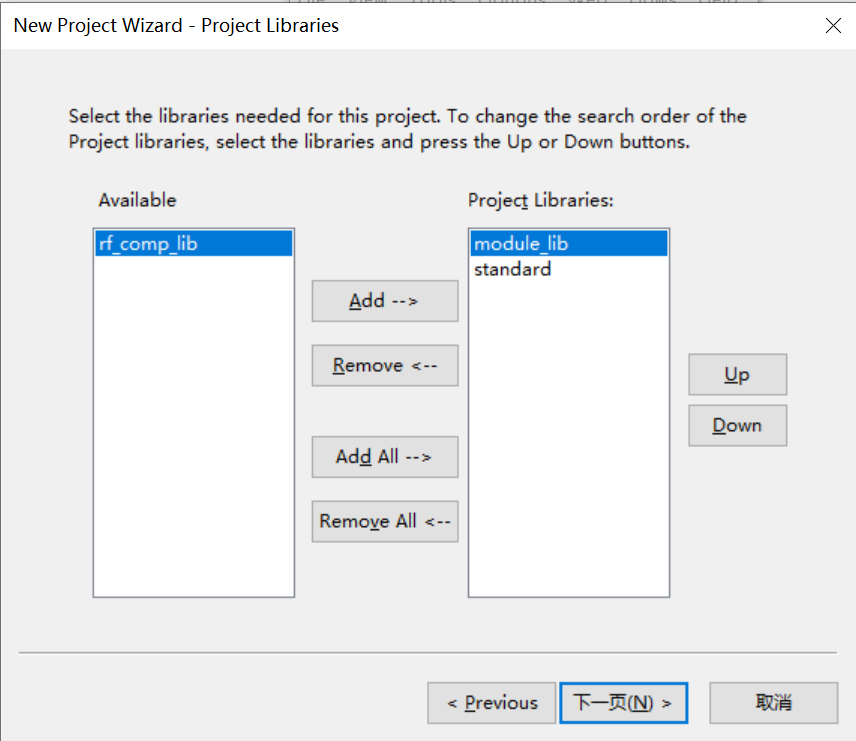

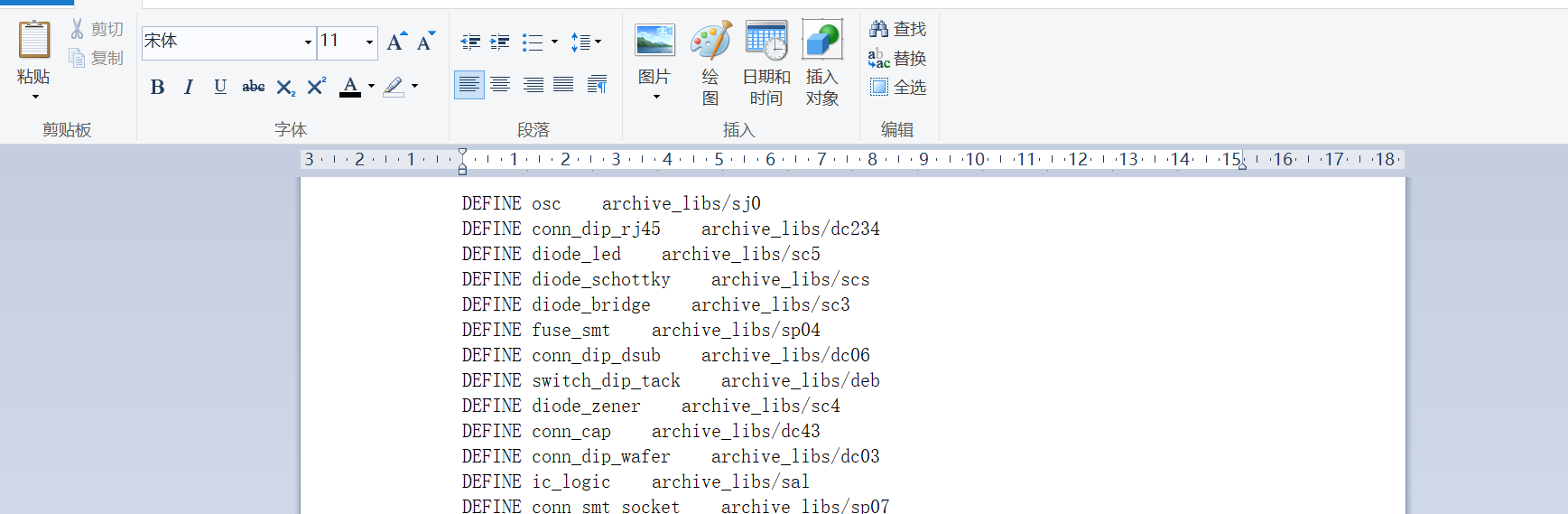

7、添加原理图库:

3150

3150

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?