一、DFI Interface

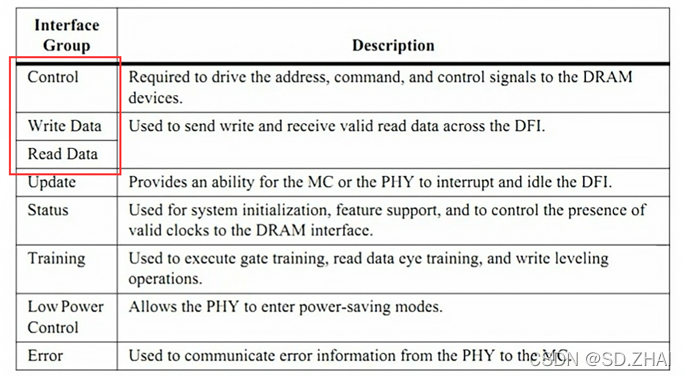

DFI接口是连接DDR Controller与DDR_PHY之间的通用接口,其信号组如下表.DFI Interface Group中常用的信号组主要包括Control、Write Data、Read Data三个信号组,其余诸如Update、Status等信号组用的较少。

各个信号组都由多个信号组成。

二、DFI Write Timing

DFI Write Timing1时序如下(tphy_wriat=3):图中的DFI Clock相当于是DDRC Clock,而DFI PHY Clock相当于是DDR Memory Clock,二者频率比为1:2。此时,DDRC控制器一段,一个时钟周期需要发出两个(p0、p1)DDR总线上的Command命令或者Data数据。

本文详细介绍了DFI Interface,作为连接DDR Controller与DDR PHY的通用接口,包括Control、Write Data、Read Data等信号组。重点讨论了DFI Write Timing的两种情况(tphy_writat=3和2)以及DFI Read Timing的两种配置(trddata_en=2和3),阐述了DFI Clock与DDR Memory Clock的关系以及在不同时序下的工作原理。

本文详细介绍了DFI Interface,作为连接DDR Controller与DDR PHY的通用接口,包括Control、Write Data、Read Data等信号组。重点讨论了DFI Write Timing的两种情况(tphy_writat=3和2)以及DFI Read Timing的两种配置(trddata_en=2和3),阐述了DFI Clock与DDR Memory Clock的关系以及在不同时序下的工作原理。

订阅专栏 解锁全文

订阅专栏 解锁全文

3063

3063

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?