参考:https://patentimages.storage.googleapis.com/3c/c6/56/9d4a3cfe4b3d95/CN101377691B.pdf

片上集成系统(SoC)中有多个功能模块,如处理器和各种硬件模块等。处理器通过修改各个硬件模块内部的控制寄存器来控制硬件模块的操作。同时,在为了降低功耗,每个硬件模块可能与处理器分别处于不同的时钟频率。例如,计算密集型模块需要在高频时钟下运行,而端口传输等模块可能在较低的时钟频率下运行。因此,当处理器配置内部模块的控制寄存器时,需要考虑跨时钟域的行为。传统上,处理器像APB总线,通过一定的总线模式访问内部模块的每个寄存器。

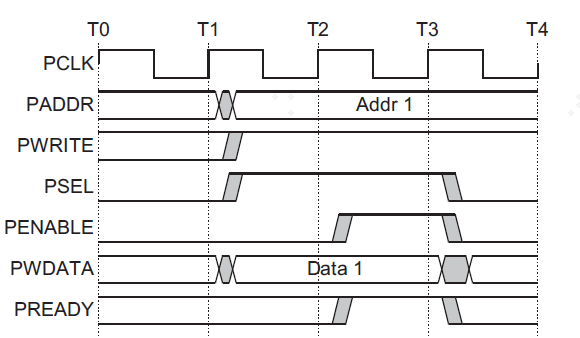

图1为无等待状态下的APB3.0主机写入数据示意图

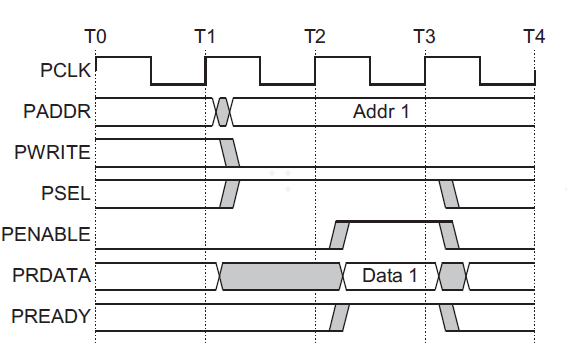

图2为APB3.0主机-主机协议读取数据示意图。

如图1、图2所示,PCLK为APB时钟区的时钟信号,PADDR为APB时钟区的地址信号;PWRITE为APB时钟区的写信号;PSEL为APB时钟区的片选信号,PENABLE为APB时钟区的使能信号,PWDATA为APB时钟区的写数据信号(图2中为PRDATA;为APB时钟的读数据信号zone), PREADY 是 APB 时钟区的握手。

APB总线主要用于低带宽外设之间的连接,例如UART、1284等,其总线架构不支持多个主模块,其唯一的主模块(master)就是APB桥接。

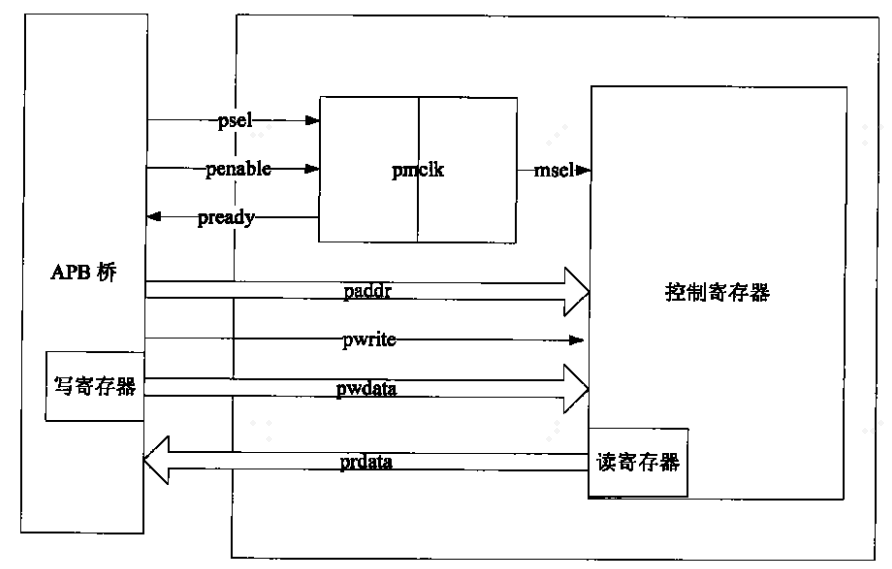

APB3.0的特点是:不定时钟周期传输;信号准备就绪,需要等待响应;如图3所示,转向逻辑很简单,只有四个控制信号,分别是PWRITE、PSEL、PENABLE、PREADY。

图3 APB桥接口信号和控制信号传输

系统初始化为IDLE状态,此时,尚未从模块中选择任何不传输操作。传输将执行时,PSEL=1,PENABLE=0,系统进入SETUP状态,在SETUP状态只能停止一个周期。当PCLK的下一个上升沿到来时,系统进入ENABLE状态。当系统进入ENABLE状态时,维持之前在SETUP状态的PADDR、PSEL、PWRITE不变,并将PENABLE变为1。传输会在 ENABLE状态下维持不定周期,在 ready信号为1的时候结束。之后,如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入 SETUP状态。

传统上,在利用APB总线访问硬件模块内部的寄存器的时候,模块的内部寄存器都必须和APB总线采用相同的时钟。在被访问模块的每个寄存器中一般都会设置一个状态位,用于指示APB桥对该寄存器的配置是否完成。当被访问模块中的所有寄存器都配置完毕后,再将最后一个寄存器的状态位设置为有效。在该状态位没有与模块时钟同步之前,模块中的控制寄存器到模块内部的路径都认为是无效路径( false path)。所述状态位通过两级寄存器实现与模块时钟的同步。所述状态位与模块时钟同步之后,模块发现该状态位有效,再采用各个控制寄存器的配置。

2307

2307

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?