日常·唠嗑

接上一篇Litedram仿真验证(三):AXI接口完成仿真(FPGA/Modelsim)之后,本篇对仿真后的工程进行板级验证。

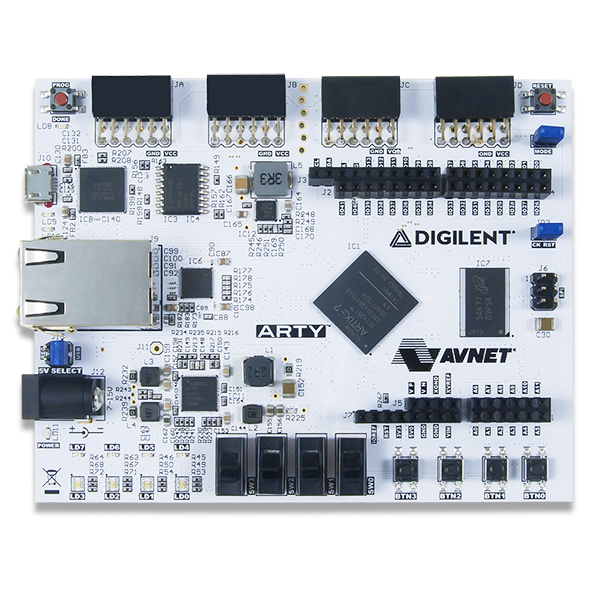

本次板级验证用到的开发板:Arty-a7,目前已经停产了,某宝上面还有卖,溢价比较严重。

板子资料链接:https://digilent.com/reference/programmable-logic/arty-a7/start

需要科学上网才能打开,因为是官方的板子资料很详细,有需要可以看看。

FPGA:xc7a35tcsg324-1

DDR3:MT41K128M16

一、仿真中遗留的问题

在上一篇文章中,提到AXI读写中,读会读不出来:

本文介绍了基于Litedram软核在FPGA Artix7平台上进行DDR3控制器的板级验证过程。作者通过调试解决了DDR3初始化问题,进行了板级测试,并使用ILA和逻辑分析仪抓取波形验证。最后,作者提供了工程获取和交流的方式。

本文介绍了基于Litedram软核在FPGA Artix7平台上进行DDR3控制器的板级验证过程。作者通过调试解决了DDR3初始化问题,进行了板级测试,并使用ILA和逻辑分析仪抓取波形验证。最后,作者提供了工程获取和交流的方式。

订阅专栏 解锁全文

订阅专栏 解锁全文

2388

2388

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?