VCS仿真代码:https://github.com/CJH8668/risc_cpu

仿真前除了按照原作者的步骤修改相应文件,还需修改cputop.v:line 47 $stop改为$finish,这样可以让simulation结束,再make verdi,就能正常查看波形了

《verilog数字系统设计教程第三版》夏宇闻

链接:https://pan.baidu.com/s/1VLb4x14WM5uUfYkFvyWM_Q

提取码:8rez

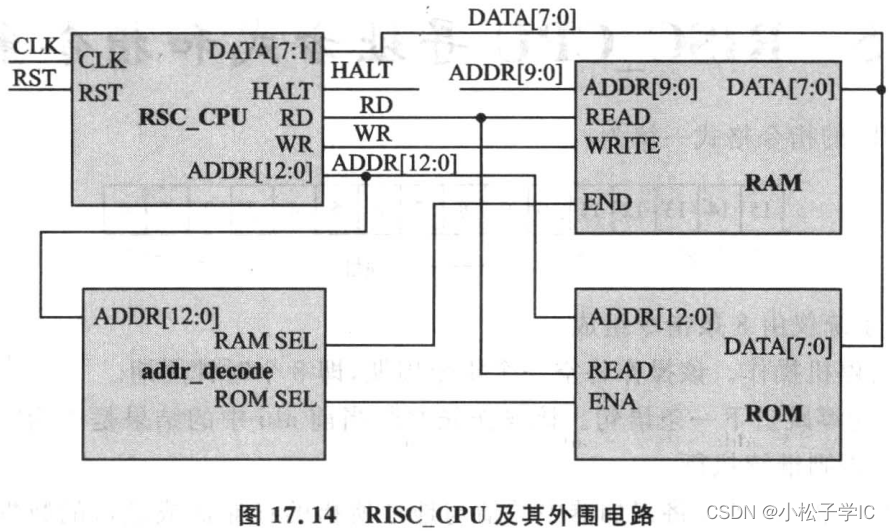

一.RISC_CPU及其外围电路

addr_decode:地址译码器

选通RAM或ROM:1FFFH-1800H RAM 17FFH-0000H ROM

ROM:存储程序,只读

使能且读有效时,读相应地址下的数据(data=rom[addr];)

RAM:存储数据,可读可写

*DATA 是inout类型

读数据:使能且读有效时,读相应地址的数据(data=ram[addr];)

写数据:写上升沿,写数据到相应地址中(ram[addr]<=data;)

二.RISC_CPU 操作和时序

1.系统的复位和启动

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

310

310

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?