基于Riffa框架开发PCIe

Riffa 框架简介

关于PCIE的控制涉及到的知识十分复杂,对于公司在开发时,需要软件和FPGA相互进行配合进行开发才能开发出一个可以实际应用的控制代码。软件工程师在开发时有许多可供调用的函数库,同样的,FPGA开发时也有开源的库可以使用。采用开源的Riffa框架来完成PCIE测试环境的搭建,能够加快开发效率

开源的Riffa框架的Github仓库地址如下:

Riffa仓库地址

Riffa框架中,包含了PCIE开发相关的FPGA开发代码和上位机源码。

PCIE IP 核配置

AXI总线时钟选择62.5M,AXI总线接口位宽设置为64bit。

在IDs界面是PCIE设备的相关信息,主机在上电时BIOS系统中识别到的PCIE设备,就是通过这些ID号来进行识别的。

在本实验中,关于ID的设定全部保持为默认值即可,若用户对ID进行了更改,可能导致计算机在启动时不能正确识别设备从而导致蓝屏死机。

Vendor ID是厂商ID,本实验中的厂商ID代值的就是Xilinx;

Device ID代表了PCIE设备,其中7指的是Xilinx 7 系列FPGA,02指的是使用的PCIE 2.0 的协议,1指的是含有一个PCIE的传输Lane;

Base class Menu指的是PCIE设备的种类,常见的有声卡,显卡,网卡等,各种不同种类的设备都有其对应的驱动,若驱动与其PCIE的种类不对应,就会导致系统的内存访问错误,从而导致蓝屏。

在PCIE的BARs配置界面对PCIE的BAR进行设置,BAR空间对应的就是在内存中开辟一段空间用于存放PCIE设备的信息。只使用到一个BAR0一个BAR且将其内存空间的大小设置为1K。

IP核的负载选择最大负载长度为512字节,勾选对数据进行缓冲。

在中断配置界面,取消勾选传统类型的中断,只选择消息类型的中断。

在share logic界面取消勾选包含其他逻辑,这样在PCIE的IP核中就包含了全部功能。

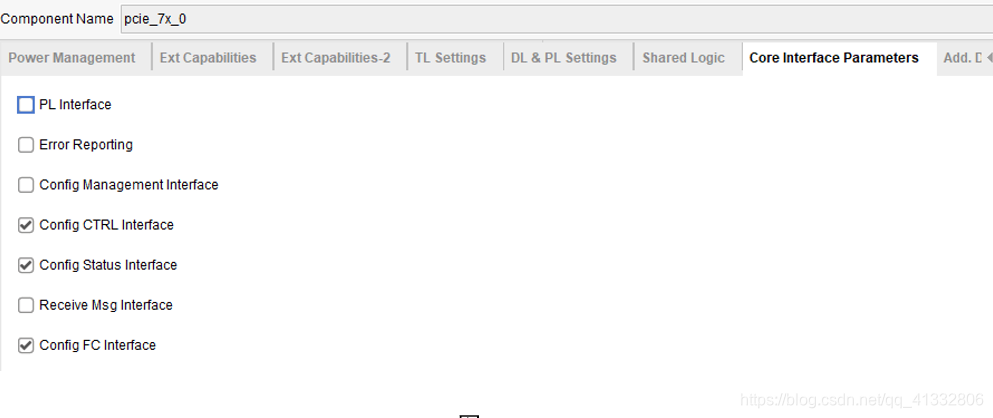

在IP核接口参数配置界面,只选择其中用于配置核控制的参数,这是由于Riffa框架的特性所提供的。

搭建Riffa框架

对于Riffa框架的移植,需要将FPGA文件夹中的riffa_hdl全部添加到工程当中,除此之外,由于我使用的artix-7的芯片,因此在fpga目录下的具体工程下面将AC701对应的riffa_wrapper和工程的顶层文件复制,然后添加到自己的工程中。

搭建好框架后,可以看到PCIE的IP核找不到文件,只需要将代码中的PCIE的IP核的名称更改为前面生成的PCIE IP核的名称即可。

还需要修改其中的参数。

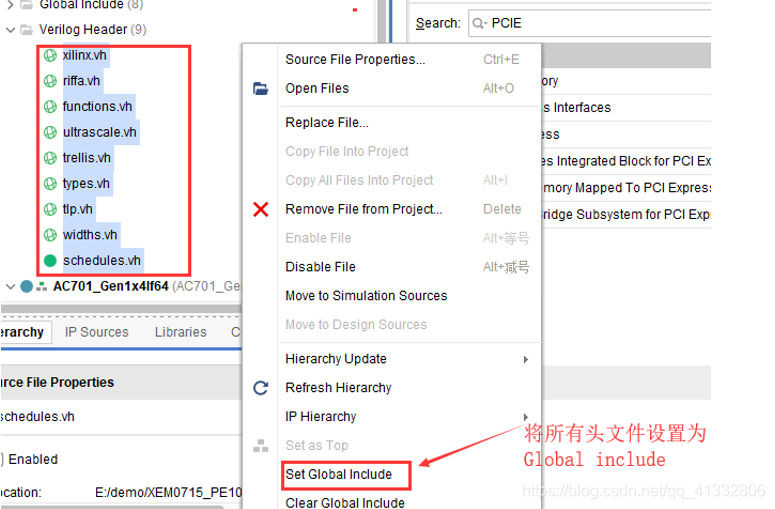

最后还需要将所引用到的头文件进行引用即可,完成本次Riffa框架的移植。

驱动安装

引脚分配完成,下载bit文件后会发现一个未识别设备。然后进行驱动的安装即可。

Riffa中有已经编译好的驱动,安装即可,在Win10操作系统下,需要对驱动的兼容性进行修改。

最后就可以识别设备啦!!!!!

对PCIE进行简单的测试,测测应力什么的,还是可以跑起来的。

一个Lane带宽比较低,多个Lane的话,效率会明显提升。

参考:

V3学院尤老师

</article>

412

412

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?