1. 简介

DDS(direct digital synthesizer),直接数字合成器,实现快速频率切换,容易实现频率、相位、幅度的数控调制。DDS在通信领域应用尤为广泛。

2.DDS原理

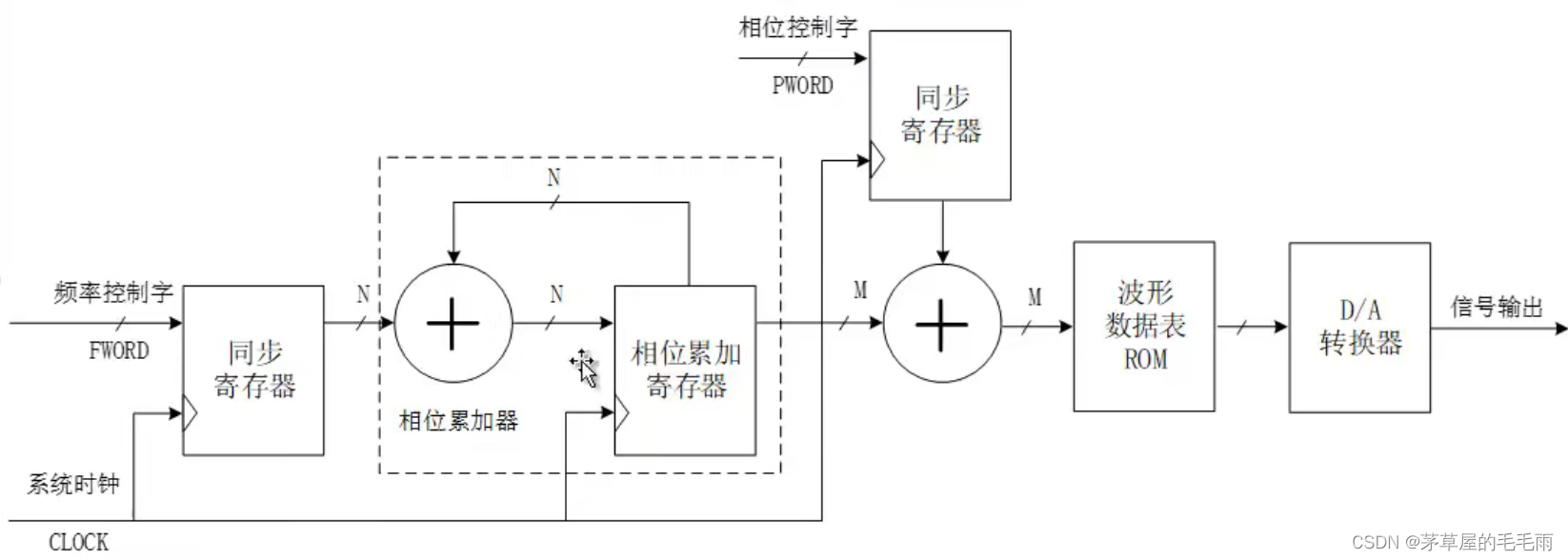

图2.1 基本DDS结构

基本公式:

是输出信号频率,

是相位增量,

为时钟频率,N是相位累加器的数据位宽,也是频率输入字的数据位宽。

下面采用更形象的方式理解这个公式。

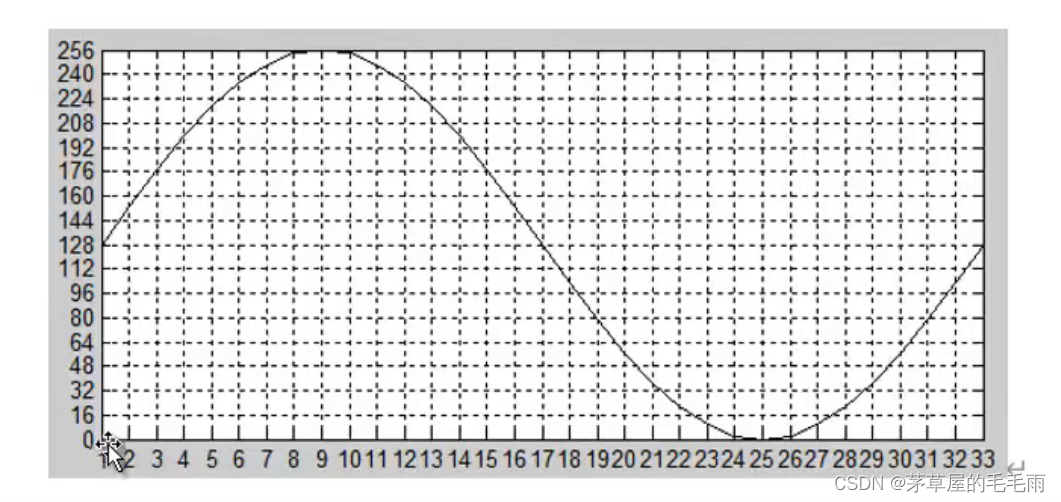

图2.1 32个采样点的正弦波形

假设=1

,即

=1000

(1)若取点间隔为1,输出频率?

要输出整个正弦波需要32ms(),则

(2)若取点间隔为2,输出频率?

,则

(3)若取点间隔为0.5(同一个值取样两次),输出频率?

,则

由上面分析和规律,清晰得到基本公式。

又称频率控制字(在上述形象的分析中,为取点间隔,也就是增量),也是相位增量。只要对相位的量化值进行简单的累加运算,就可以得到正弦信号当前的相位值。相位累加器是整个DDS的核心。在图2.1中,频率控制字输入还经过了一组同步寄存器(将频率控制字延迟一拍),使得频率控制字改变时不会干扰相位累加器正常工作。

波形数据表ROM完成相位-幅度的转换,图2.1中相位累加寄存器和相位控制字相加后作为ROM的地址。

3.Verilog代码

module DDS_Module(

Clk,

Reset_n,

Fword,//频率控制字

Pword,//相位控制字

Data

);

input Clk;

input Reset_n;

input [31:0]Fword;

input [11:0]Pword;

output [13:0]Data;

//频率控制字同步寄存器

reg [31:0]Fword_r;

always@(posedge Clk )

begin

Fword_r <= Fword;

end

//

//相位控制字同步寄存器

reg [11:0]Pword_r;

always@(posedge Clk )

begin

Pword_r <= Pword;

end

//

//相位累加器

reg [31:0]Freq_ACC;

always@(posedge Clk or negedge Reset_n)

begin

if(!Reset_n)

Freq_ACC <= 0;

else

Freq_ACC <= Fword_r + Freq_ACC;

end

/

//波形数据表地址

wire [11:0]Rom_Addr;

assign Rom_Addr = Freq_ACC[31:20] + Pword_r;

rom rom_inst1(

.clka(Clk),

.addra(Rom_Addr),

.douta(Data)

);

endmodule注意:相位累加器的高12位与相位控制字(Pword)相加作为ROM的地址。

rom数据宽度为14位,深度为4096(12位),用来存放正弦波数据。

4.testbench

`timescale 1ns / 1ps

module DDS_Module_tb(

);

reg Clk;

reg Reset_n;

reg [31:0]FwordA,FwordB ;

reg [11:0]PwordA,PwordB;

wire [13:0]DataA,DataB;

DDS_Module DDS_Module_inst0(

Clk,

Reset_n,

FwordA,//频率控制字

PwordA,//相位控制字

DataA

);

DDS_Module DDS_Module_inst1(

Clk,

Reset_n,

FwordB,//频率控制字

PwordB,//相位控制字

DataB

);

initial Clk = 1;

always #10 Clk = ~Clk;

initial begin

Reset_n = 0;

FwordA = 65536;

PwordA = 0;

FwordB = 65536;

PwordB = 1024;

#201;

Reset_n = 1;

#5000000;

FwordA = 65536 * 1024;

FwordB = 65536 * 1024;

PwordA = 0;

PwordB = 2048;

#1000000;

$stop;

end

endmodule

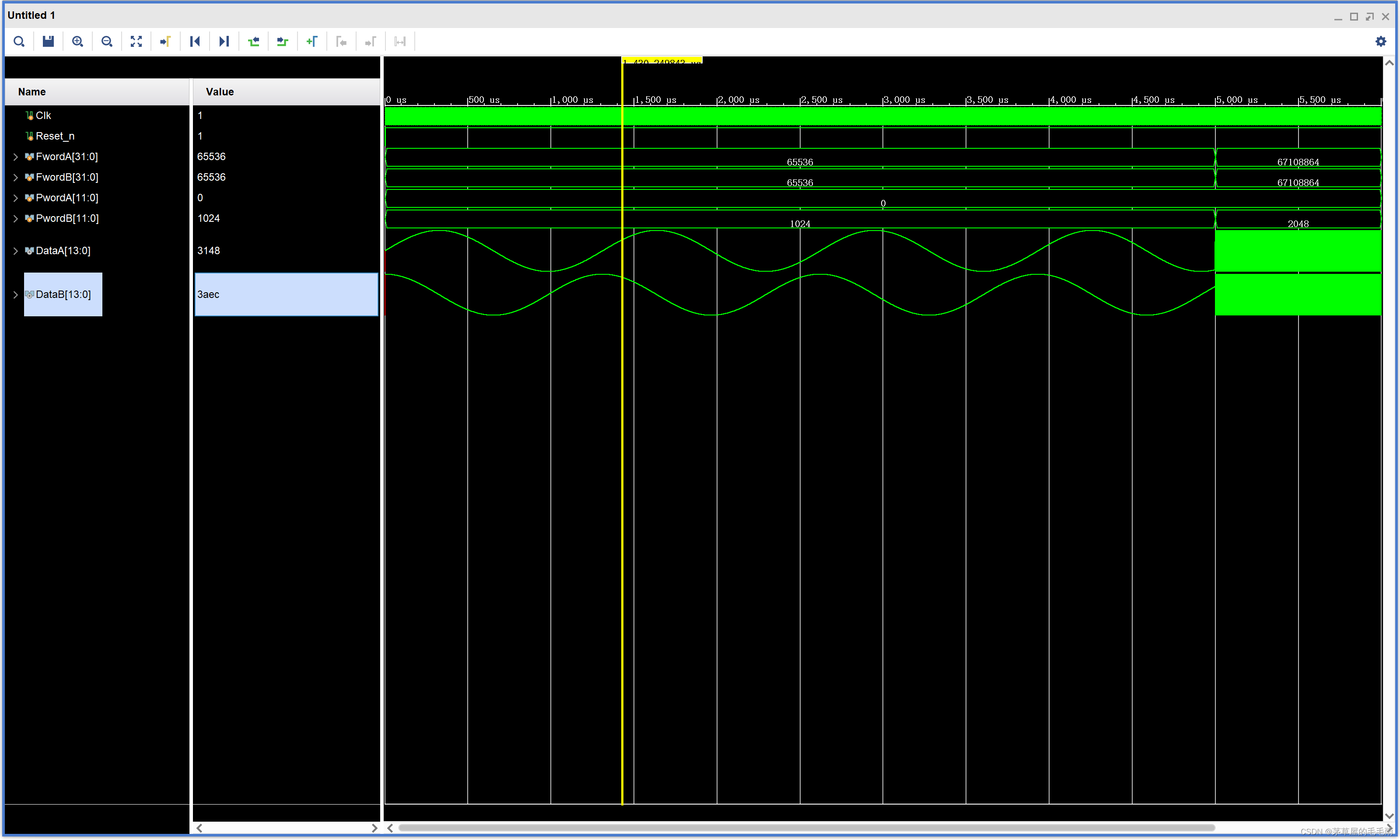

5.仿真波形、

输出频率验证:测量仿真正弦波的周期,计算输出频率;与用公式计算出的输出频率比较。若相等,则设计正确。

输出相位验证:ROM深度为4096,图中PwordB=1024,理论上DataB的相位为90度。从图中可以看出DataB的相位确实为90度,所以设计正确。

985

985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?