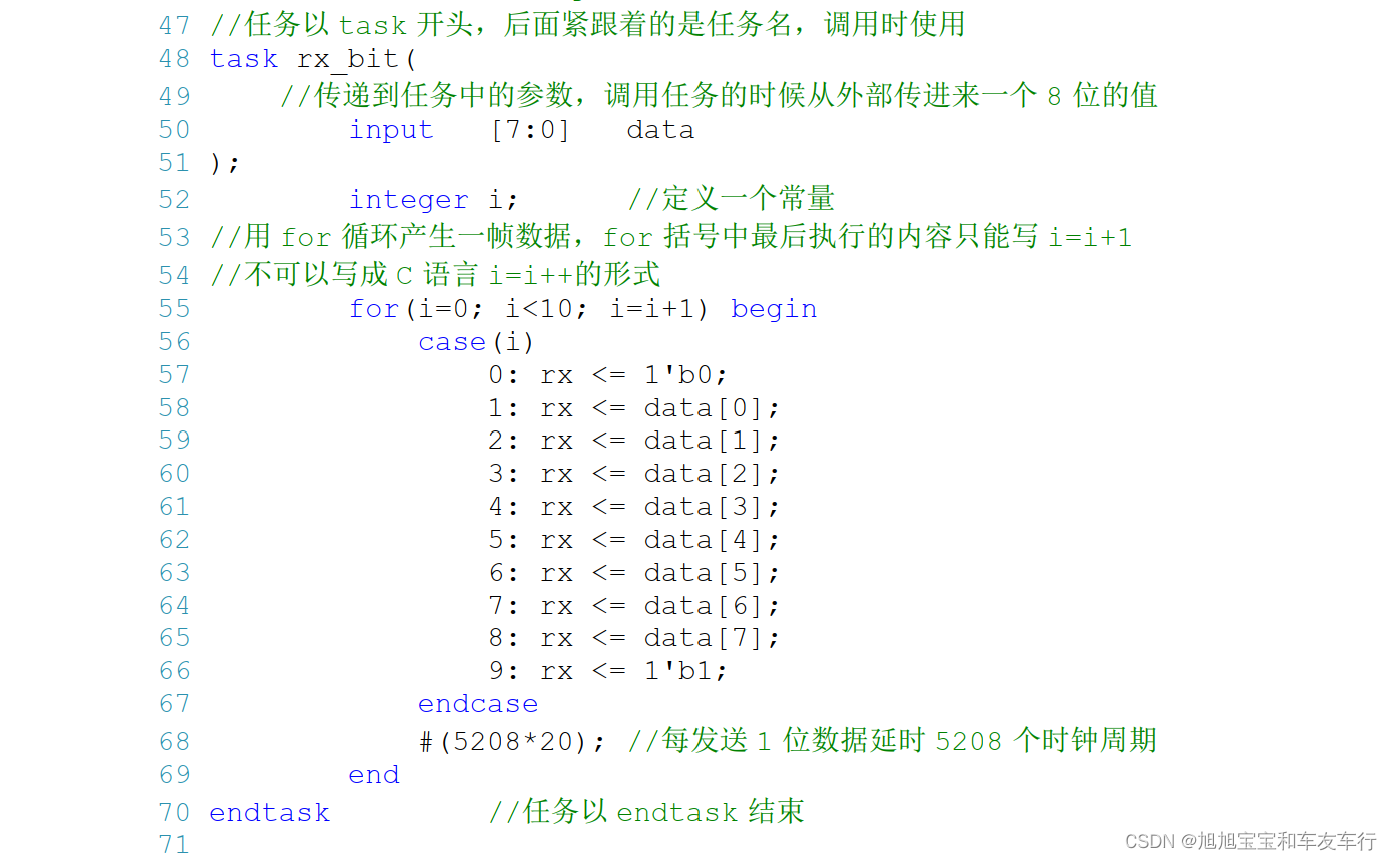

for语句在Verilog 中一般不在可综合代码中使用,因为for循环会被综合器展开为所有变量情况的执行语句 ,每个变量独立占用寄存器资源,每条执行语并不能有效地复用硬件逻辑资源,造成巨大的资源浪费。 简单的说就是:for语句循环几次,就是将相同的电路复制几次,因此循环次数越多,占用面积越大, 综合就越慢。for语句的一般 使用 情况: 在testbench中 使用 ,往往用于激励信号的生成。看如下图所示例子,该例子是野火rs232接口教程中采用for语句来产生测试激励的数据。

先定义一个常量i integer i

采用for语句产生一帧数据,结构清晰;

for循环的主要功能用于赋值和延迟两个功能

赋值

module count(

input i_clk,

input i_rst,

output reg[9:0]o_count1,

output reg[9:0]o_count2,

output reg[9:0]o_count3

);

reg[7:0]tmps;

integer i;

reg[7:0]men_delay[16:1]; //定义二维数组men_delay

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

tmps<=8'd0;

for(i=1;i<=16;i=i+1)begin

men_delay[i]<=8'd0;

end

end

else begin

tmps<=tmps+8'd1;

for(i=1;i<=16;i=i+1) begin

men_delay[i]<=tmps;

end

end

end

endmodule

写好仿真后

通过integer i;定义一个for循环的计数器变量,

而对于变量,则通过reg[7:0]men_delay[16:1];这种方式来定义,即定义16个数组,其位宽为8。

通过仿真可以看到,每一次时钟周期,通过for循环,可以实现16个变量的赋值

延迟

module count(

input i_clk,

input i_rst,

input [7:0]din,

output [7:0]dout

);

integer i;

reg[7:0]men_delay[256:1];

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

for(i=1;i<=256;i=i+1)

begin

men_delay[i]<=8'd0;

end

end

else begin

men_delay[1]<=din;

for(i=2;i<=256;i=i+1)

begin

men_delay[i]<=men_delay[i-1];

end

end

end

assign dout= men_delay[200];

endmodule

输入的数据din为八位位宽,

reg[7:0]men_delay[256:1];定义256个数组,位宽为8

在每个时钟上升沿 men_delay[i]<=men_delay[i-1] 相当于把din延迟一拍,最后 assign out= men_delay[200],相当于延时200个周期;

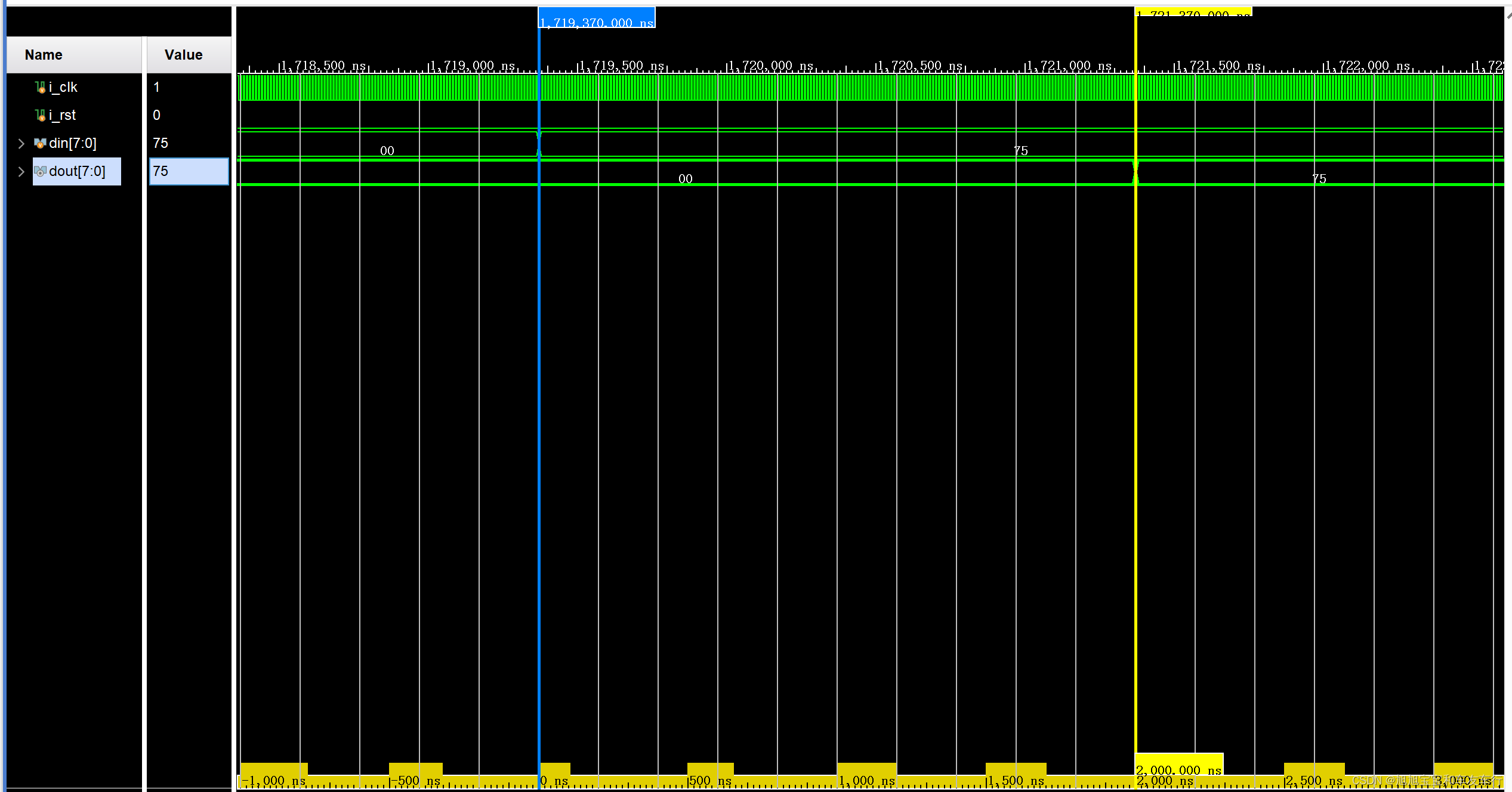

编写测试文件仿真如下

当din发生改变时,一个周期10ns 发生了200个周期的延迟,因此2000ns之后dout才发生改变;

857

857

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?