UVM phase机制

Phase机制在基于UVM的仿真中尤其重要,它是整个仿真周期中的同步机制。每个环境组件(uvm_component)在仿真中都会执行一组预定义的仿真阶段,而且默认情况下,只有在所有组件都执行完了当前仿真阶段的任务,才可以进入到下一个仿真阶段。phase的引入很大程度上解决了因代码顺序混乱造成的一些问题。

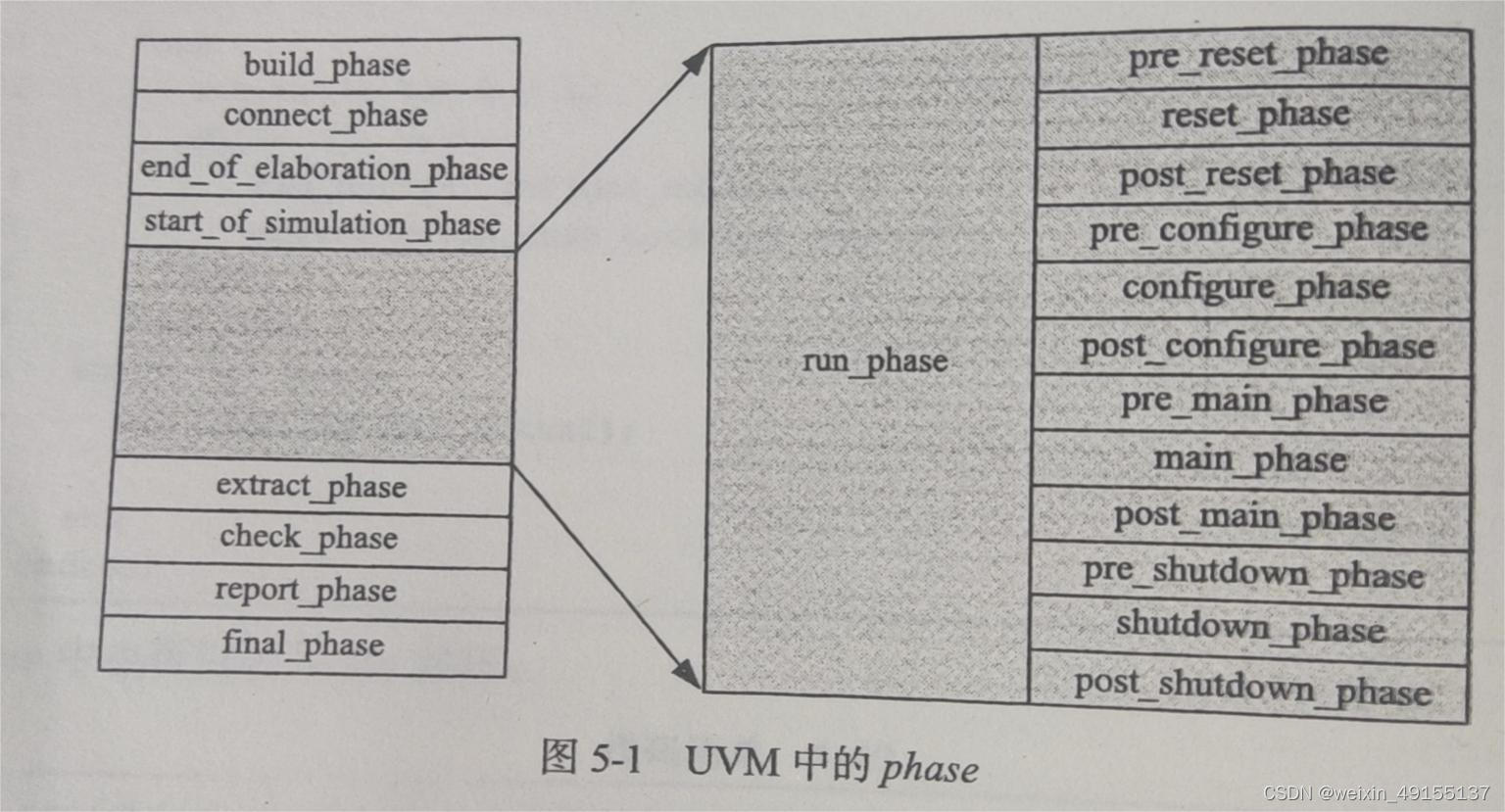

UVM 中的phase,按照其是否消耗仿真时间($time 打印出的时间)的特性,可以分成两大类,一类是function phase,如 build phase、connect phase 等,这些 phase 都不耗费真时间,通过函数来实现;另外一类是 task phase,如run phase 等,它们耗费仿真时间通过任务来实现。给 DUT 施加激励、监测 DUT 的输出都是在这些 phase 中完成的。

灰色背景的是消耗时间的task phase ,其他是function phase。每组Phases又分别包含了多个具体的Phase,每一个Phase都有自己预定义的功能,在下图中被详细列出。

图片引用 SystemVerilog | UVM | Phase机制基础 - 知乎 (zhihu.com)

build_phase和finall_phase是自上而下执行,假如UVM 不使用自上而下的方式执行 build phase,那会是什么情况呢? UVM的设哲学就是在 build_phase 中做实例化的工作,driver 和 monitor 都是 agent 的成员变量、所以它们的实例化都要在 agent 的 build_phase 中执行。如果在 agen 的 build phase 之前执行driver的 build_phase,此时 driver 还根本没有实例化,所以调用 driver.build phase 只会引

发错误。

UVM 是在 build_phase 中做实例化工作,这里的实例化指的是uvm component 及其派生类变量的实例化,假如在其他 phase 实例化一个 uvm_component,那么系统会报错。如果是uvm_object 的实例化,则可以在任何 phase 完成,当然也包括 build phase了。

除了自上而下的执行方式外,UVM 的phase 还有一种执行方式是自下而上。事实上除了build_phase 之外,所有不耗费仿真时间的phase(即function phase) 都是自下而上执行的。如对于 connect_phase 即先执行 driver和 monitor 的 connect phase,再执行 agent 的connect phase。

无论是自上而下还是自下而上,都只适应于UVM 树中有直系关系的 component。对于同一层次的、具有兄弟关系的 component,如 driver 与 monitor,它们的执行顺序如何呢?

执行顺序是按照字典序的, 这里的字典序的排序依据 new 时指定的名字。假如monitor 在 new 时指定的名字为 aaaIdriver的名字为 bbb,那么将会先执行 monitor的 build phase。反之若 monitor为mon,driver为 drv,那么将会先执行 driver 的 build phase。

UVM 树的遍历

除了兄弟关系的 component,还有一种叔侄关系的 component,如my.coreboard 与 my_driver,从树的层次结构上来说,scoreboard级别是高于 driver的,但是这两者 build_phase 的执行顺序其实也是不确定的。这两者的执行顺序除了上节提到的字典序外,还用到了图论中树的遍历方式: 广度优先或是深度优先。

所谓广度优先,指的是如果 i_agt 的 build_phase 执行完毕后,接下来执行的是其兄弟component 的 build_phase,当所有兄弟的 build_phase 执行完毕后,再执行其孩子的 build phase.

所谓深度优先,指的是如果 i_agt 的 build phase 执行完毕后,它接下来执行的是其孩子的 build_phase,如果孩子还有孩子,那么再继续执行下去,一直到整棵以 i_agt 为树根的UVM 子树的 build_phase 执行完毕,之后再执行i_agt 的兄弟的 build phase。

UVM 中采用的是深度优先的原则,对于scoreboard 及 driver 的 build phase的执行顺序,i_agt实例化时名字为“i_agt”,而scb为“scb”,那么i_agt的 build phase先执行,在执行完毕后,接下来执行 driver、monitor 及sequencer 的 build phase。当全部执行完毕后再执行 scoreboard 的 build phase.

super.phase

对于 build phase来说,uvm component 对其做的最重要的事情就是 自动获取通过 config db::set 设置的参数。如果要关掉这个功能,可以在自己的 build_phase中不调用super.build phase。

phase跳转

@(nengedge vif.rest_n);

phase.jump(uvm_reset_phase::get());

检测到rest_n为低跳转到reset_phase.

7097

7097

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?