一.简介

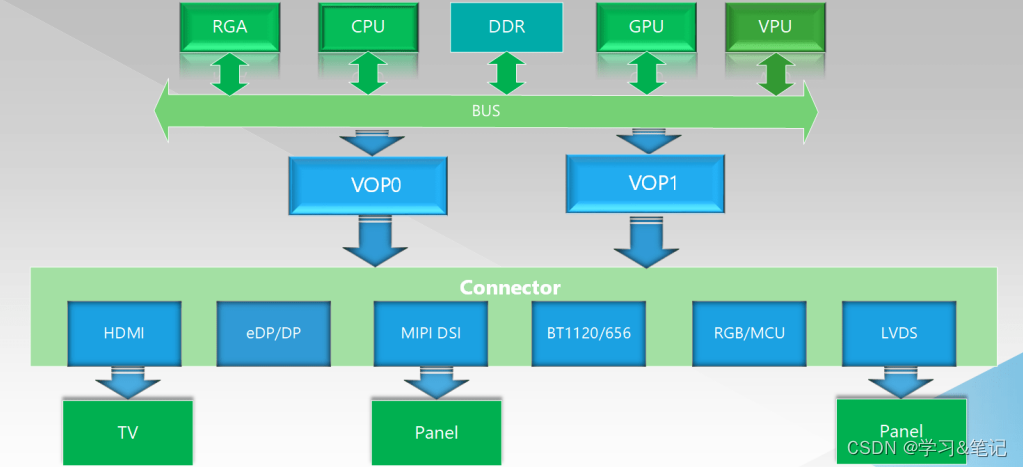

显示子系统是 Rockchip 平台显示输出相关软硬件系统的统称,它包括 VOP(比较老的平台叫 LCDC,比如 RK3188、RK3066)和 RGB、BT1120、BT656、I8080(MCU 显示接口),LVDS、MIPI DSI、EDP、DP、HDMI 等显示信号输 出模块以及与之对应的软件驱动。

从上面的 DSS 框图可以看到,在整个显示通路的最后端,是由 RGA,GPU、VPU 组成的显示图形加速模块,他们是专 门针对图像处理优化设计的硬件 IP,能够高效的进行图像的生成和进一步处理(比如 GPU 通过 opengl 功能提供图像 渲染功能,RGA 可以对图像数据进行缩放,旋转,合成等 2D 处理,VPU 可以高效的进行视频解码),从而减轻 CPU

负担。 经过这些图像加速模块处理后的数据会存放在 DDR 中,然后由 VOP 读取,根据应用需求进行 Alpha 叠加,颜色空间 转换,gamma 矫正,HDR 转换 等处理后,再发送到对应的显示接口模块(HDMI/DP/DSI/RG

订阅专栏 解锁全文

订阅专栏 解锁全文

2978

2978

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?