1. 简介

ACE是AXI Coherency Extensions的缩写。顾名思义,ACE就是AXI加上支持一致性的扩展。ACE协议提供了系统级一致性框架。一个有着硬件一致性缓存的处理器,既可以主动发起(initiating)一系列的一致性事务,也必须监听其它处理器发出的一致性事务。

开始之前,先看几个基本概念:

- Caching master:指的是具有硬件一致性缓存的处理器单元。这个处理器有一个snoop地址通道和一个snoop响应通道,还可以选择带一个snoop数据通道。这里插一句,这三个通道是ACE协议比AXI协议多出来的,后面会讲。

- Initiating master:发起主机,指的是可以发出一个事务以启动后续一系列事件的单元。

- Snooped master:被监听主机,指的是可以接收snoop事务的处理器单元。

ACE协议实现通过以下扩展支持Barrier传输和DVM(Distributed Virtual Memory)

1、五个状态缓存模型,指明了Cache line的状态,决定接口可以执行哪些操作

2、扩展了AXI4接口信号,提供了新的传输类型

3、扩展了Cache Master与其他Master交互的通道,以便共享数据

一致性互联系统,即多个具有Cache的Master通过内部互联器件管理来访问主存。

2. cache line 5种状态

缓存一致性(cache coherency)要解决的是空间上的问题,也就是说,如果多个处理器同时缓存了主存(main memory)的同一段数据,那么这些处理器之间必须要保证数据的一致,如果某个处理器改动了数据,就要通知其它处理器知晓,否则会引起应用程序运行不一致。对此,ACE协议要求,如果cache中的一个缓存行(cache line)是整个系统中的唯一拷贝,那么拥有这个缓存行的处理器单元可以修改数据,同时不必通知其它主机;如果这个缓存行数据在整个系统中存在其它拷贝(副本),则拥有这个缓存行的处理器在修改数据的同时,必须通知其它处理器知晓这个改动。所以,对于缓存行来说,记录其当前状态至关重要。为此,在ACE里面提出了一个五种状态的缓存模型(cache state model)。

- Invalid:简称I,表示该缓存行无效

- UniqueClean:简称UC,表示缓存行是唯一的,并且数据未被修改

- UniqueDirty:简称UD,表示缓存行是唯一的,但是数据被修改过,拥有该缓存行的主机必须保证修改后的数据要写回到主存

- SharedClean:简称SC,缓存行可能存在其它拷贝,但该缓存行数据没有被修改过

- SharedDirty:简称SD,缓存行可能存在其它拷贝,但该缓存行数据被修改过

3. ACE相对AXI4变动

3.1 ACE对AXI4通道信号的扩展

对读写地址通道和读数据通道进行了扩展,对写数据和写应答通道未进行扩展:

3.2 ACE自身扩展的通道

snoop address(AC):cache主端提供snoop传输的地址和控制信息

snoop response(CR):cache主端提供snoop传输的响应

snoop data(CD):可选的主端传递数据通道。通常发送在主端snooped时复制返回的有效数据(读事务和clean snoop)

ACE额外使用RACK和WACK通知完成读写事务

4. ACE读写操作流程

4.1 从共享地址加载数据操作流程

1、主端在读地址通道发起读事务

2、interconnect查询是否在其他Cache保存有此地址的cache line存在

3、 1)如果存在

-----在CR通道响应

-----在interconnect上提供数据,在CD通道提供数据

2)不存在

-----在interconnect上发起主存传输事务,由当前的主端发起事务效率较高

-----在AXI读数据通道(RD)上返回数据,为AXI标准的读事务

4、主端器件使用RACK信号响应读完成

注:1、如果发起主端或被snooped的cache都不负责将dirty line写入主存则interconnect负责在读取的同时将数据写进主存

2、在这种情况下interconnect负责产生传输地址和从snooped的数据写进主存

4.2 向共享地址store数据操作流程

写入分为四种情况:

1、写入partial cache line

2、写入entire cache line

3、写入已经cache的数据

4、重复写入Overlapping store

4.2.1 写入partial cache line

注: 主端存储前必须获得当前cache line的拷贝

1、主端获得cache line预存储形式,并且通过在RA通道上发起RU(ReadUnique)事务删除其他cache拷贝

2、interconnect在AC通道上传输给其他cache

3、snooped cache使用CR通道响应interconnect的传输,并使用CR通道返回数据

4、interconnect 使用RD通道响应响应最初的主端

-----如果没有snooped则interconnect 读取主存,然后响应主端-----

5、主端器件执行存储,并使用RACK信号指示传输已完成。

-----如果cache line是unique的,不需要广播给其他cache进行snoop-----

4.2.2 写入entire cache line

注:存储前不需要获得数据

1、主端在RA通道上发起(Make Unique)事务获得cache line拷贝,这将移除其他的cache line拷贝

2、interconnect在AC通道上将事务传递给其他cache

3、snooped cache 在CR通道上响应表明copy已经被删除

4、interconnect使用RD通道响应主端已完成

-----只有响应,不传递数据-----

5、主端使用RACK信号表明传输完成

4.2.3 写入已经cache的数据

注:主端已经获得cache line

1、主端在RA通道上发起(Clean Unique)事务获得cache line拷贝,这将移除其他的cache line拷贝并且将dirty写入主存

-----cache line不必返回给主端-----

2、interconnect在AC通道上将事务传递给其他cache。snooped cache使用CR通道响应表明copy已经被删除,interconnect是否需要将dirty写入主存

4、interconnect使用RD通道响应主端已完成

-----只有响应,不传递数据-----

5、主端使用RACK信号表明传输完成

4.2.4 重复写入Overlapping store

注:两个主端存储同一个line,interconnect决定传输顺序

1、主端1执行正常一~三的store流程

2、主端2使用snoop port获取主端1的操作

1)如果主端2请求数据,需要等到1操作完成,能够进行主端2操作的时候

2)如果主端2在进行full cache line存储,当2检测到1的存储操作后删除数据的拷贝。当主端2的oberserve完成后可以继续进行2的store操作

3)如果主端2存储partial cache line,且已经有数据的copy,当2 observes到1的store操作,2必须移除copy,且必须进行以下操作

-----主端2必须重新组织一个数据请求操作,然后重新完成store-----

-----主端2可以将partial cache line写入主存,但不保留数据的copy,在后续重新获取这个cache line时需要重新取数据-----

5. ACE事务类型

5.1 Non-snooping transactions

不会引起snoop transaction,访问的地址可以是Non-shareable/Device 具体可以分为Read No Snoop和Write No Snoop。

5.2 Coherent transactions

5.2.1 从共享地址加载数据

1)Read Clean:只接受clean cache line,如果master没有接受dirty cache的能力或使用write-through cache.时使用

2)Read Not Shared Dirty:只接受clean(unique/shared),unique dirty的cache

3)Read Shared:接受任意line

5.2.2 向共享地址store数据

1)Read Unique:在partial cache line的store操作中,没有copy的cache line存在,获得cache line的copy,并且保证没有其他copy存在

2)Clean Unique:在partial cache line的store操作中,有copy的cache line存在,获得cache line的copy,并将dirty cache写入main memory, 并保证没有其他copy cache line存在。

3)Make Unique:进行full cache line的store,invalid其他的copy的cache line

5.2.3 向共享地址store数据但不需要copy

1)Read Once:得到一份cache data 的snapshot但是原Unique cache不需要从Unique变为Shared

2)Write Unique: 在write transaction之前移除所有的cache copy,在该命令之前必须保证dirty data已经都被写入memory(full or partial cache line)

3)Write Line Unique:与2)相同但只能用于full cache line

-----Read Once和Write Unique不需要full line size,Write Line Unique需要----

5.3 Memory update transactions

1)Write Back:将cache line写入主存,来释放位置,不能保留此line的copy

2)Write Clean:将cache line写入主存,来释放位置,允许保留此line的copy

3)Evict:指示此cache line地址被排除,且不需要写入主存。用于特定被跟踪的器件cache line也可用来建立snoop 过滤器,在Evict中不传输数据

5.4 Cache maintenance transactions

主端器件广播此事务访问和维持系统中其他主端的cache。并且此操作能够让主端器件查看加载和存储操作对那些无法访问的系统缓存的影响,此操作叫作Software Cache Maintenance.且Cache maintenance transactions可传播到下游缓存,允许维护系统中所有缓存

-----主端初始化其他缓存时也对本地缓存进行操作----

1)Clean Shared:清空其他cache,如果有dirty line必须写入主存,snooped 本地cache可以保留cache line的copy

2)Clean Invalid: 清空并invalid 其他cache。如果有dirty line必须写入主存,然后将clean和dirty的所有line 全部删除

3)Make Invalid: 清空并invalid 其他cache,dirty不写入主存。

5.5 Snoop transactions

通过snoop的三个channel来进行操作,是coherency和maintenance transaction的子集。

5.6 Barrier transactions

保证系统中的order和observation

memory barrier:保证在barrier之后domain中的另一个master能够观察到所有的transaction

synchronization barrier:保证在该barrier transaction之前所有的transaction都必须被某个domain内的master观察到。有些synchronization barrier需要在barrier transaction到达从端之前所有事务都已经被组织好。

5.7 Distributed virtual memory transactions

用于维护虚拟内存地址,用于两个具有虚拟内存地址的器件之间消息传递。

典型的DVM操作

1、主端在虚地址空间发起事务

2、SMMU接收虚地址转换为物理地址

----- 如果SMMU最近执行过此虚地址,则从他的TLB中直接获得翻译------

----- 否则SMMU遍历转换表进行转换-----

3、SMMU使用物理地址为主端组织事务

6. Trasnaction的处理过程

1)intial master发起一个transaction

2)根据address decode直接到slave,(不需要coherency支持)交给interconnect中的coherency支持模块。

3):coherency transaction与其他master的transaction的顺序控制,order

4):interconnect发出必要的snoop transaction

5):每个cache master收到snoop transaction,并提供响应,有些操作提供data

6):interconnect决定是否需要访问主存

7):interconenct得到snoop响应和data

8):initial master完成transaction

7. ACE信号描述

7.1 RA和WA通道

7.1.1 AxDOMAIN[1:0]

AxDOMAIN[1:0]信号指明了cache 操作的domain:

Device事务中AxCACHE[1]=0,只能用系统级

Cacheable事务中AxCACHE[3:2]!=0,不能使用系统级

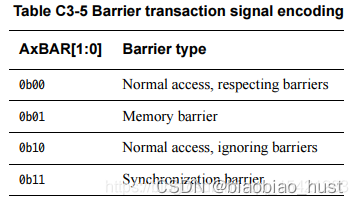

7.1.2 AxBAR[1:0]

AxBAR[1:0]指明了Barrier transaction。

7.1.3 ARSNOOP[3:0]和AWSNOOP[2:0]

7.1.4 cache line的大小限制

最小值为以下值中的较大者:

•16个字节

•数据总线的宽度(单位为byte)

最大值为以下值中的较小的:

•2048字节

•最大突发长度16×数据总线的宽度(单位为byte)例如:bus width 1024 maximum = 1024/8×16

7.1.5 其他信号

1、AxLEN必须为1、2、4、8、16**

2、AxSIZE必须等于总线位宽

3、AxBURST:

1)INCR地址必须对齐cache line size=AxLEN×AxSIZE

2)WRAP地址必须对齐AxSIZE

3)不支持fixed

4、AxDOMAIN

1)除CleanShared、CleanInvalid、MakeInvalid外域必须为Inner Shareable 或 Outer Shareable

2)CleanShared、CleanInvalid、MakeInvalid的域必须为Non-shareable、 Inner Shareable 或 Outer Shareable.

5、AxBAR

必须为normal access

6、AxCACHE

必须为Modifiable.

7、AxLOCK

1)如果事务为ReadNotSharedDirty, ReadUnique,

MakeUnique, CleanShared, CleanInvalid, MakeInvalid,

WriteLineUnique 或Evict. 必须为0

2)如果为ReadClean, ReadShared, 或CleanUnique.0或1都可以

8、WriteLineUnique事务要求所有write data strobe置位

9、以下事务要求AxLEN为正确的cache line size,即使并未传递数据

CleanUnique、MakeUnique、CleanShared、CleanInvalid、MakeInvalid、Evict.

ReadOnce和 WriteUnique transactions

1、AxDOMAIN必须为Inner Shareable或Outer Shareable

2、AxBURST必须为INCR 或 WRAP

3、AxCACHE必须为Modifiable.

4、AxLOCK必须为normal access

WriteBack and WriteClean transactions

1、AWBURST

1)WRAP地址必须对齐AxSIZE(总线位宽),burst length 必须为2, 4, 8 or 16。AWSIZE x AWLEN不能超过cache line size

2)INCR burst length必须小于16,最后一个字节为AWISZE对齐的首地址加AWSIZE x AWLEN。最后一字节必须与第一个字节位于同一个line中

2、AWDOMAIN必须为System

3、AWBAR必须为normal access

4、AxCACHE必须为Modifiable.

5、AxLOCK必须为normal access

Barrier transactions

1、AxADDR 必须为全0

2、AxBURST 必须为INCR

3、AxLEN 必须为全0

4、AxSIZE必须为总线位宽

5、AxCACHE必须为Normal, Non-cacheable.

6、AxLOCK必须为normal access

7、AxSNOOP必须为全0

7.2 RR(读响应)通道

RRESP[2]:为高时数据必须将数据写入主存

RRESP[3]:为高时表明其他cache中存在的copy必须保持Shared状态,为低时表明仅仅为cache的copy可以为Unique状态

当需要移除所有其他cache中的copy时RRESP[3]必须为低;

当不允许传递dirty时RRESP[2]必须为低;

当这两位不起作用时必须为低;

EXOKAY只有ReadNoSnoop, ReadClean, ReadShared或CleanUnique允许响应

7.3 RACK(读告知)通道

RACK信号在主端读完成后必须置位一个时钟周期,且依赖于RVALID/RREADY,就像RLAST信号,且不能被延迟

RACK必须发送到所有事务

RACK不含有顺序信息,顺序与last read和read response有关

RACK被interconnect用来保证主端的snoop port访问同一个地址的进程完成后才能发起事务

7.4 WR(写响应通道)通道

EXOKAY 只响应 WriteNoSnoop事务

7.5 WR(写告知)通道

WACK信号在主端写完成后必须置位一个时钟周期

WACK信号依赖于BVALID/BREADY

WACK必须发送到所有事务包括barrier transactions

WACK不含有顺序信息,顺序与write response有关

WACK被interconnect用来保证主端的snoop port访问同一个地址的进程完成后才能发起事务

7.6 AC(Snoop address)通道

ACVALID:为高时snoop address可用

ACREADY:为高时主端可接受snoop address信息

ACADDR[ac-1:0]:snoop address位宽必须与读写地址位宽保持一致。

ACSNOOP[3:0] :Snoop事务类型

ACPROT[2:0]:Snoop保护类型 ACPROT[1]可被定义两个地址空间:安全的和不安全的,也可以被定义为额外地址位防止地址混淆

7.7 CR(Snoop response)通道

CRVALID:表明Snoop response是有效的

CRREADY:表明Snoop response可在这个周期被接收

CRRESP[4:0]:表明Snoop response的类型

CRRESP[1]:为高时代表要提供full cache line data,为低时不需要。以下操作如果snoop导致了cache hit则需要传输数据 (如果line为clean的,虽然不一定需要传输数据,但推荐仍进行传输)

ReadOnce、ReadClean、ReadNotSharedDirty、ReadShared、ReadUnique.、当cache hit且dirty、CleanInvalid和CleanShared操作需要传输数据

CRRESP[1]:为高时代表snoop 的cache line发生了错误,需要系统支持错误修正,如果系统不支持则永久置低

CRRESP[2]:为高时需要将dirty数据写入主存

CRRESP[3]:为高时表明snoop完成后cache保留cache line的copy

CRRESP[4]:为高时表明snoop之前cache处于unique状态其他cache没有copy

7.8 CD(Snoop data)通道

CDVALID:snoop data有效

CDREADY:snoop data准备接收

CDDATA[cd-1:0]:snoop data

CDLAST:最后一次数据传输

CDDATA位宽不必要与读写数据位宽一致

snoop data位宽可以为32, 64, 128, 256, 512, 或1024,但要满足

• cache line size transactions must be a full data bus width

• the burst length must be 1, 2, 4, 8, or 16.

CD(Snoop data)通道是可选的,但cache 主端不能保有dirty数据,在获得dirty数据时必须首先把dirty数据写入主存。

7.9 snoop通道依赖关系

529

529

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?