1,新建工程

器件选xc7z010clg400-1

一路点yes进入主界面

2,设计输入

简介:设计输入是将所设计的系统或电路以开发软件要求的某种形式表示出来,

并输入给EDA工具的过程。常用的方法为硬件描述语言(HDL)和原理图输入方法等。

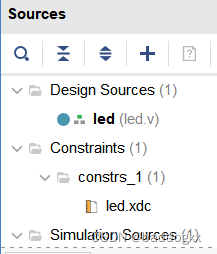

1,点击sources窗口的+号创建工程顶层文件

2,选第二个创建design sources

3.一路点yes 创建verilog源文件

4,编写verilog代码

3,分析与综合(Elaborated/Synthesis)

简介:将语言描述的电路逻辑转化成与门、或门、非门、触发器等基本逻辑单元的互连关系,又叫的门级网表。

比如四选一选择器,综合过程将Verilog代码翻译成了门级互连网表。综合就是RTL设计转换为门级表示,是由时序驱动和优化的。

利用Verilog 做电路设计时我们总是强调可综合的概念,可综合就是我们的这段代码可以被翻译成门级电路,

不可综合就是代码不能被翻译成与之对应的门级电路。

综合是创造性的转化过程,它能翻译电路,也能够优化电路,去除电路描述中冗余的电路结构和复用功能相同的电路结构。

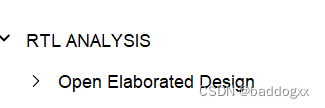

1,点击“Open Elaborated Design” 进行RTL源文件编译(分析)

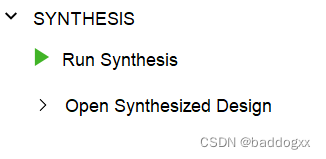

2,点击“Run Synthesis” 将RTL代码转化为门级网表(综合)

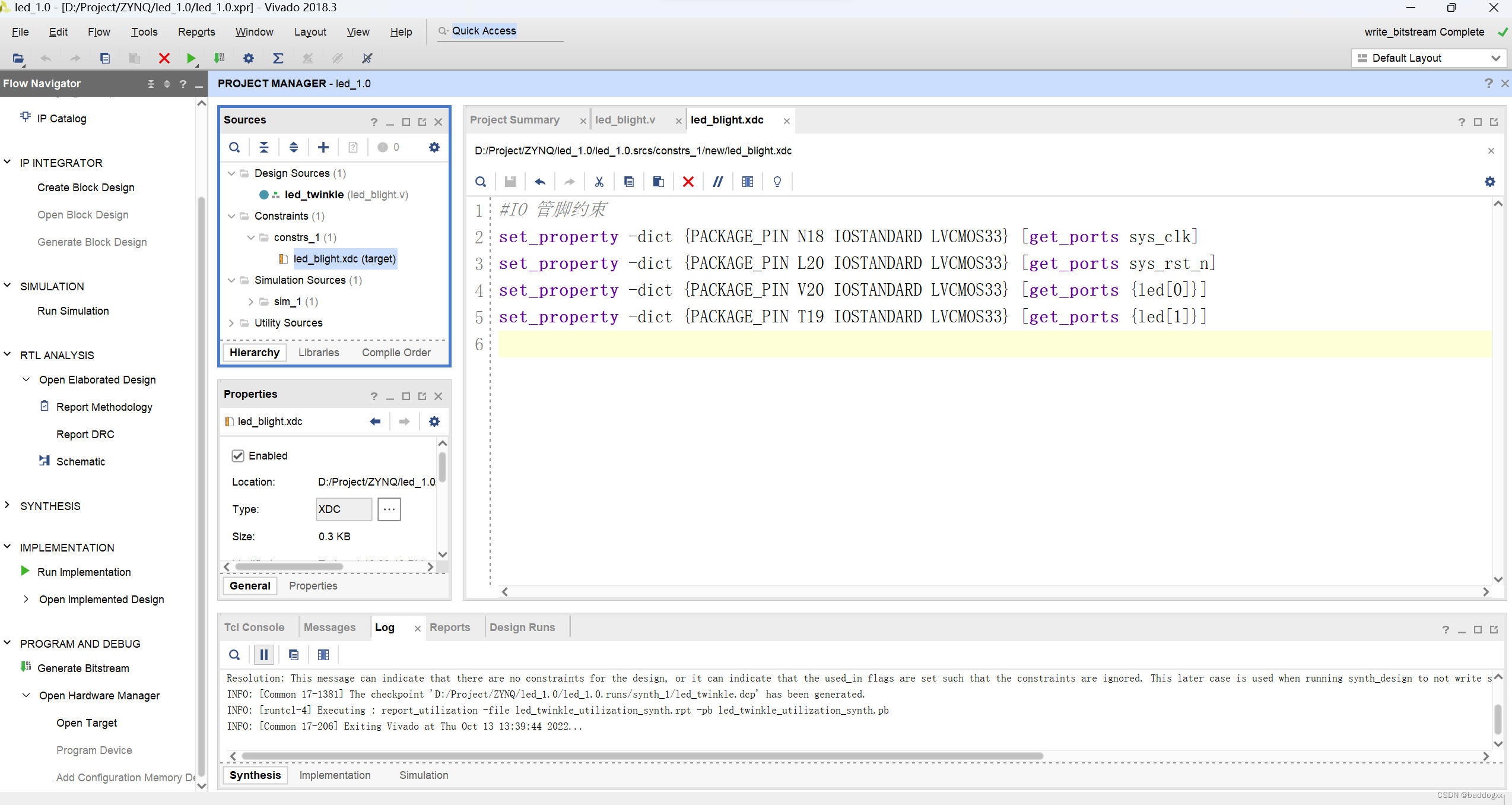

4,约束输入

第一种方法

1,创建约束文件

点击sources窗口的+号

这次选第一个添加或创建约束

一路点击ok

2,在.xdc文件中写入约束代码

第二种方法

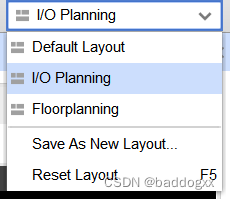

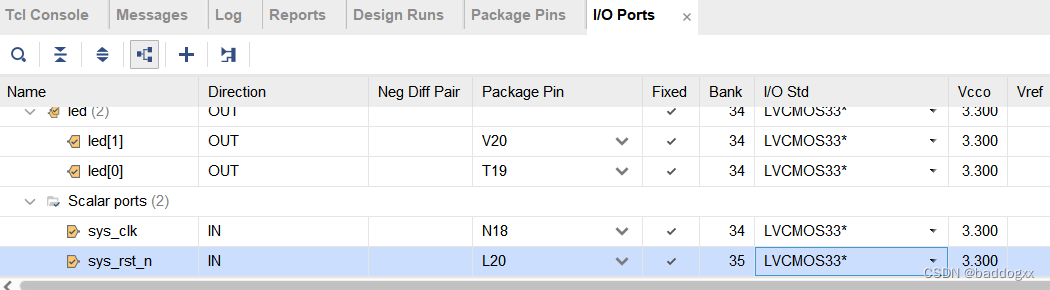

1,在打开分析窗口后点击右上角的“I/O Planning”,打开管脚分配页面

2,在下方区域中进行管脚分配

分配完成之后保存就得到与第一种方法一样的xdc文件

5,设计实现

简介:implementation是place和route的过程,也就是布局布线。作用是将综合生成的逻辑网表配置到具体的FPGA芯片上。

综合后生成的门级网表只是表示了门与门之间虚拟的连接关系,并没有规定每个门的位置以及连线的长度等。

布局布线就是一个将门级网表中的门的位置以及连线信息确定下来的过程。

1,点击左边窗口的Run Implementation就OK了

6,生成和下载比特流

简介:在下载程序之前,首先要先生成用于下载到器件中的比特流文件,该文件的后缀为“.bit”。

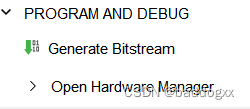

1,点击左边窗口的“Generate Bitstream”一路点ok就行了。

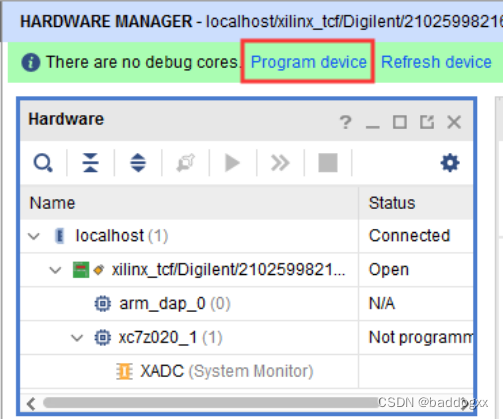

2,比特流生成完成后就点击下面的“Open Hardware Manager”

3,电脑连接下载器,板子上电

4,点击“open target”,点击“Auto Connect”

5,点击“Program Device”一路点击ok。

1279

1279

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?