最近看了一篇文章《可测试性设计(DFT):测试设计极限》,结合目前在Layout的板卡,学习消化一下其中的内容。

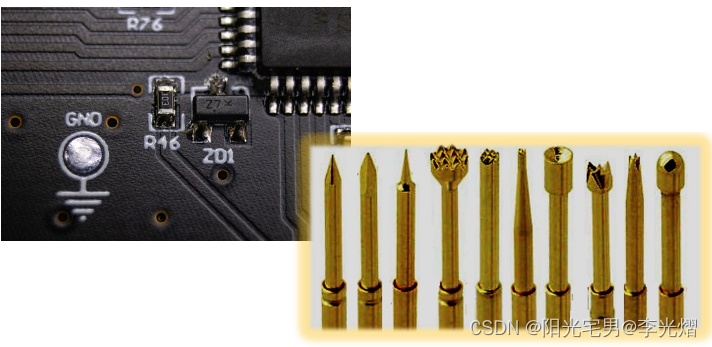

我们在生产中可能会看到一些测试点和测试探针,如下所示:

测试点是一个小小的金属端子,用作连接点来测试 PCBA 上的电路。它们的尺寸取决于诸多因素,包括工具精度、电路板尺寸、制造工艺以及探头形状和公差。

测试探针是安装在 ICT 夹具中的带有弹簧的针。

由测试点和探针整个装置构成了 PCB 和夹具之间的接口连接,用于收集数据并发现错误。

探针头和测试点的组合具有不同的形状、尺寸和长度,用于匹配它们所在的可用空间大小。探针头也有很多类型,用于连接焊盘以外的测试点;它们也可以是在布局中带有标记或标识的连接器或其他 PCBA 特征。

可测试性的重要性

对于设计工程师来说,设计一块 PCB 需要经过许多步骤(原理图网表导入、布局、布线、评审、反标等等),在评审过程中还可能需要数个版本的迭代,付出大量的时间和工作。

在这个过程中,确保PCB设计针对测试进行了优化往往会被忽视。然而,如果不能

本文探讨了可测试性设计(DFT)在PCB设计中的重要性,包括测试点和探针的作用,以及与制造供应商、电子工程师和测试工程师的合作。DFT能够确保在生产早期发现并解决问题,防止大规模返修。测试内容涵盖AOI、AXI和ICT,而良好的测试设计是大批量生产成功的关键。

本文探讨了可测试性设计(DFT)在PCB设计中的重要性,包括测试点和探针的作用,以及与制造供应商、电子工程师和测试工程师的合作。DFT能够确保在生产早期发现并解决问题,防止大规模返修。测试内容涵盖AOI、AXI和ICT,而良好的测试设计是大批量生产成功的关键。

订阅专栏 解锁全文

订阅专栏 解锁全文

2555

2555

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?