文章目录

背景

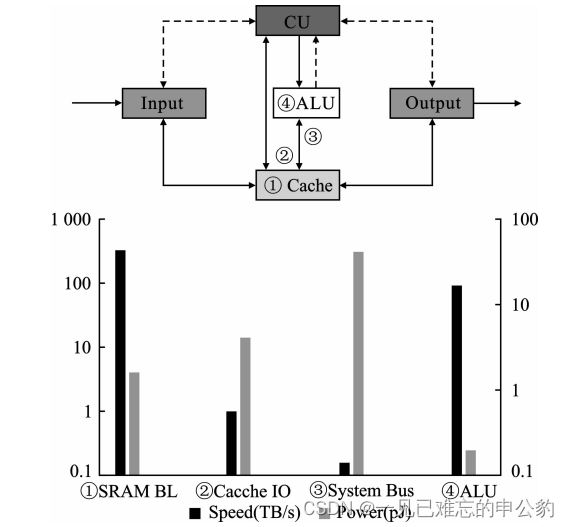

在处理数据密集型应用时,冯·诺伊曼架构面临严重的性能和能量消耗问题,主要因为处理器和存储器之间频繁传输大量数据。

为应对这一挑战,基于SRAM的存内计算技术被提出,通过将运算单元整合到内存中,实现即存即算的数据处理,彻底打破了冯·诺伊曼瓶颈。

冯·诺伊曼架构和冯·诺伊曼瓶颈如下图:

SRAM 存内计算技术

存内计算技术是一种新兴的存储器技术,它将存储单元和计算单元集成在同一个存储器芯片中,从而实现数据在存储和计算之间的直接传输,而不需要通过外部总线或处理器进行数据传输。这种技术可以大大提高数据处理的效率和能效,因此在人工智能、大数据处理等领域具有广泛的应用前景。SRAM(静态随机存取存储器)是一种常见的存内计算技术,它具有高速、低功耗、易扩展等优点,因此在存内计算领域得到了广泛的应用。本文将对SRAM存内计算技术进行综述,介绍其基本原理、技术实现、应用场景和未来发展方向。

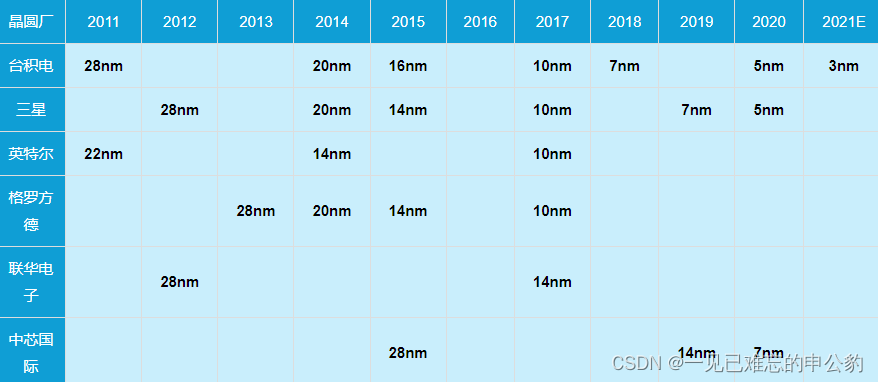

知存科技的WTM2101量产芯片采用40nm制程,将神经网络部署在芯片中,已经实现了满足端侧算力需求的语音识别等功能。即将量产的WTM8芯片,采用28nm制程,作为新一代存内AI计算视觉芯片,能够实现图像的AI超分、插帧、HDR识别和检测这样复杂的功能[8],现有的一些研究也已经证明存算一体可以实现16bit、32bit的浮点计算,具备进入高算力芯片的能力。

SRAM存内计算技术的核心思想是将存储单元和计算单元集成在一起,从而实现数据在存储和计算之间的直接传输。这种技术可以大大提高数据处理的效率和能效,因为数据不需要通过外部总线或处理器进行传输,从而减少了数据传输的延迟和功耗。此外,SRAM存内计算技术还可以实现更高的能效比,因为存储器和计算单元的集成可以减少电路的复杂性,从而降低功耗。

SRAM存内计算技术的实现方式有多种,其中最常见的是通过在传统的SRAM存储单元中集成计算逻辑来实现。这种实现方式可以在不增加额外的硬件开销的情况下实现高性能的计算能力。另一种实现方式是通过在SRAM存储器阵列中集成多个计算单元,从而实现更强大的计算能力。这种实现方式可以扩展到更大的规模,但需要更多的硬件资源。

SRAM存内计算技术的应用场景非常广泛,包括人工智能、大数据处理、图像处理、自然语言处理等领域。在人工智能领域,SRAM存内计算技术可以用于实现神经网络的存储和计算,从而提高神经网络的性能和能效。在大数据处理领域,SRAM存内计算技术可以用于实现高效的数据处理和分析,从而提高数据处理的速度和精度。在图像处理和自然语言处理领域,SRAM存内计算技术可以用于实现高效的特征提取和模型训练,从而提高图像和自然语言处理的性能和能效。

基于电压域的 SRAM 存内计算技术

基于电压域的SRAM存内计算技术是一种将计算和存储单元结合在一起的技术,它利用SRAM存储单元的电压变化来实现计算功能。这种技术可以显著提高处理速度,同时降低功耗和硬件成本。

在电压域上实现的 SRAM 存内计算技术,通常先使用 DAC 单元将数字量先转化为线性的电压值,然后利用电荷共享的方式实现计算,最后再用ADC 单元将模拟的计算结果转换为相应的数字信号.通过将数据量转换成电压值的方式实现多位算法,简单易行,也是当下存内计算的最主要实现形式.如果按计算模块和存储模块之间的距离划分。

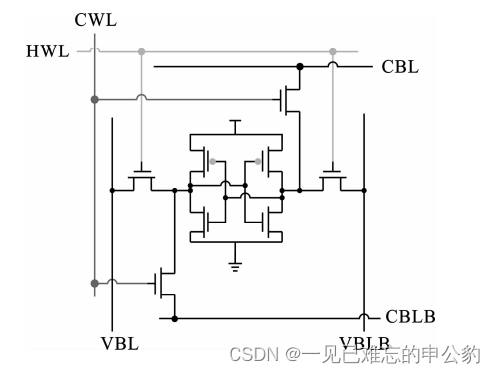

位串性技术的8TSRAM 通用近内存计算

- 基于位串性技术的 8TSRAM 通用近内存计算。Wang 等人提出了一种混合近内存计算阵列,可用于需要高能效、高灵活性和高可编程性的般用途的应用。架构如下图:

在传统的处理器中,数据需要在存储器和处理器之间不断传输,这不仅增加了数据传输的延迟,还增加了功耗。而基于电压域的SRAM存内计算技术可以将存储单元和计算单元集成在一起,实现数据在存储和计算之间的直接传输,从而避免了数据传输的延迟和功耗。

基于电压域的SRAM存内计算技术的实现方式是利用SRAM存储单元的电压变化来模拟逻辑门的输入和输出。通过对SRAM存储单元的电压进行读取、转换和写入操作,可以实现各种逻辑运算,从而完成计算任务。这种技术可以实现在单个SRAM存储单元中完成多个逻辑运算,提高了计算速度和能效。

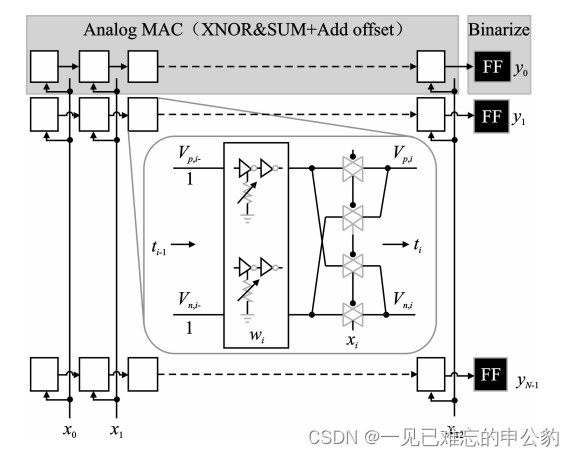

脉冲宽度调制8T-RAM 存内计算

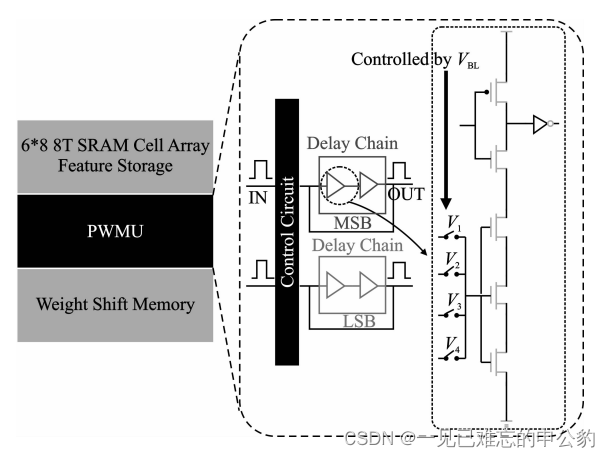

基于脉冲宽度调制的8T-RAM 存内计算.Yang 等人设计了一款基于 8TSRAM 三明治 RAM 设备,能够实现特征值8bit,权重 lbit 的BWN 网络,如图7所示,该方案将特征值和权重值的存储单元分别存储在脉冲宽度调制单元PWMU附近,在计算模式下,两位输入会经2-4译码器置换成4种电压水平,用于调整脉冲宽度,权重作用在选择器上,如果权重为1,脉冲宽度会对应扩展,反之则缩短,最终经脉冲量化器量化得到最终结果,该设计通过特制的 PWMU 实现了时间域的乘加计算,能耗效率可达到 119.7 TOPS/W,但是 8TSRAM 和 PWMU 单元都会造成大面积开销.同时:模拟域的 SRAM 存内计算对 PVT 以及版图走线比较敏感,相应的计算精度、量化误差问题仍需进步优化改进

架构如下图:

基于电压域的SRAM技术缺点

基于电压域的SRAM技术存在以下缺点:

- 电压窗口受限:SRAM存储单元的电压变化范围有限,这限制了可实现的功能和计算精度。

- 高精度电压控制:需要高精度的电压源和电压调节电路,增加了硬件复杂性和成本。

温度、工艺和时间影响:SRAM存储单元的电压变化会受到温度、工艺和时间的影响,这会影响技术的稳定性。 - 可扩展性挑战:随着存储器规模的扩大,电路的复杂性和功耗都会显著增加。

- 集成度和能耗:SRAM的基本单元电路较复杂,集成度较低,且运行功耗较大。

- 成本高:每个存储单元需要更多的晶体管,使得SRAM的成本较高。

基于电压域的SRAM技术的优点

基于电压域的SRAM技术具有以下优点:

- 高性能:SRAM作为读写速度最快的内存介质,具备高能效比的计算优势,适用于需要高速处理的应用场景,如自动驾驶、无人机等对计算准确性和反应速度要求高的场景。

- 可扩展性强:SRAM可向先进制程兼容,从而达到更高的能效比和面效比,有助于实现更大规模的存内计算。

- 工艺成熟度高:SRAM的工艺成熟度较高,可以相对较快地实现技术落地与量产。

- 精度无损:SRAM在进行操作时不需要动态的刷新电路,读写延迟短,精度无损。

- 集成度高:SRAM具有集成度高,完全兼容数字逻辑电路工艺等优点。

- 低功耗:由于SRAM在进行操作时不需要动态的刷新电路,使其具有快速访问、较低功耗等优点。

电压域的SRAM技术的局限性

基于电压域的SRAM技术虽然具有许多优点,但也存在一些局限性。

-

由于SRAM存储单元的电压变化范围有限,因此基于电压域的SRAM技术只能在有限的电压范围内实现逻辑运算,这限制了其可实现的功能和计算精度。

-

基于电压域的SRAM技术需要精确控制存储单元的电压,这需要高精度的电压源和电压调节电路,增加了硬件复杂性和成本。

-

由于SRAM存储单元的电压变化会受到温度、工艺和时间的影响,因此基于电压域的SRAM技术的稳定性有待提高。

基于电压域的SRAM技术的可扩展性也有挑战。随着存储器规模的扩大,电路的复杂性和功耗都会显著增加,因此需要解决如何在大规模存储器中实现高效、低功耗的存内计算技术。

尽管存在这些局限性,基于电压域的SRAM技术仍然是一种非常有前途的存内计算技术,可以应用于人工智能、物联网、智能传感器等领域。未来随着技术的不断发展和完善,相信这些局限性可以得到一定程度的解决。

应用领域

基于电压域的SRAM存内计算技术的应用场景主要包括人工智能、物联网、智能传感器等领域。在人工智能领域,这种技术可以用于实现神经网络的存储和计算,从而提高神经网络的性能和能效。在物联网和智能传感器领域,这种技术可以用于实现高效的数据处理、分析和传输,从而提高物联网和智能传感器的性能和能效。

基于电压域的SRAM存内计算技术是一种非常有前途的技术,它可以提高数据处理的效率和能效,降低功耗和硬件成本。未来随着技术的不断发展和完善,这种技术有望在更多领域得到应用。

总结

这篇文章总结了冯·诺伊曼架构及其在处理数据密集型应用中所面临的性能和能耗问题。为了应对这一挑战,文章介绍了存内计算技术,其中重点讨论了基于电压域的SRAM存内计算技术。

在冯·诺伊曼架构中,存储器和处理器之间频繁传输大量数据,导致性能瓶颈。为解决这个问题,存内计算技术被提出,其核心思想是将计算单元整合到存储器中,实现数据在存储和计算之间的直接传输,从而提高数据处理效率和降低能耗。

特别关注了基于电压域的SRAM存内计算技术,这一技术利用SRAM存储单元的电压变化来实现计算功能。通过将数字量转化为电压值,利用电荷共享的方式进行计算,最终将结果转换为数字信号。这种技术在人工智能、大数据处理、图像处理等领域有着广泛的应用前景。

总体而言,基于电压域的SRAM存内计算技术在改善冯·诺伊曼架构的性能和能耗方面具有潜在的优势,为未来在各个领域的应用提供了创新的可能性。

参考文献

微电子学与计算机-SRAM 存内计算技术综述

291

291

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?