文章目录

一、HLS简介

1、HLS是什么

高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。所谓的高层次语言,包括C、C++、SystemC等,通常有着较高的抽象度,并且往往不具有时钟或时序的概念。相比之下,诸如Verilog、VHDL、SystemVerilog等低层次语言,通常用来描述时钟周期精确(cycle-accurate)的寄存器传输级电路模型,这也是当前ASIC或FPGA设计最为普遍使用的电路建模和描述方法。

2、HLS与VHDL/Verilog编程技术有什么关系

HLS 是一个很好的研究方向,涉及的技能知识和研究点都非常多,需要懂得编译、OS和数字电路等等,每个都是大头,但我不觉得HLS会是未来硬件描述的最佳解决方案。合适的方案应该提供一个抽象层次更高的硬件描述语言。verilog 适合于RTL 级别的硬件描述,但是RTL 级别的硬件描述其实还是过于底层,因此这也带来了很多繁重的编码和设计工作,类似于汇编程序一样,合适的解决方案类似于软件编程中从汇编走向C/C++的过程,提供一个更高层次的抽象描述,并提供一些基本的微结构组件,用于快速搭建数字系统。像blue spec/ chisel就给我有这种感觉。

无论是HLS还是Verilog,两者代表了两个“极端”的方向。Verilog可以精准的控制电路实现,但实现起来需要较长的周期,而HLS虽然可快速迭代,但其从软件到硬件翻译无论是面积还是资源均难以控制。目前我们的算法加速设计采用SpinalHDL,在保持电路本身特性的同时,借助scala语法能够快速的做电路实现。

二、HLS技术

1、HLS关键技术问题

1、将高级语言转化为RTL电路

2、循环优化,并行处理

2、技术局限性

1、与Verilog相比,能做到的优化十分有限

2、HLS编译器是静态工具,对理解代码的动态特性没有任何帮助

3、对于一些简单的逻辑,HLS实现结果较为臃肿

4、HLS对开发人员的要求比较高。

三、HLS开发环境搭建

工具选择:

quartus 18.1;

Visual Studio 2010.

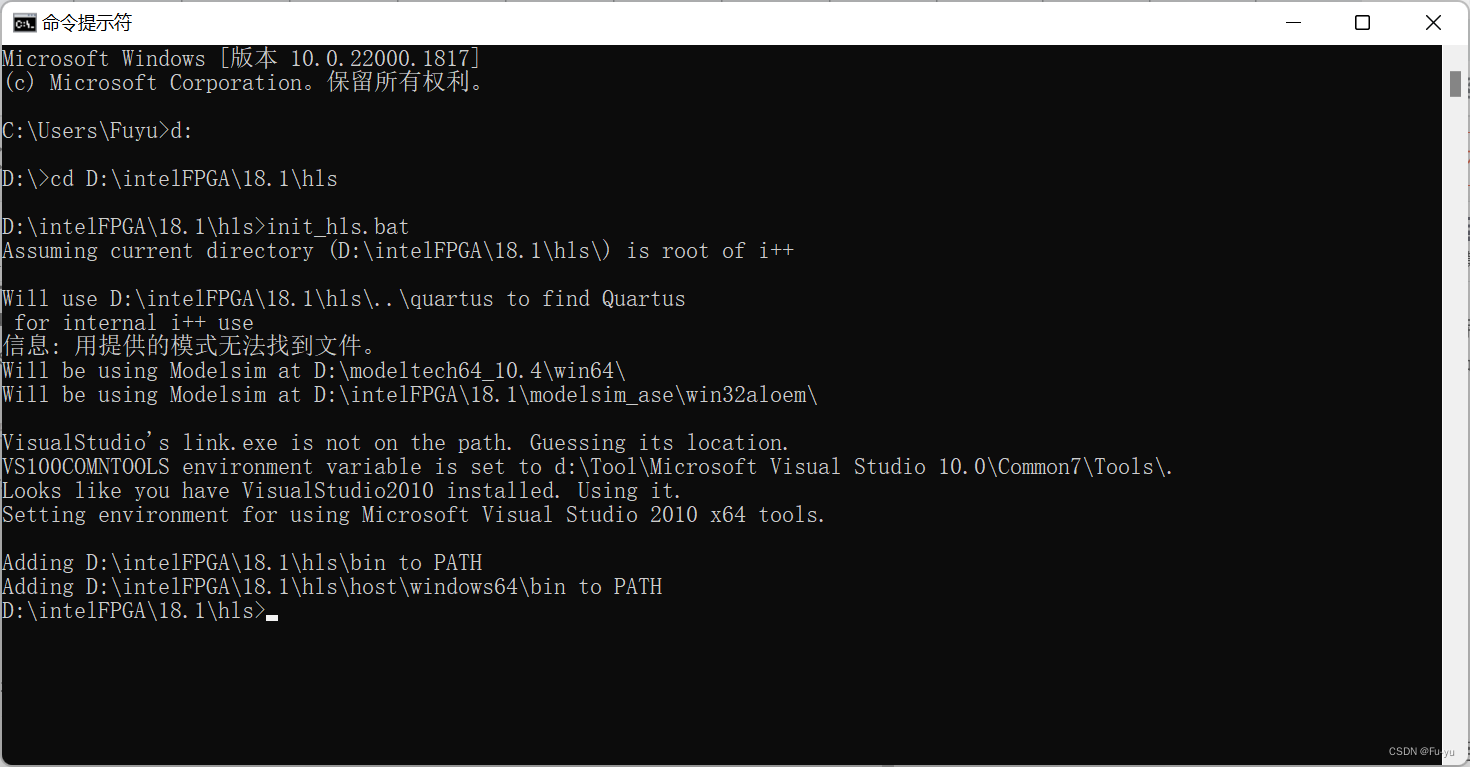

1、初始化

打开系统命令管理器cmd,定位到init_hls.bat的路径,并运行

d:

cd D:\intelFPGA\18.1\hls

init_hls.bat

2、编写测试文件

在桌面新建项目hls_prj,创建temp.cpp,编写如下乘法器代码:

#include “HLS/hls.h”

#include “stdio.h”

component int mul(int a,int b)

{

int c =0;

c = a*b;

return c;

}

int main()

{

int a=0,b=0,c=0,i=0;

for(i=0;i<5;i++)

{

a= i+1;

b= i+2;

c = mul(a,b);

printf("%d * %d = %d\n",a,b,c);

}

return 0;

}

3、编辑测试文件

切换到刚刚新建的工程目录

cd D:\Desktop\hls_prj\temp\temp

i++ -march=x86-64 -o mul.exe temp.cpp

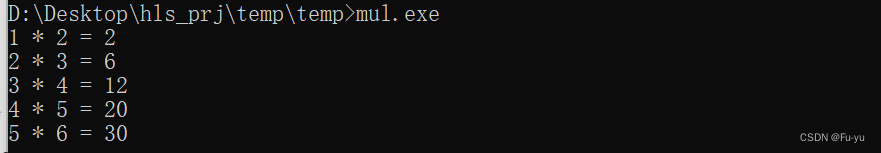

运行mul.exe文件

mul.exe

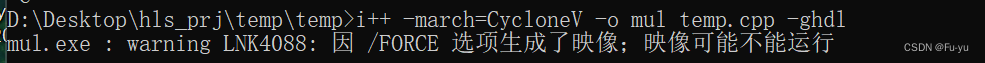

生成镜像文件

i++ -march=CycloneV -o mul test.cpp -ghdl

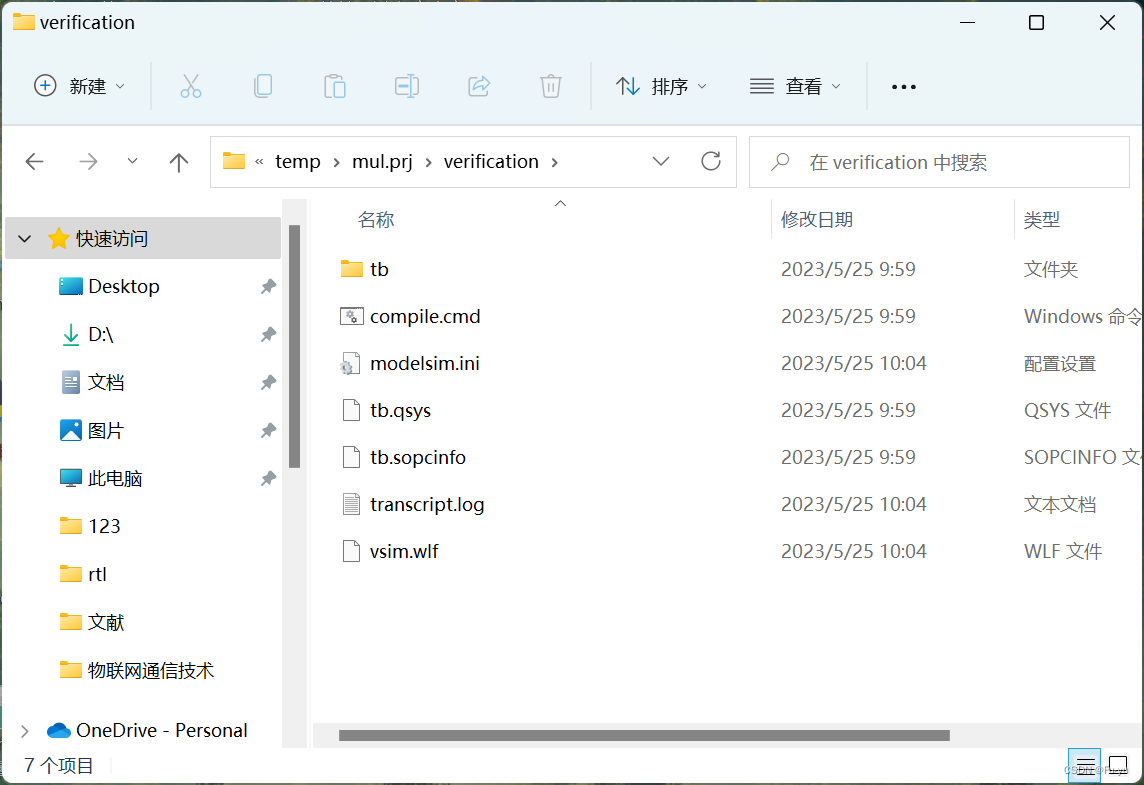

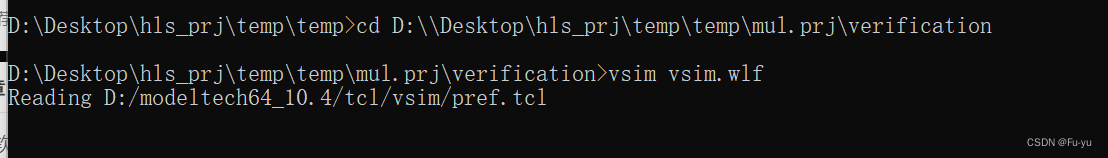

继续运行mul.exe文件,产生波形文件vsim.wlf

mul.exe

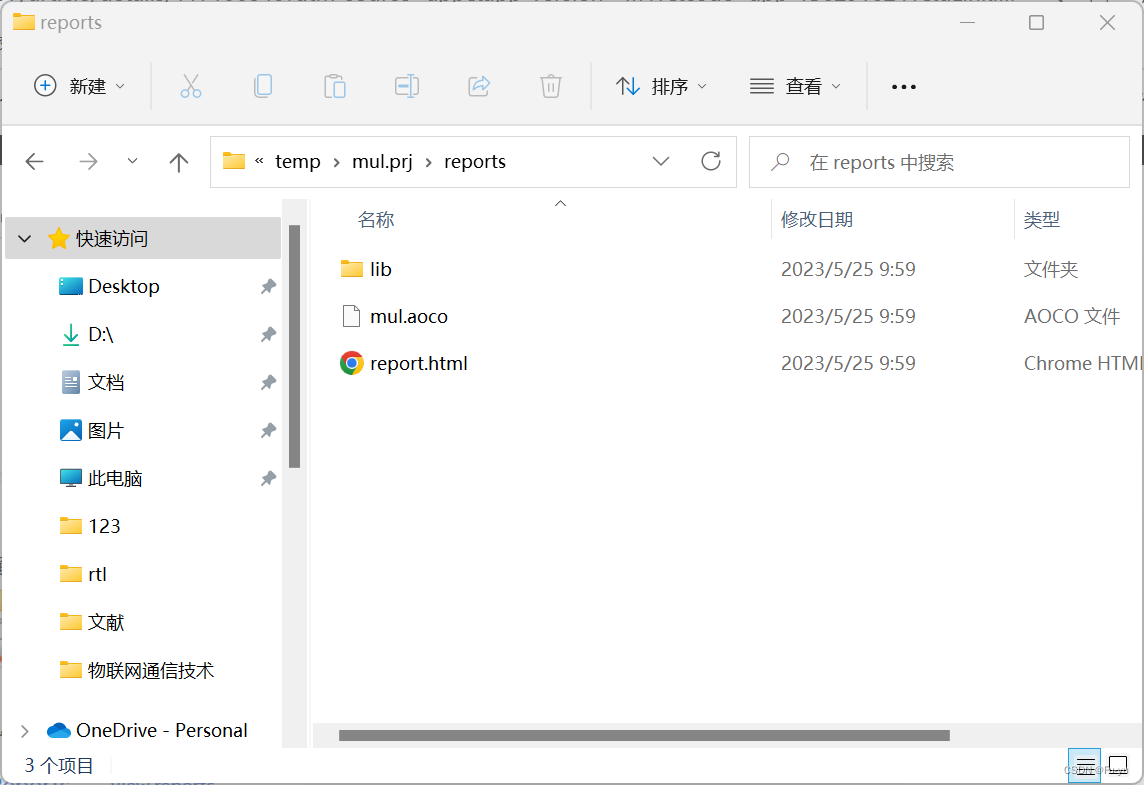

查看报告

报告内容如下

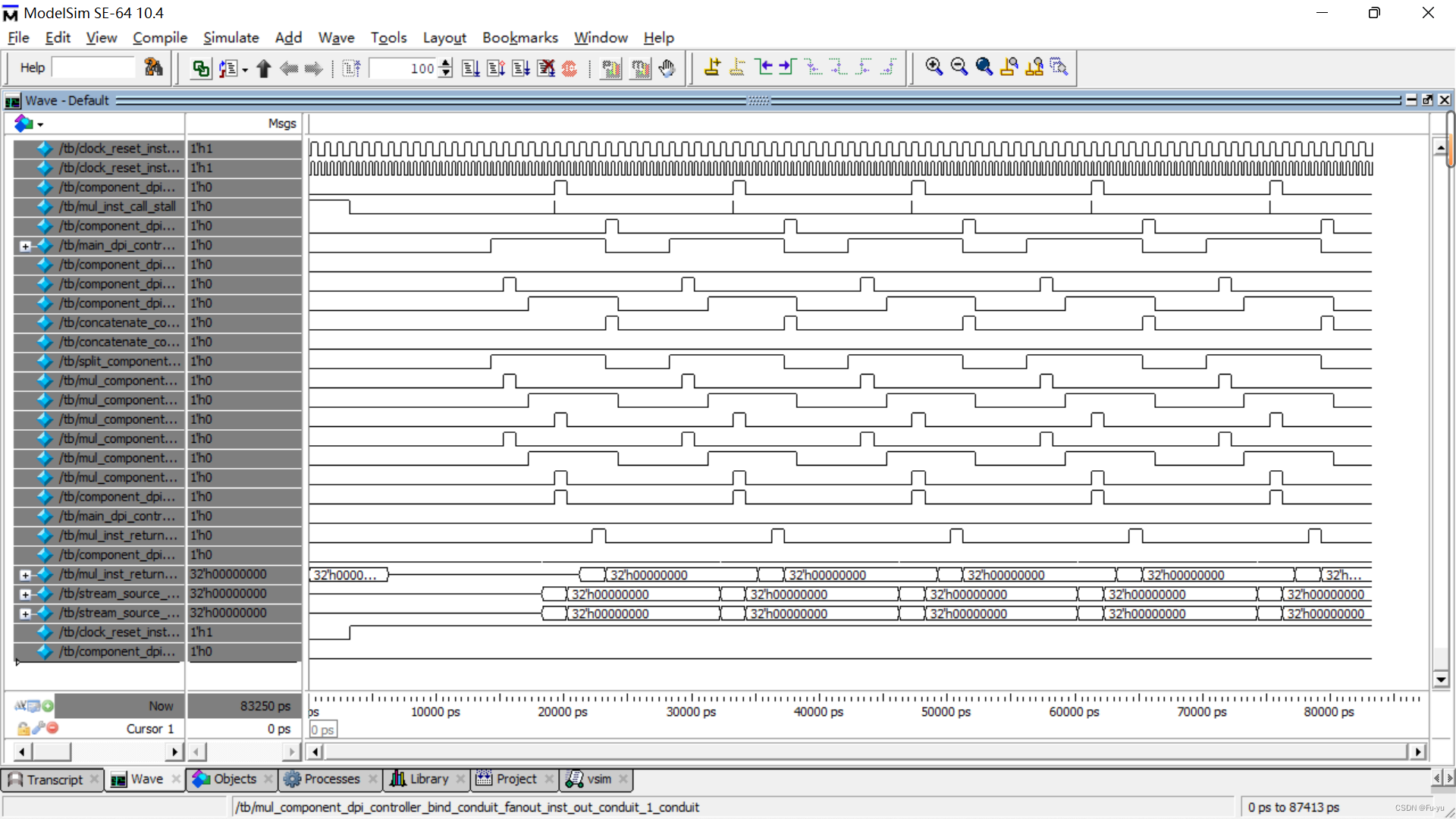

打开波形文件

4、HLS-IP核的工程建立

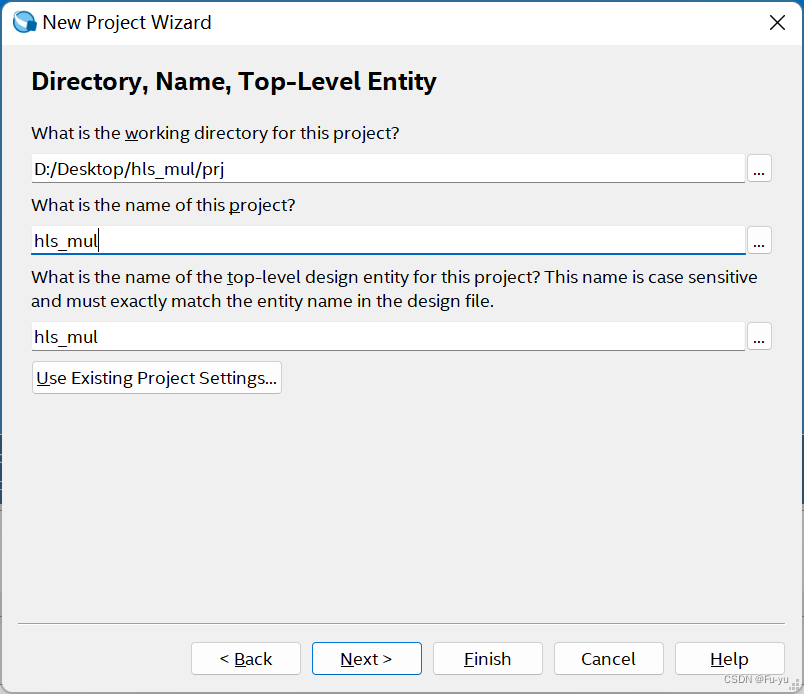

4.1、新建quartus项目

4.2、导入自编辑IP核

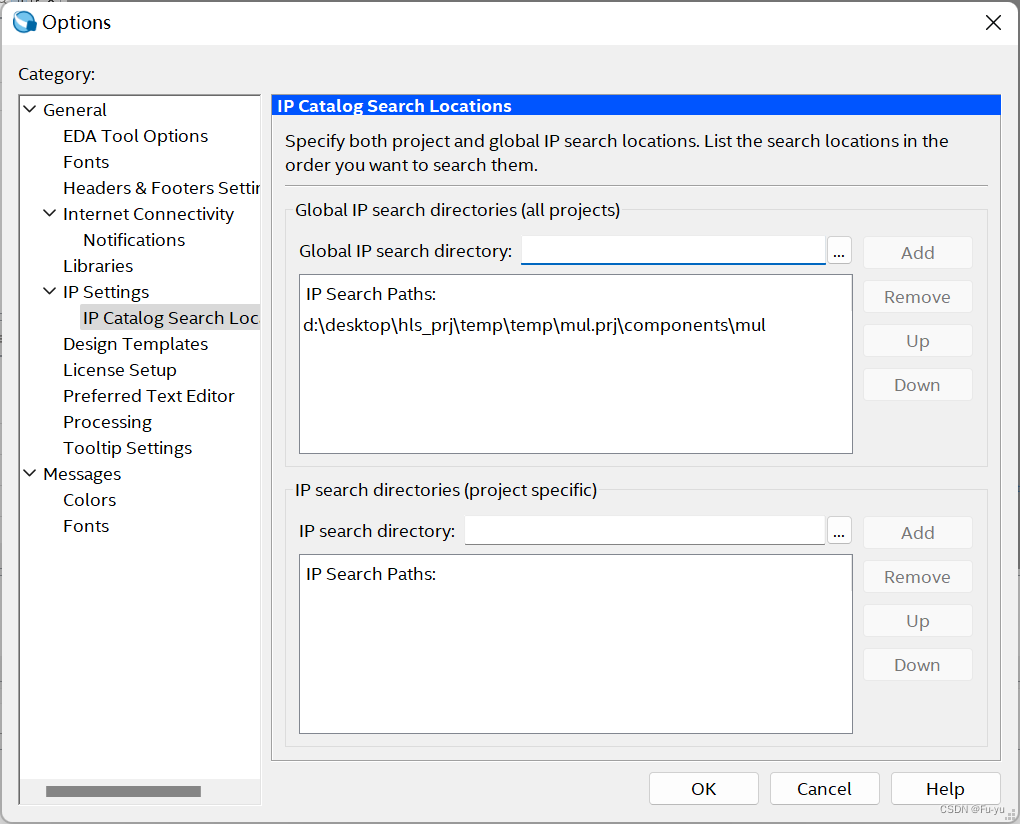

Tools–>Options–>IP Setting–>IP Catalog Search Locations

4.3、HLS-IP核的添加

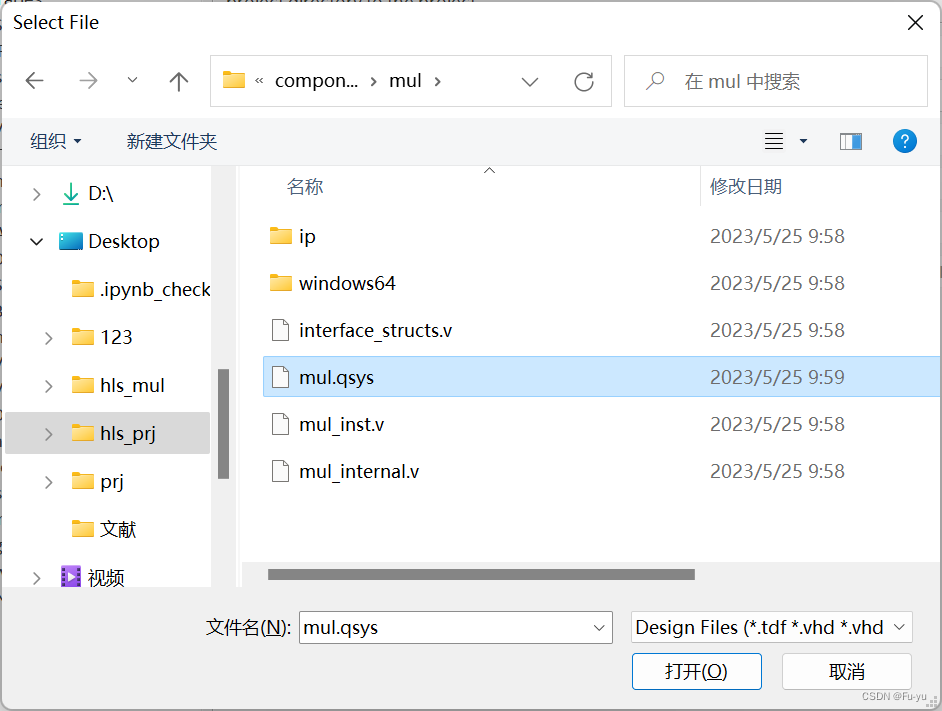

添加生成的qsy文件

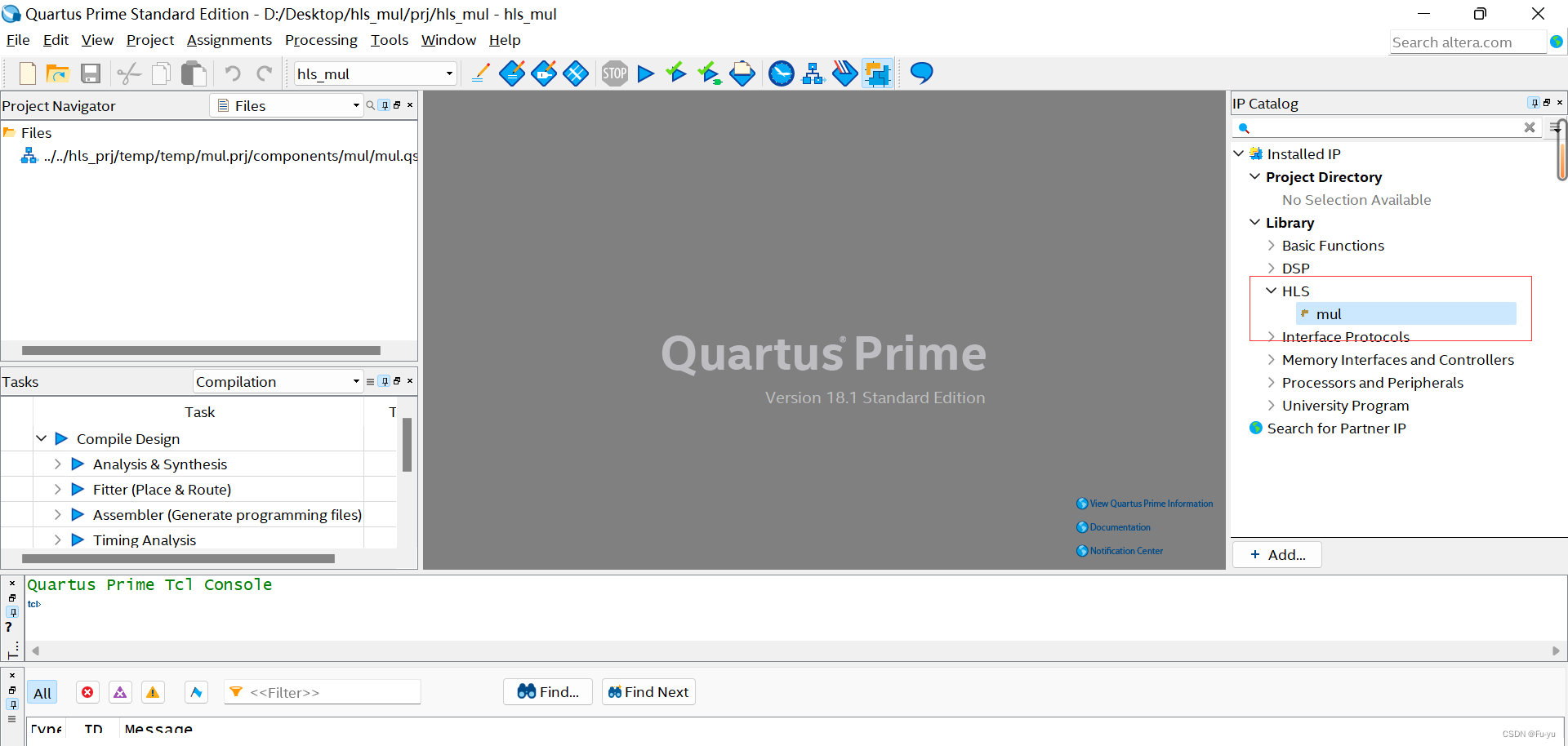

找到已经添加的IP核

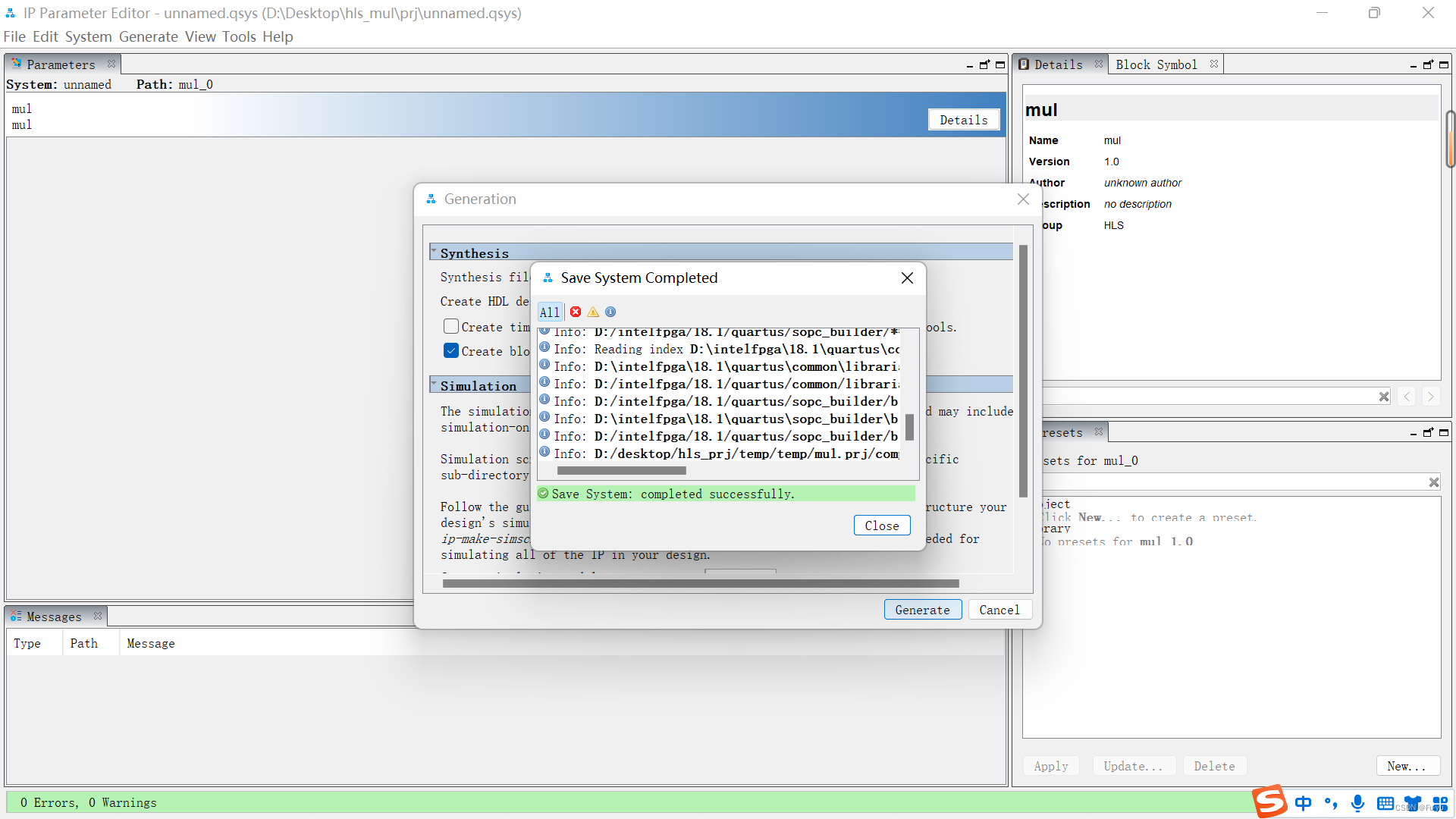

双击mul IP核,在弹出的框中,点击generate HDL

在弹出新的对话框,点击generate,一直点击退出,直到最后一层,点击finish。

5、模块实例化

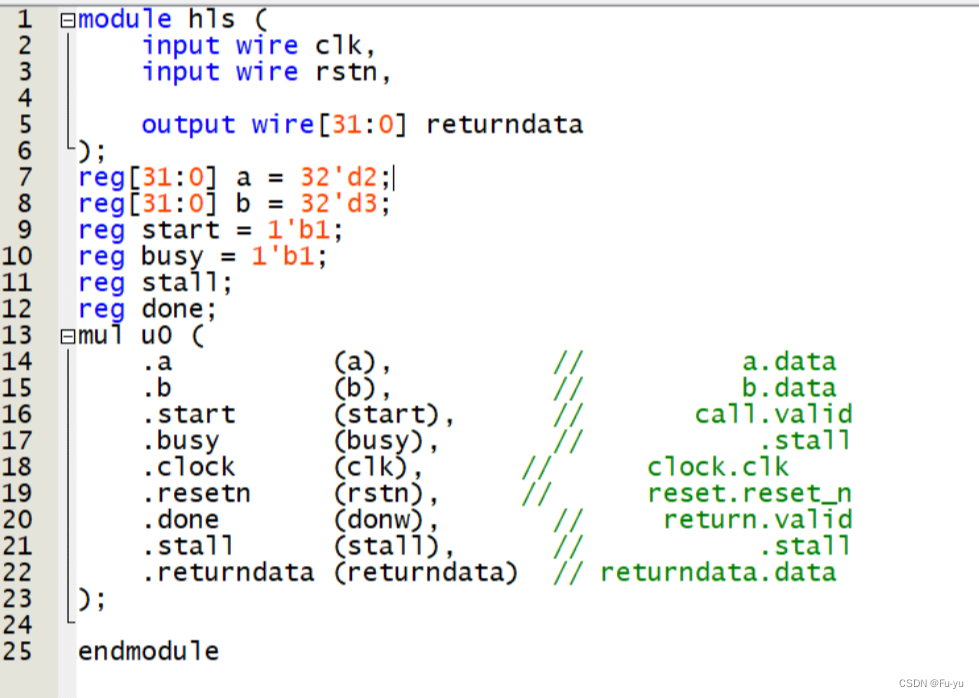

在之前创建的工程中,新建Verilog文件,命名为hls

双击之前打开的qsy文件

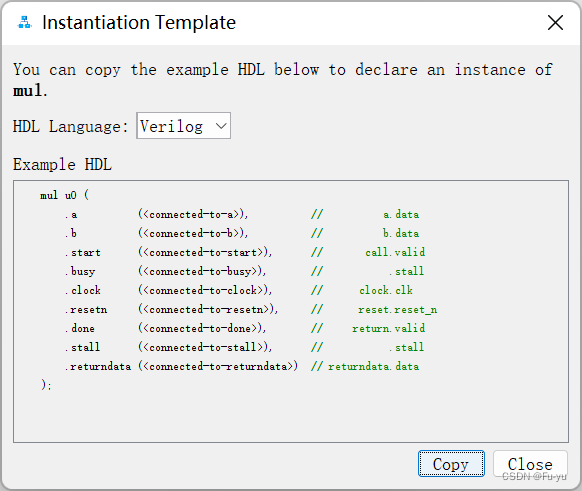

点击generate->Show instantination Template

copy其中的内容加入到编写的hls.v文件中,并进行实例化

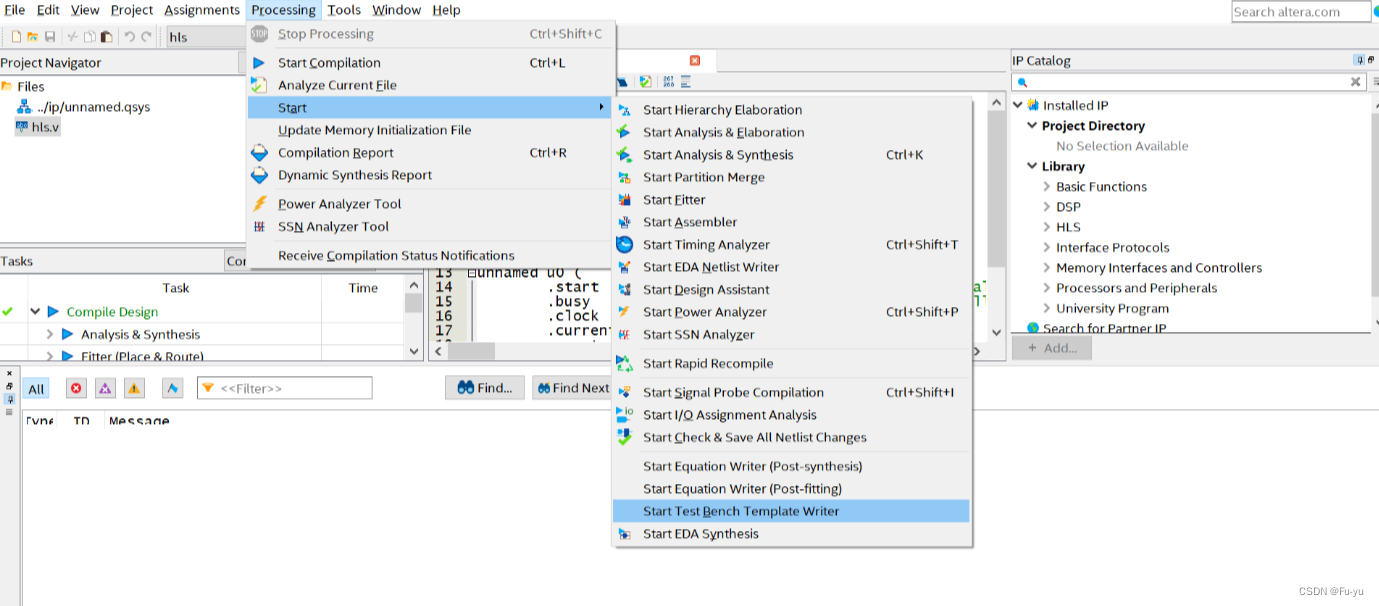

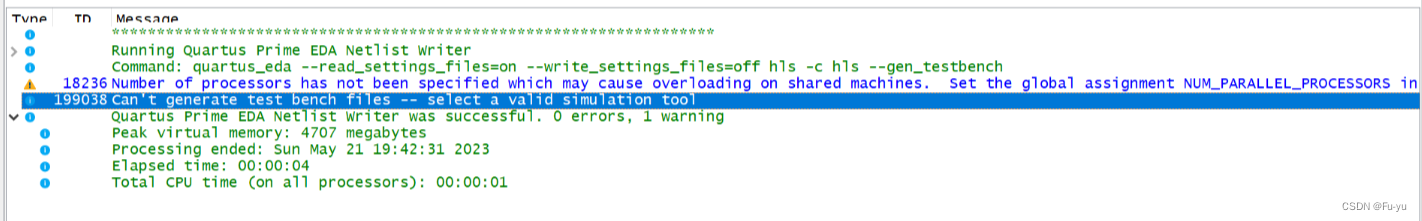

编译测试代码:双击Analysis & Synthesis,编译成功后,生成测试文件。

此时HLS工程创建完毕。

参考链接

https://blog.csdn.net/weixin_45888898/article/details/117372276

https://blog.csdn.net/u010835747/article/details/112141781

817

817

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?