module keyled

(

input sys_clk,

input sys_rest_n,

input [3:0] key, //按键输入信号

output reg[3:0] led //led输出信号

);

reg [23:0]cnt; //时钟计数

reg [1:0]led_ctrl; //按键状态

//用于计数0.2s的计数。

always @ (posedge sys_clk or negedge sys_rest_n)

begin

if(!sys_rest_n)

cnt <= 24'd0;

else

if(cnt<24'd10000000)

cnt <= cnt + 1'b1;

else

cnt <= 24'd0;

end

always @(posedge sys_clk or negedge sys_rest_n)

begin

if(!sys_rest_n)

led_ctrl <= 2'd0;

else

if(cnt == 24'd10000000)

led_ctrl<=led_ctrl+1'b1;

else

led_ctrl<=led_ctrl;

end

always @(posedge sys_clk or negedge sys_rest_n)

begin

if(!sys_rest_n)

led <= 4'b0000;

else if(key[0]==1'b0)

case(led_ctrl)

2'd0 : led<=4'b1000;

2'd1 : led<=4'b0100;

2'd2 : led<=4'b0010;

2'd3 : led<=4'b0001;

default : led<=4'b0000;

endcase

else if(key[1]==1'b0)

case(led_ctrl)

2'd0 : led<=4'b0001;

2'd1 : led<=4'b0010;

2'd2 : led<=4'b0100;

2'd3 : led<=4'b1000;

default : led<=4'b0000;

endcase

else if(key[2]==1'b0)

case(led_ctrl)

2'd0 : led<=4'b1111;

2'd1 : led<=4'b0000;

2'd2 : led<=4'b1111;

2'd3 : led<=4'b0000;

default : led<=4'b0000;

endcase

/*else if(key[0]==1'b0)

case (led_ctrl)

2'b00 : led <= 4'b1000;

2'b01 : led<= 4'b0100;

2'b10 : led <=4'b0010;

2'b11 : led<=4'b0001;

default : led<=4'b0000;

endcase

else if (key[1]==1'b0) //按键2按下时,从左向右的流水灯效果

case (led_ctrl)

2'b00 : led<=4'b0001;

2'b01 : led<=4'b0010;

2'b10 : led<=4'b0100;

2'b11 : led<=4'b1000;

default : led<=4'b0000;

endcase

else if (key[2]==1'b0) //按键3按下时,LED闪烁

case (led_ctrl)

2'b00 : led<=4'b1111;

2'b01 : led<=4'b0000;

2'b10 : led<=4'b1111;

2'b11 : led<=4'b0000;

default : led<=4'b0000;

endcase

*/

else if(key[3]==1'b0)

led = 4'b1111;

else

led = 4'b0000;

end

endmodule

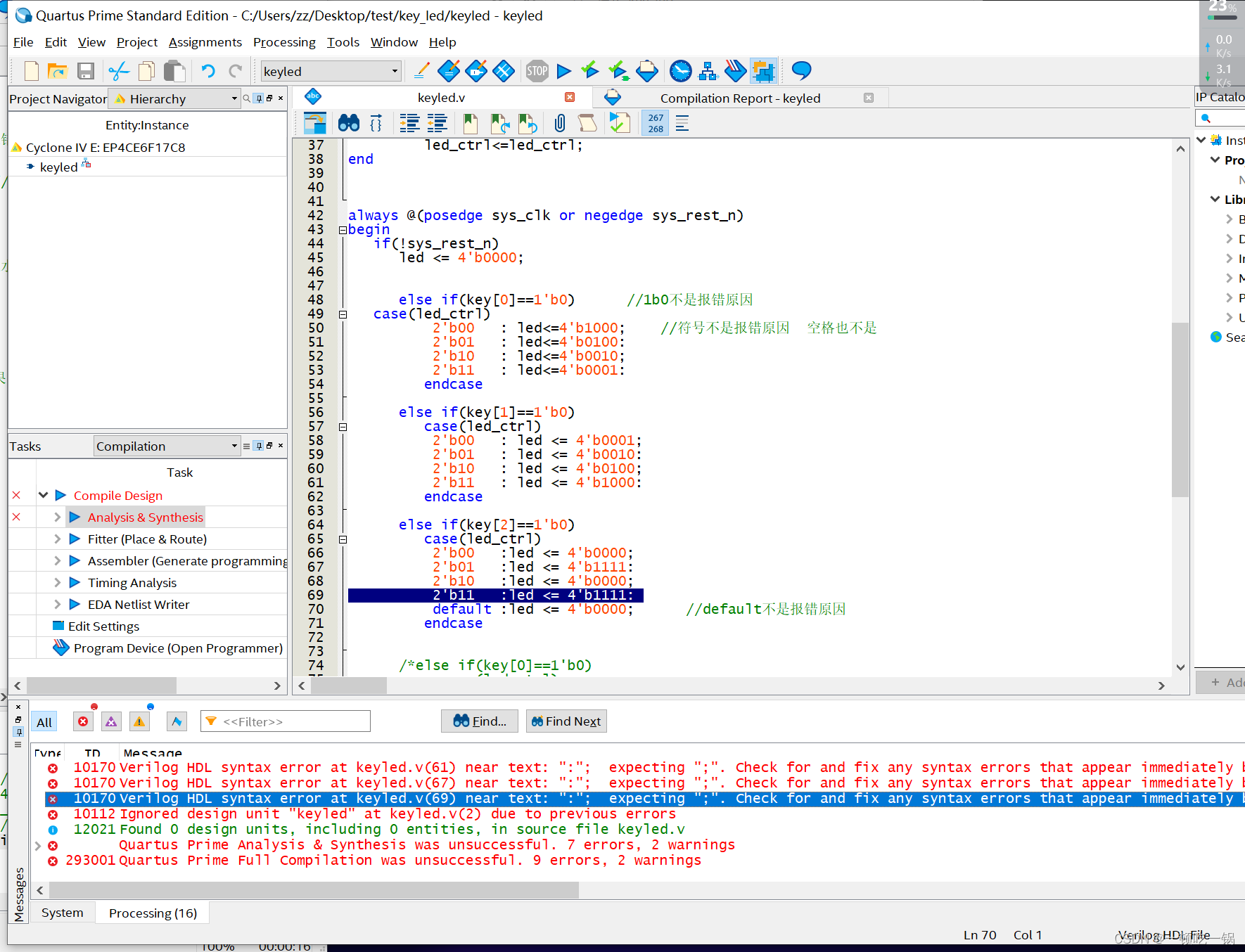

//下面的报错找了很久,是因为符号的问题!!!

560

560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?