本次设计是基于Xilinx旗下的Artix-7的开发环境下,首先需要设计流水灯的闪烁规则。本次设计采用的开发板只有四个LED灯,所以循环规则应该是0001→0010→0100→1000→0001...1000;本次设计流水灯闪烁为1S一次的间隔,由这些条件可以先进行模块的设计。

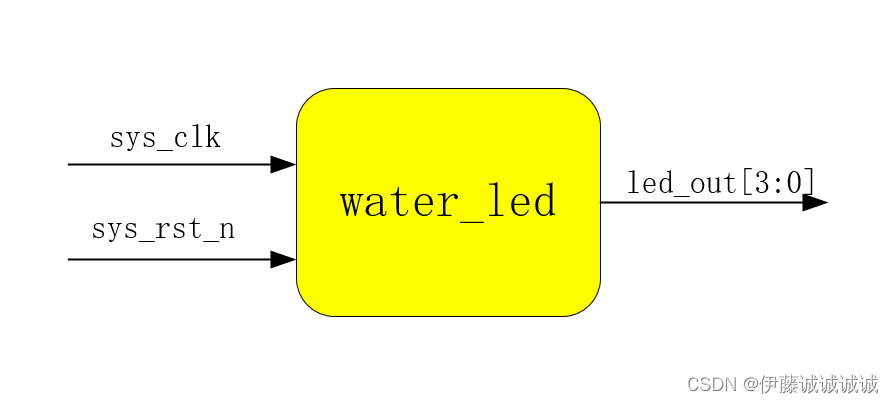

LED流水灯基本面板如下:

由上图模块可以知道,模块有两路输入一路输出,根据这个模块可以进行波形的绘制

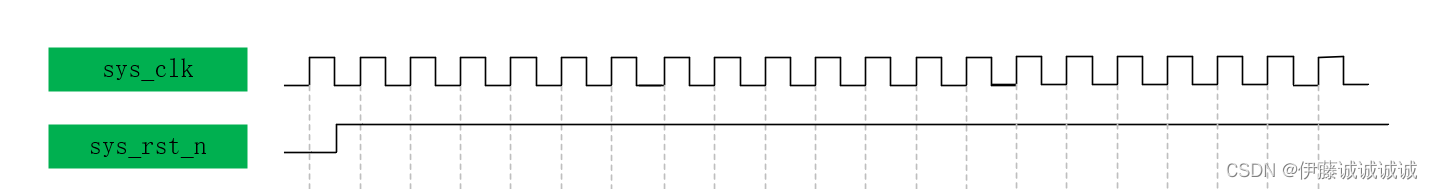

首先是时钟和复位的波形图

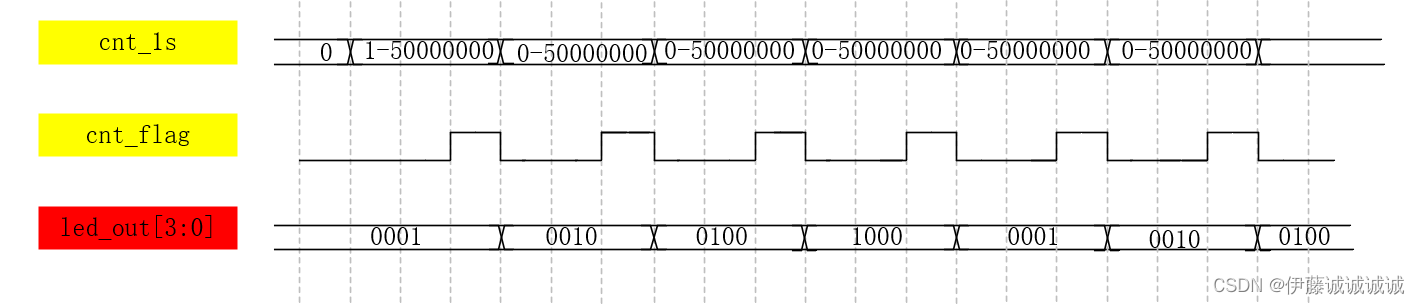

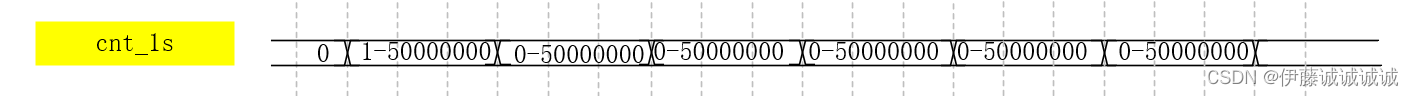

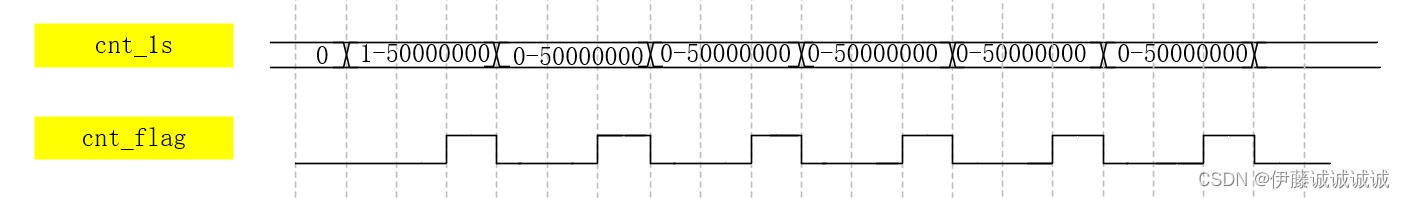

设置的延迟间隔为1S,时钟频率为50MHz,所以每秒计数等于1/(1/50_000_000),每秒计数为50_000_000 ,转换成二进制位26位,所以可以画出1s计数的波形

为了准确判断1S计数结束可以增加一个1S计数的标志位

标志位在计数到达最大值之前的一个时钟周期变成高电平,在计数到最大值之后变为低电平

然后是LED的输出

在1S延迟后进入下一个循环指令,由这个波形图就可以编写LED流水灯的模块代码了

module water_led #( parameter CNT_MAX = 26'd50_000_000 ) ( input sys_clk, input sys_rst_n, output reg [3:0] led_out ); reg [25:0] cnt_1s; reg cnt_flag; //1s计数器 always@(posedge sys_clk or negedge sys_rst_n) if(!sys_rst_n) cnt_1s <= 26'd0; else if(cnt_1s == CNT_MAX) cnt_1s <= 26'd0; else cnt_1s <= cnt_1s + 26'd1; //1s计数器标志位 always@(posedge sys_clk or negedge sys_rst_n) if(!sys_rst_n) cnt_flag <= 1'b0; else if(cnt_1s == CNT_MAX - 26'd1) cnt_flag <= 1'b1; else cnt_flag <= 1'b0; //led_out always@(posedge sys_clk or negedge sys_rst_n) if(!sys_rst_n) led_out <= 4'b0001; else if((led_out == 4'b1000) && (cnt_flag == 1'b1)) led_out <= 4'b00001; else if(cnt_flag == 1'b1) led_out <= led_out <<1; else led_out <= led_out; endmodule在simulate source 这里添加测试文件testbench.v 文件

`timescale 1ns/1ns module tb_water_led(); reg sys_clk; reg sys_rst_n; wire [3:0] led_out; initial begin sys_clk <= 1'b1; sys_rst_n <= 1'b0; #20 sys_clk <= 1'b1; end always #10 sys_clk <= ~sys_clk; water_led #( .CNT_MAX(26'd20) ) water_led_inst ( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .led_out (led_out) ); endmodule程序基本这样,纯手打没有进行验证,大概就是这个循环,接下来就是可以创建DXC文件进行管脚的约束,LED流水灯的实现基本就告一段落了。

FPGA流水灯闪烁

最新推荐文章于 2024-05-21 14:27:39 发布

936

936

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?