2.0 Protocol Layer

Universal Chiplet Interconnect express (UCIe)可以映射PCIe、CXL以及任何流式传输协议。以下是使用的协议映射:

- PCIe 6.0 Flit Mode

- CXL 2.0,"CXL 68B-Enhanced Flit Mode","CXL 256B Flit Mode":如果协商使用CXL,将独立协商CXL.io、CXL.cache和CXL.mem协议。

- 流式传输协议:这提供了用于通过UCIe传输用户定义协议的通用模式。

注意:不支持CXL 1.1。通过CXL.io 68B Flit Mode提供对PCIe非Flit Mode的支持。

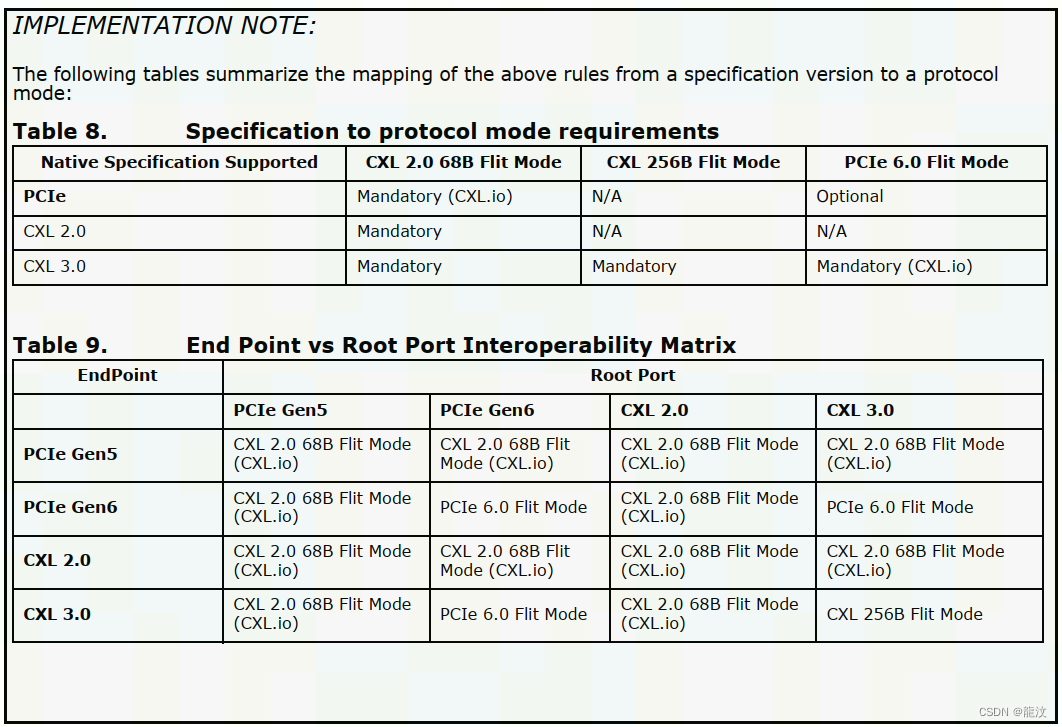

协议层的互操作性要求如下:

- 如果协议层宣称支持PCIe,它必须支持CXL 2.0规范中定义的CXL.io协议的68B Flit Mode。

- 如果协议层支持"CXL 256B Flit Mode",它必须支持PCIe 6.0 Flit Mode和CXL 2.0规范中定义的CXL.io协议的68B Flit Mode。

- 宣称支持CXL的协议层只允许支持CXL 2.0或CXL 68B-Enhanced Flit Mode,而不支持"CXL 256B Flit Mode"或PCIe 6.0 Flit Mode。

Die-to-Die (D2D) Adapter是与远程链路协商协议并将其通知给协议层的组件。对于每个协议,UCIe支持多种操作模式(根据宣传的功能、物理层状态以及使用模型与远程链路进行协商)。这些模式具有不同的Flit格式,并定义了在效率、带宽和互操作性方面进行不同权衡的能力。支持的协议、宣传的模式和Flit格式的范围必须在SoC集成时或在特定芯片重置启动流程期间确定。Die-to-Die Adapter使用这些信息作为链路训练的一部分来协商操作模式,并通过Flit感知的Die-to-Die接口(FDI)通知协议层。有关适配器中参数交换规则的详细信息,请参阅第3.1节。

根据协议层的角度,后续章节概述了不同模式,因此它们按协议分为子章节,涵盖了支持的操作模式。协议层负责根据协商的模式和Flit格式通过FDI传输数据。本章中格式的示例配置显示了协议层中的64B数据路径映射到UCIe的物理链路上的64 Lane模块的高级封装配置。某些Flit格式由适配器填充了专用的字节位置,与此相关的细节在第3.0章节中单独说明。对于其他链路宽度,请参考第4.1.1节中定义的字节到Lane的映射。

2.1 PCIe 6.0

UCIe仅支持PCI Express Base Specification Revision 6.0中定义的Flit模式。请参考PCI Express Base Specification Revision 6.0获取协议定义。对于PCIe,UCIe支持两种操作模式,这些模式在下面的子章节中定义。在说明这些模式的不同格式的图中,灰色的字节表示适配器插入的信息。在这些信息作为Flit的一部分显示的情况下(例如在标准的256B Flit中),协议层必须在发送端将其设置为0,并在接收端忽略它们。

2.1.1 Raw Mode for PCIe 6.0

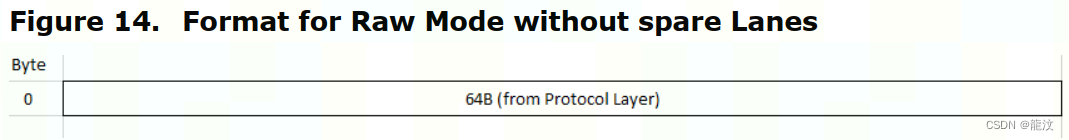

这种模式是可选的。其预期用途是用于传输PCIe协议的UCIe Retimers。一个示例用途是,当CPU和I/O设备位于不同的机架/机箱中,并通过使用Off-Package Interconnect的UCIe Retimer连接,如图2所示。对于原始模式,重传、CRC和FEC由协议层处理。所有64个字节都由协议层填充。强烈建议UCIe Retimers使用PCIe Express Base Specification中为此模式定义的6B FEC的奇偶校验位或Flit模式8B CRC来检查和计数错误,以帮助表征D2D链路(以表征或调试作为主要错误源的链路)。

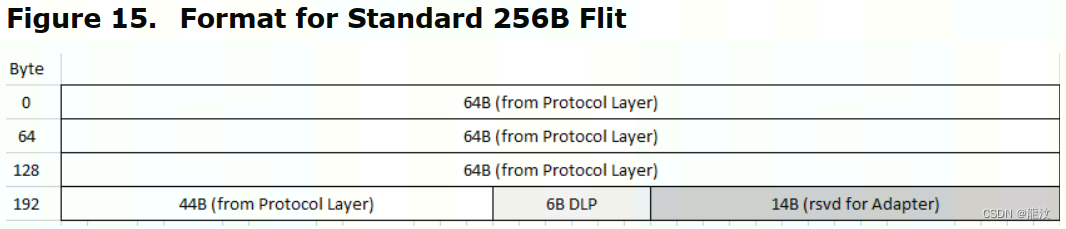

2.1.2 Flit Mode: Standard 256B Flit for PCIe 6.0

当支持PCIe协议时,这种模式是强制性的。它是PCI Express Base Specification中定义的标准Flit格式,支持此Flit格式的主要目的是为了与仅支持标准PCIe Flit格式的供应商实现互操作性。协议层必须按照FDI上的Flit传输的Flit格式,在保留给Die-to-Die Adapter的字段上设置为0。在UCIe上不使用PM和Link Management DLLPs。其他DLLPs(适用于PCIe Flit Mode的DLLPs)和Flit状态定义遵循相同的规则,包括在PCI Express Base Specification Revision 6.0中定义的打包方式。强烈建议在实现中优化掉协议层中与8b/10b、128b/130b和非Flit Mode相关的CRC/Retry或帧逻辑,以获得面积和功耗高效的UCIe应用设计。DLP字节的部分内容必须由协议层驱动,用于Flit_Marker的分配;有关如何驱动DLP字节的详细信息,请参阅第3.2.3节。

2.2 CXL 3.0 256B Flit Mode

请参考Compute Express Link规范,了解关于协议层消息和“CXL 256B Flit Mode”的插槽格式的详细信息。该协议有四种可能的操作模式,这些模式在下面的子节中定义。适配器会插入灰色字节。在这些字节被显示为主数据路径的一部分的情况下(例如在标准的256B Flit中),协议层必须在发送端将其设置为0,并在接收端忽略它们。

2.2.1 Raw Mode for "CXL 256B Flit Mode"

这种模式是可选的。它的预期用途是用于传输"CXL 256B Flit Mode"协议的UCIe Retimers。该模式的一个示例用法是,当CPU和I/O设备位于不同的机架/机箱中,并通过使用Off-Package互连的UCIe Retimer进行连接时。重传、CRC和FEC由协议层处理。所有的64个字节都由协议层填充。图14显示了该模式下的传输示例。强烈建议UCIe Retimers使用6B FEC的奇偶校验位或Flit Mode 8B CRC或6B CRC来检查和计数错误,具体取决于启用了哪种Flit格式。这有助于对主要错误源D2D Link进行特征化和调试。对于CXL.cachemem、Viral或poison封装(如果应用),必须在该模式下由协议层处理。

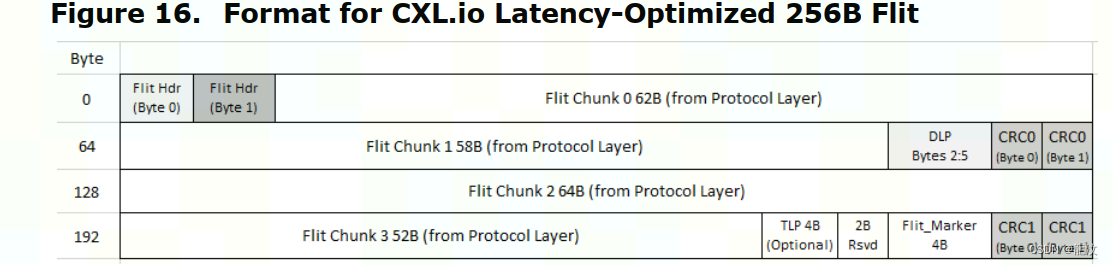

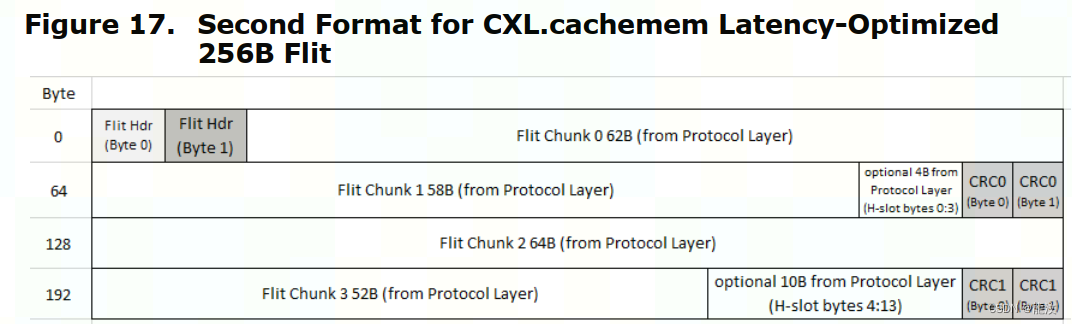

2.2.2 Flit Mode: Latency-Optimized 256B Flit for "CXL 256B Flit Mode"

强烈建议在UCIe上支持"CXL 256B Flit Mode"的这种模式。该模式定义了两种Flit格式,这两种格式是从Compute Express Link 3.0规范中定义的延迟优化Flit派生而来的。第二种Flit格式与第一种Flit格式的唯一区别是,它通过为协议层提供额外的字节来提供更高的Flit打包效率——对于CXL.io,这会导致额外的4B TLP信息,对于CXL.cachemem,这会导致额外的14B H-slot可以打包在Flit中。在链路建立时,可以协商支持第一种或第二种格式。延迟优化模式使协议层能够以128B边界消耗Flit,显著降低积累延迟。当协商使用这种模式时,协议层必须按照此Flit格式在FDI上进行Flit传输,并在保留给Die-to-Die Adapter的字段上发送0。

在UCIe上,对于任何256B Flit模式的CXL.io,不会使用Ack、Nak、PM和Link Management DLLP。其他DLLP和Flit_Marker的定义遵循Compute Express Link规范中定义的相同规则。协议层必须驱动DLP字节的部分内容来进行Flit_Marker分配;请参考第3.2.3节,了解有关如何驱动DLP字节的详细信息。

对于此模式下的CXL.cachemem,FDI提供了一个lp_corrupt_crc信号,以在保证Viral封装的同时优化延迟。有关Viral封装的接口规则的详细信息,请参考第8.0章节。

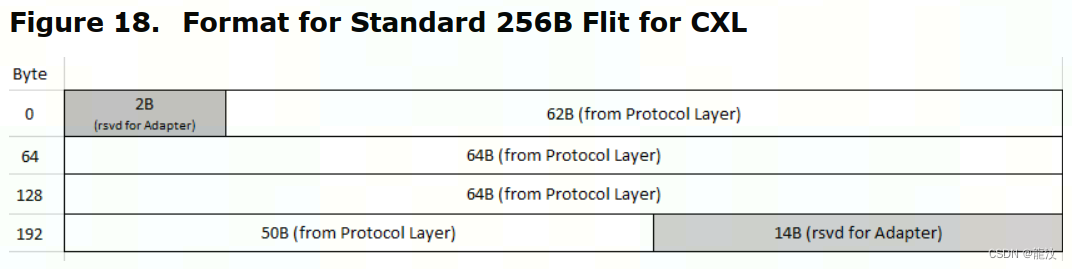

2.2.3 Flit Mode: Standard 256B Flit for "CXL 256B Flit Mode"

当支持"CXL 256B Flit Mode"协议时,此模式是强制性的。它是Compute Express Link规范中定义的256B Flit模式的标准Flit格式,支持此Flit格式的主要目的是为了与仅支持标准256B Flit格式的供应商实现互操作性。协议层必须按照Flit格式在FDI上进行Flit传输,并在保留给Die-to-Die Adapter的字段上发送0。在UCIe上,不会使用Ack、Nak、PM和Link Management DLLP用于CXL.io。其他DLLP和Flit状态的定义遵循Compute Express Link规范中定义的相同规则和打包方式。协议层必须驱动DLP字节的部分内容来进行Flit_Marker分配;请参考第3.2.3节,了解有关如何驱动DLP字节的详细信息。图18显示了此模式的Flit格式。

对于此模式下的CXL.cachemem,FDI提供了一个lp_corrupt_crc信号,以在保证Viral封装的同时优化延迟。有关Viral封装的接口规则的详细信息,请参考第8.2节。

2.3 CXL 2.0 or "CXL 68B-Enhanced Flit Mode"

请参考Compute Express Link规范,了解有关CXL 2.0或"CXL 68B-Enhanced Flit Mode"的协议层消息和插槽格式的详细信息。每个协议都有两种可行的操作模式,这些模式在下面的子节中进行了定义。适配器会插入灰色字节。

2.3.1 Raw Mode for CXL 2.0 or "CXL 68B-Enhanced Flit Mode"

这种模式是可选的。它的预期用途是用于传输"CXL 64B Flit Mode"协议的UCIe Retimers。这种模式的一个示例用法是,当CPU和I/O设备位于不同的机架/底盘中,并通过使用OffPackage Interconnect的UCIe Retimer进行连接时。重传和CRC由协议层处理。所有的64个字节都由协议层填充。图14展示了这种模式的传输示例。

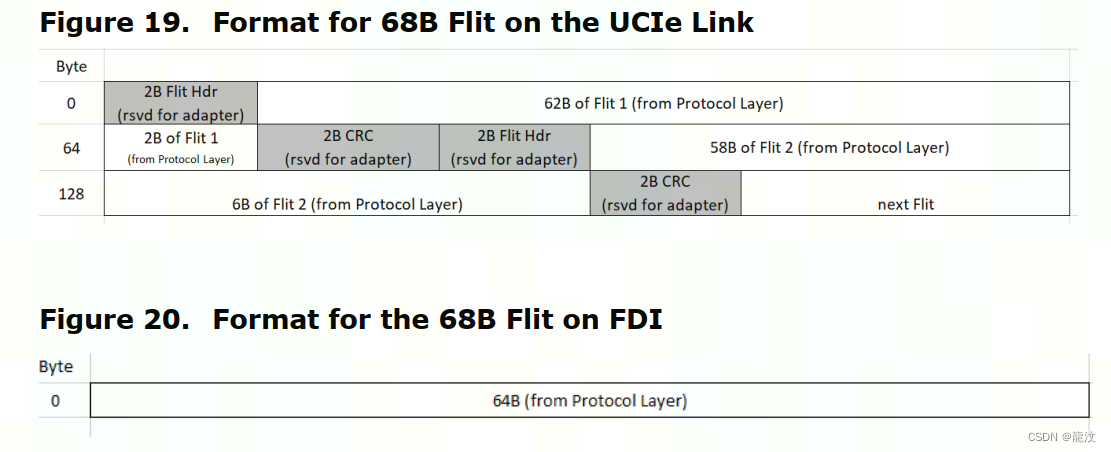

2.3.2 Flit Mode: 68B Flit for CXL 2.0 or "CXL 68B-Enhanced Flit Mode"

当协商使用CXL 2.0或"CXL 68B-Enhanced Flit Mode"协议时,这种模式是强制的。它遵循计算扩展链路规范中定义的相应的68B Flit格式,并支持此Flit格式的主要动机是为了与仅支持基线CXL格式的供应商实现互操作性。协议层在FDI上呈现Flit的64B(不包括协议ID和CRC),而Die-to-Die适配器则插入2B的Flit头和2B的CRC,并执行所需的字节移位,以按照图19所示的格式排列Flits。

在此模式下,不使用PM、Ack或Nak DLLP来进行CXL.io。对于CXL.io,信用更新和其他剩余的DLLP按照计算扩展链路规范中定义的方式通过Flits传输。对于CXL.io,发射器在协议层不得实现重传(因为重传由适配器处理)。为了保持帧结构的一致性,CXL.io的协议层仍必须将LCRC字节驱动为固定值0,接收器必须忽略这些字节,不发送任何Ack或Nak DLLP。

对于CXL.cachemem,Flit中的"Ak"字段被保留,不使用重传Flits(因为重传由适配器处理)。链路初始化始于发送INIT.Param Flit,无需等待任何接收到的Flits。如果适用,病毒封控必须在68B Flit Mode的协议层内处理。

2.4 Streaming protocol

如果不打算向远程链路使用和协商任何PCIe或CXL协议,那么这将使用默认协议。在UCIe规范中定义了一种单一的操作模式,但允许供应商定义扩展。

换句话说,如果没有选择使用PCIe或CXL协议,那么默认的协议将是UCIe协议。UCIe规范为该协议定义了一种操作模式,但允许供应商进行扩展以满足特定需求。这意味着供应商可以根据自己的要求对UCIe协议进行扩展,以实现更多的功能或适应特定的应用场景。

2.4.1 Raw Mode for Streaming protocol

这种模式是流式协议支持的强制要求。协议层将填充所有64个字节。图14展示了在x64模块上通过物理链路进行传输的这种模式。

这意味着在流式协议支持中,协议层将使用64个字节的数据进行传输。这些数据由协议层填充,并通过物理链路进行传输。图14可能显示了该模式下的数据传输示意图,以展示数据在物理链路上的传输方式和布局。

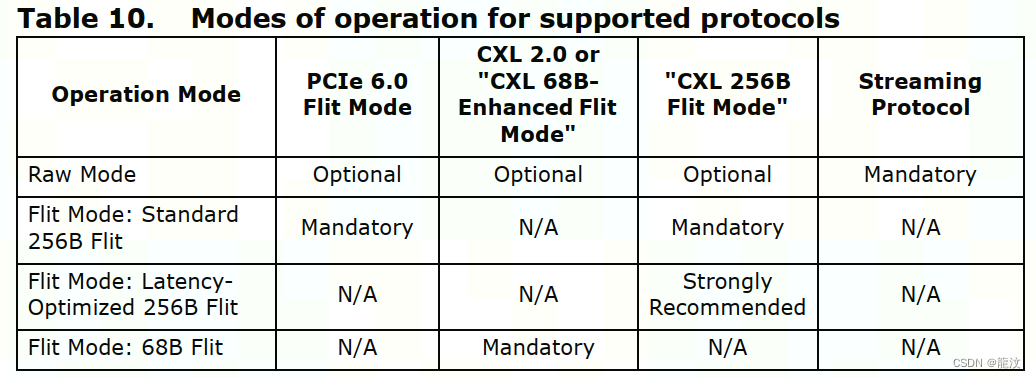

2.5 Summary of supported modes

每个协议的不同操作模式在表格10中总结。它们的格式细节在第3.0章中定义。

4629

4629

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?