UCIe全称Universal Chiplet Interconnect Express,协议定义了提供高带宽,低延迟,高功耗效率,低成本的芯粒(Chiplet)或者简称Die间互联的协议。

针对日益增长的高性能计算,存储,存算等领域的高带宽低延迟需求,UCIe协议定义的通用互联协议。各芯片Die间可以通过UCIe接口实现数据互通信。

目前UCIe标准规范已经进化到2.0版本。增强了链路管理,调试和测试的需求,也增加了UCIe-3D互联的支持,进一步降低了pitch间距。

作为标准接口协议,UCIe 互联协议支持多种上层协议及封包模式,包括PCIe,CXL Transaction Layer以及Stream数据模式(RAW Mode)。

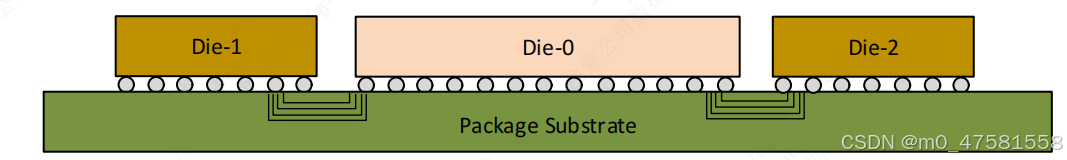

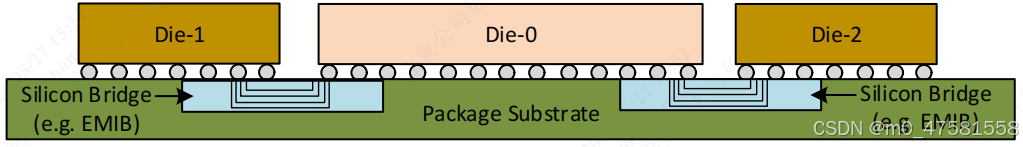

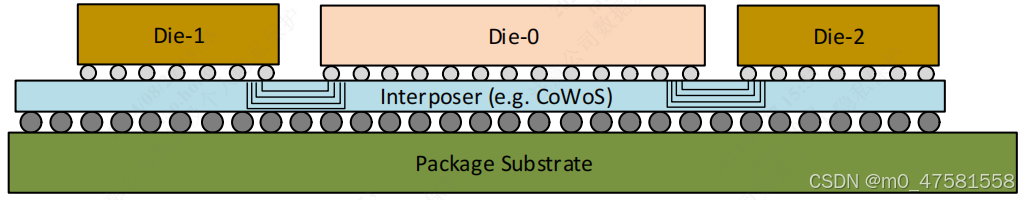

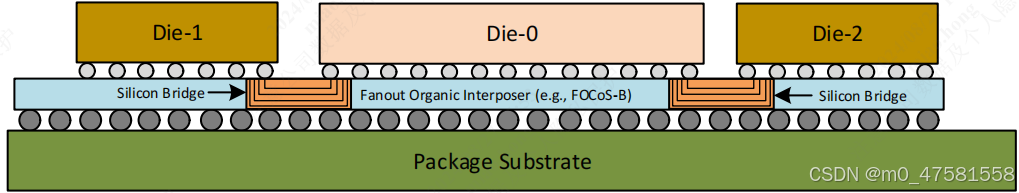

UCIe标准协议展示了典型的UCIe package内互联的应用:

UCIe可以用于CPU/CPU之间,CPU/Accellerator之间以及CPU和IO Die之间的互联。

在使用Retimer的情况下,UCIe协议也可以基于CXL2.0 Retimer 实现off package,如PCB或者光互连。

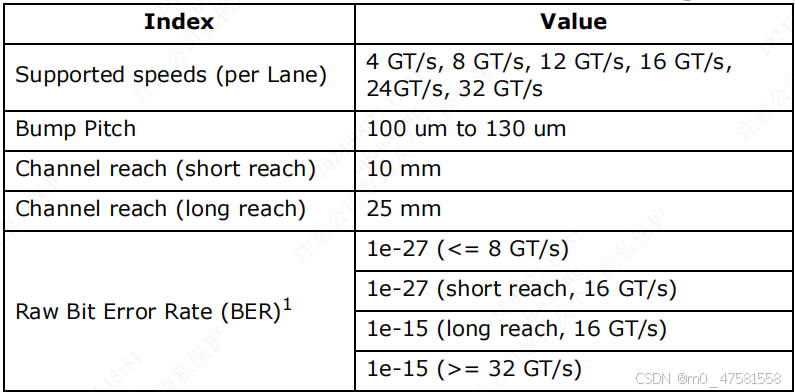

UCIe Spec 版本1支持标准封装(2D封装)和高级封装(2.5D封装)模式。

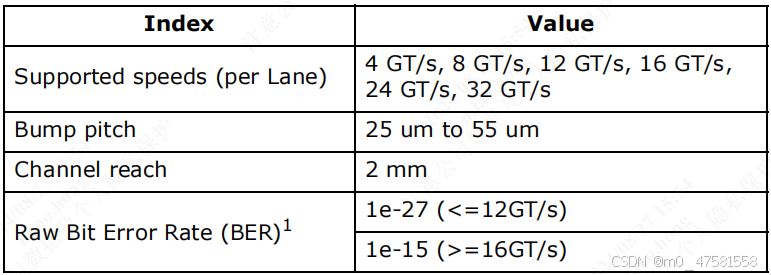

标准UCIe封装模式可以支持从4Gbps到32Gbps per lane的速率,Bump Pitch支持100um到130um,支持short channel reach 10mm和long chanel reach到25mm的封装。相对低速下BER要求1e-27,高速要求1e

1767

1767

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?