本章开始主要介绍UCIe协议第四章,物理层逻辑定义和规范。

如其他的通信协议一样,接口的物理层包含两个部分,逻辑子层和电气子层。其中逻辑层主要负责:

1.定义接口信号和时序

2. 定义发送端如何将上层数据分发到各个物理通道以及接收端如何把从各个通道收到的数据恢复成byte stream(Flit)。

3. Broken Lane的repair和remap。

4. 链路初始化,训练(training)和电源状态管理/切换。

5. 扰码Scrambling和training sequence的产生。

6. Lane Reversal和ID映射。

7. 宽度和速度协商和动态切换。

本节继续从上一节内容,描述链路初始化和training

链路初始化和链路状态训练

Note: 协议规定每个链路状态的超时Timeout时间为8ms(RESET和TRAINERROR除外),任何状态的超时(TIMEOUT),状态均需要转换到TRAINERROR,其中timeout counter在Sideband收到STALL 的时候需要reset 0.

在每次链路linkup的时候, training都是必须要的流程。除此以外,还有以下几种方式触发training:

1. 软件向 UCIe link Control的Start UCIe Link Training bit写1.

2. Adapter 通过RDI接口触发Link Training

3. Sideband INIT pattern。

如果链路在尝试多次training均失败(次数是implementation specific的)之后,状态transition 到RESET,等待后续软件或其他方式重新触发Link Training。并且针对软件或RDI触发的training,或者由于Timeout导致的link up 切换到link down,在Training失败后,物理层需要在RDI接口上报告Fatal Error。

Training 基本操作

Transmitter对每条Lane均发起数据/时钟对齐测试

操作序列为:

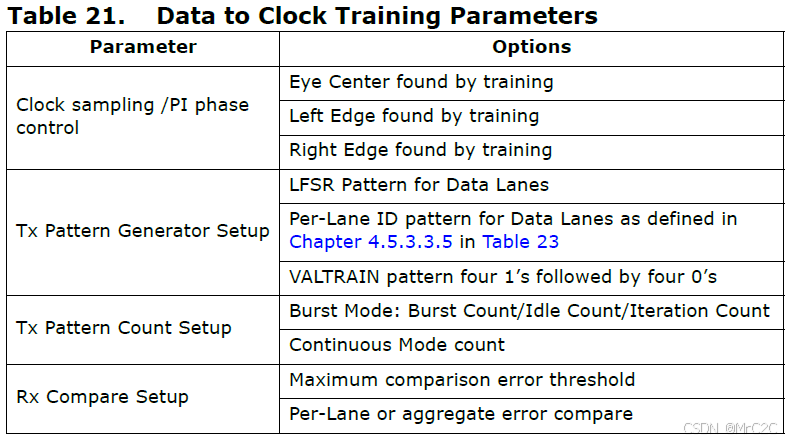

1. Transmitter 设置data和clk关系的training参数。

Transmitter发送sideband message {START Tx INIT D to C Eye Sweep Req}包含了上图中的data to clock parameters,并等待对端UCIe的response。对端接收到Requestor sideband message之后,需要配置自己使用requestor发过来的参数,用来在后面的步骤去check mainband的data to clock training或者叫test pattern(上一节描述过的test pattern generator,PRBS23)。并且回复一个Sideband message {Start Tx Init D to C eye sweep resp}

2. UCIe链路Tx 复位mainband的LFSR(pattern generator),并且发送sideband message {LFSR clear error req}. 对端收到msg之后,同样也需要复位自己的LFSR,同时复位本地的error counter和status。并且通过sideband发送{LFSR clear errorr resp} msg。

3. UCIe链路Tx在“Pattern count setup” cycle之后,开始从mainband发送pattern(Tx Pattern Generator Setup中定义的pattern)。

4. UCIe链路对端的Rx,根据Rx Compare Setup中的参数,开始LFSR pattern的比较和check。

5. UCIe链路Tx 发送 {D to C results Req},请求对端返回compare记录到的链路test结果。对端在收到这个request之后,停止比较,并通过sideband返回给requestor,自己记录到的test compare到的error, {D to C Results log}

6. UCIe停止mainband发送测试pattern,并通过sideband发送message {End Tx Init D to C Point test req}, 对端通过sideband 通道发送响应packet {End Tx Init D to C test resp}。 并且链路双方在完成最后的resp packet之后,链路进入Electrical IDLE状态。

Transmitter发起Data to Clock Eye width Sweep training

在完成data to clock test之后,transmitter在每一条Lane上发起data to clock Eye sweep,此操作可以通过遍历data 和clock之间的不同相位下正确/错误率,可以让上层选择最好的data/clock采样相位,同时也可以以此check 系统信号的margin。此操作的序列为:

1. UCIe (假设链路A端) 发送sideband message {Start Tx Init D to C Eye Sweep req} 到UCIe 对端(假设链路B端),并且等待B端回复的response。消息内容为Table-21内定义的链路参数。链路B端在接收到这些参数后,发发送response message {Start Tx Init D to C Eye sweep resp}。UCIe链路接收端必须enable pattern comparison(数据pattern比较器)功能,用来支持后无的sweep过程中将mainband收到的数据和local LFSR产生的数据进行比较。

2. UCIe (链路A端)复位自己的mainband transmitter LFSR (pattern generator)并通过sideband 发送{LFSR clear error req}告知链路B端清除它的LFSR error checker状态和counter,以及复位自己的LFSR。并且向链路A端发送{LFSR clear error resp} sideband message。

3. A端根据自己的Tx Pattern generator的设置,通过transmitter mainband 向B端发送测试数据。发送数量为“pattern count setup”的测试pattern。

4. B端接收A端发送来的测试数据,并和本地LFSR产生的数据进行对比,并log记录比较结果。

5. A端发送sideband message {D to C result Req}查询B端的比较结果,B端停止pattern的比较并回复message {D to C result log}。

6. A端根据调整PI phase,并继续步骤2-5的测试过程 (具体PI phase每个step的时间长短由implementation指定)。A端遍历并找到所有能通过测试的UI phase区间。

7. 完成后,A端停止测试并发送{End Tx Init D to C eye sweep req} ,B端回复{End Tx Init D to C eye sweep resp}。并将信号置Elec Idle。

Receiver发起Data to Clock point training

和Transmitter发起Data to clock point training步骤类似,UCIe定义Receiver也可以通过发起sideband message {Start Rx Init D to C point test req}来向对端的Tx请求对某一组参数的training。

1. A端receive发起{Start Rx Init D to C point test req} sideband message 并启动pattern comparison功能。并等待B端{Starts Rx Init D to C point test resp}.

2. B端复位自己的mainband transmitter LFSR,并发送{LFSR clear error req} sideband message. A端复位local LFSR并复位自己的comparison error checker状态和counter。并发送{LFSR clear error resp} sideband message。

3. B端根据{test req}内发送的pattern generator setup和pattern count setup 通过mainband发送测试pattern。

4. A端接收B端发送来的LFSR数据,和Local的LFSR数据做比对,并记录checker log。

5. B端测试pattern发送完成后,发送sideband 消息{Rx Init D to C Tx count done req}. A端接收到消息后停止比较器,发送resp 消息{Rx Init D to C Tx count done resp}. 此时A端可以使用记录到的测试log数据。

6. A端发送消息{End Rx Init D to C point test req}通知B端结束测试。 B端收到后发送resp消息{End Rx Init D to C point test resp}.

Receiver 发起Data to Clock Eye Width Sweep training

此步骤和Transmitter发起eye sweep类似,接收端发起eye width sweep的步骤如下:

1. Receiver (A端)发起{Start Rx Init D to C eye sweep req} sideband消息来发起sweep请求。并等待B端回复resp 消息{Start Rx Init D to C eye sweep resp}.

2. B端复位自己的LFSR并发送{LFSR clear error req}, A端收到后复位/清除自己的LFSR和error log信息。并发送{LFSR clear error resp} sideband 消息。

3. B端根据第一步协商的“Tx pattern generator setup”和"pattern count setup"参数,发送测试pattern。

4. A端接收并比较测试数据。记录测试结果。

5. B端发起{Rx Init D to C result Req}, A端发起{Rx Init D to C result Resp} 将自己的检查结果反馈给B端。A端根据结果决定测试pass or fail。

6. B端调整forward clock PI phase 并发起下一轮测试,持续循环步骤2-5,记录pass的PI phase range。sweep pattern和range是implementation specific。

7. 完成所有的PI phase sweep后,B端发送{End Rx Init D to C eye sweep req}消息,并等A端回复{End Rx Init D to C eye sweep resp}。并结束training过程。

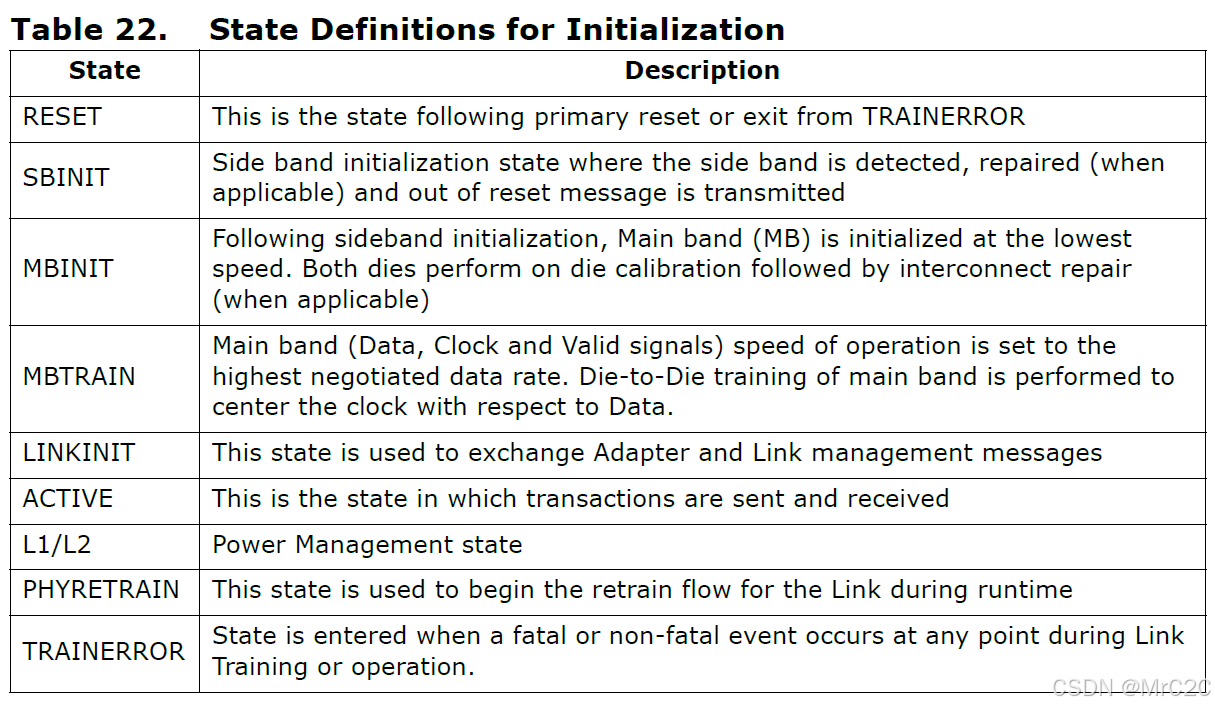

链路训练状态机(Link Training State Machine)

链路训练状态

RESET

复位状态,为链路上电初始化的默认状态,在此状态需要准备上电必要的操作,例如sideband clock开始运行,mainband开始运行

SBINIT

sideband 通道的初始化,包括CK/DATA的协商,advance package的sideband repair操作等。

MBINIT

Mainband的初始化,使用sideband message通道协商链路参数(速率,时钟相位等), mainband repair,calibration等操作。

MBTRAIN

MBTRAIN用来设置链路速度(最大速度取决于MBINIT状态时两端交互过的链路双方的support的速度中的较慢者),进行时钟和数据的phase shift(中间对齐),高速场景下的calibration操作(Rx clock校准,Tx/Rx de-skew),以及链路repair操作等。

LINKINIT

此状态用于Die2Die adapter完成RDI接口的link management。

ACTIVE

链路link up,正常工作状态。

L1/L2

UCIe的两个低功耗状态,此状态均由Adapter 从RDI发起,request进L1或L2.

PHYRETRAIN

链路重新训练状态(类似于Pcie的recovery状态)。

TRAINERROR

由于链路发生了Fatal或者non-fatal的问题,需要重新进入reset状态前,链路可以进入TRAIN ERROR状态。

6563

6563

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?