项目介绍

项目目标简单来说,就是基于ZCU102 FPGA平台,通过FMC把FMCJESDADC1子板上的2路ADC数据采集到FPGA内部,并对采集到的数据做解调处理,恢复出基带信号。

需实现的关键功能:

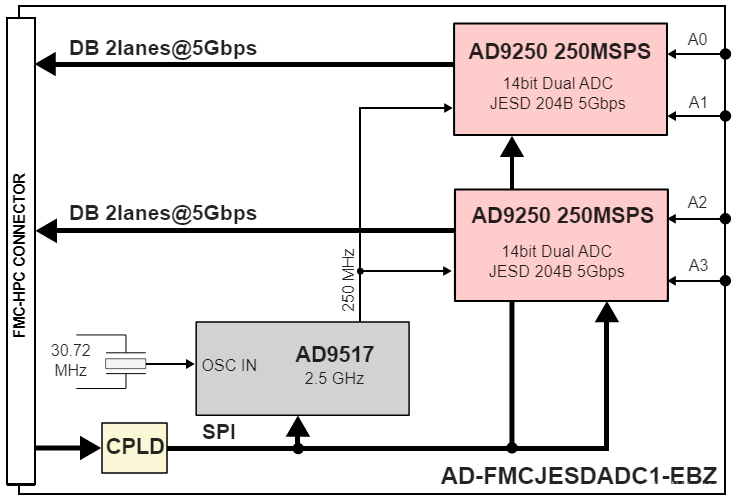

(1)在FPGA上实现SPI Master功能,并通过其完成ADC子板上时钟芯片(AD9517-3)及2路ADC芯片(AD9250)的配置。

(2)实现JESD204b接口,并与AD9250完成链路建立和数据接收,重新拼接恢复出ADC数据。

(3)将恢复的ADC数据进行混频及滤波处理,恢复出基带信号。

ZCU102 FPGA介绍

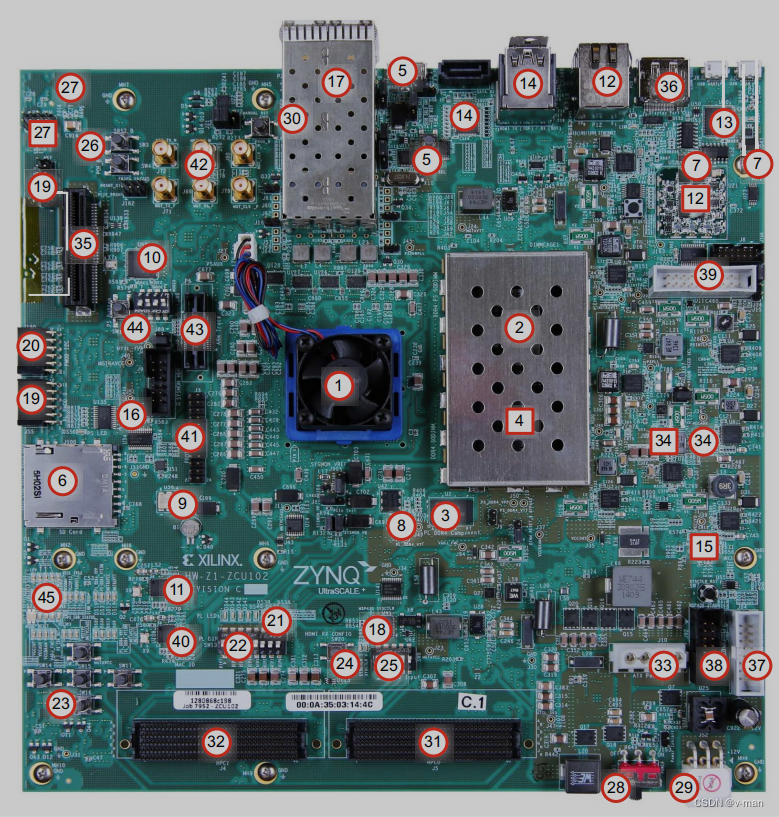

如下图是ZCU102 FPGA示意图,本项目中所使用资源及接口有:

- ⑦位置的调试串口

- ⑥位置的SD卡

- 23位置的LED,用于指示内部逻辑状态

- 31位置的HPC0 FMC接口,用于对接FMCJESDADC1

FMCJESDADC1介绍

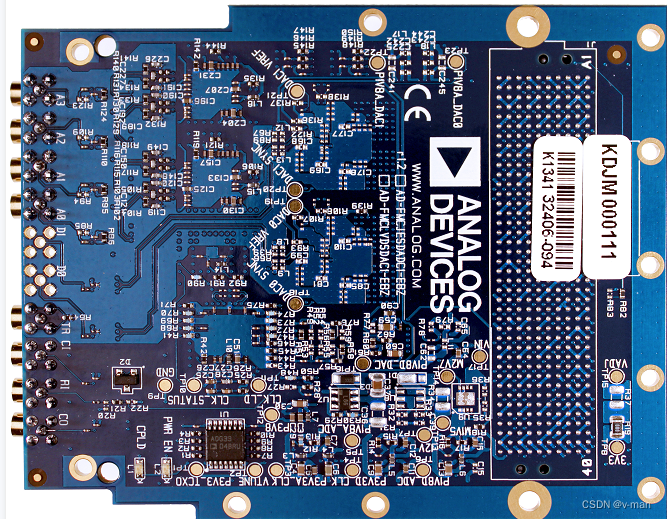

FMCJESDADC1子板具体:

- AD9175-3 时钟芯片,用于提供ADC采样时钟及JESD SERDES参考时钟、JESD控制器主工作时钟。

- 2颗AD9250 ADC芯片,高达250MHz的采样率,支持14bit采样位宽。

可用资源

-

FMCJESDADC1子板资料

AD-FMCJESDADC1-EBZ Zynq Quick Start Guide [Analog Devices Wiki]

-

AD9715-1芯片资料

https://www.analog.com/media/en/technical-documentation/data-sheets/ad9517-3.pdf

-

AD9520芯片资料

https://www.analog.com/media/en/technical-documentation/data-sheets/AD9520-3.pdf

561

561

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?