(1)为什么要分阶段?

如前篇所述,终极目标是:通过纯FPGA控制把FMCJESDADC1子板上的2路ADC数据采集到FPGA内部,并对采集到的数据做解调处理。

但客观现实是:

- FMCJESDADC1上的AD9517时钟芯片、AD9520 ADC芯片及FPGA的JESD接口都没有调试过,没有现成的配置。调试过程必然需要不断修改AD9517、AD9520 、JESD各种配置。如果将配置固化在RTL中,必然调试效率很低。

- ADI参考工程的上述配置都通过软件完成,软件各种封装又很厚,需要花时间消化。且最终项目的目标是纯RTL来控制,并不需要在CPU上跑软件。

基于上述考虑,本项目分2个阶段完成。

(2)使用PetaLinux辅助调试阶段

本阶段的方案是:使用ZYNQ PS系统并允许Petalinx系统,将AD9517、AD9520、JESD控制器当做PS系统的外设。通过Linux串口即可下读写指令即可完成对AD9517、AD9520、JESD控制器的配置和状态回读,得到配置脚本。

这种方式极大提高调试效率且门槛最低。

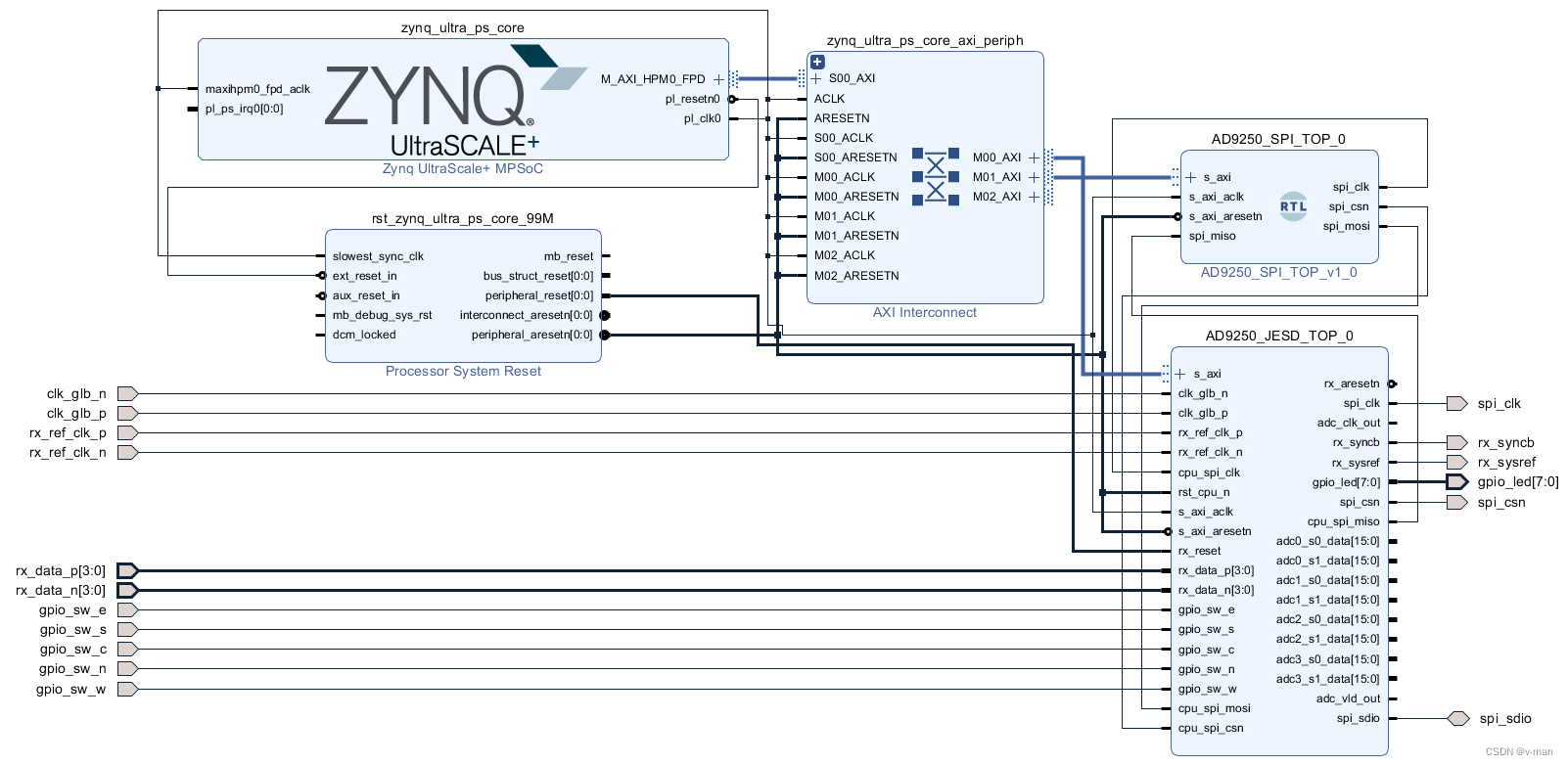

本阶段的系统架构如下:

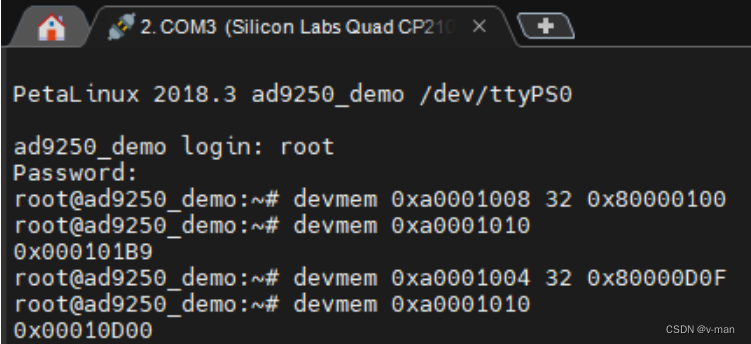

读写调试示例:

(3)使用纯RTL控制阶段

阶段(2)是为了得到所有正确的配置和流程,但最终的目标我们并不需要依赖这个处理器及配置脚本,而是纯RTL控制即可工作,这样对FPGA平台的依赖和资源使用最少。

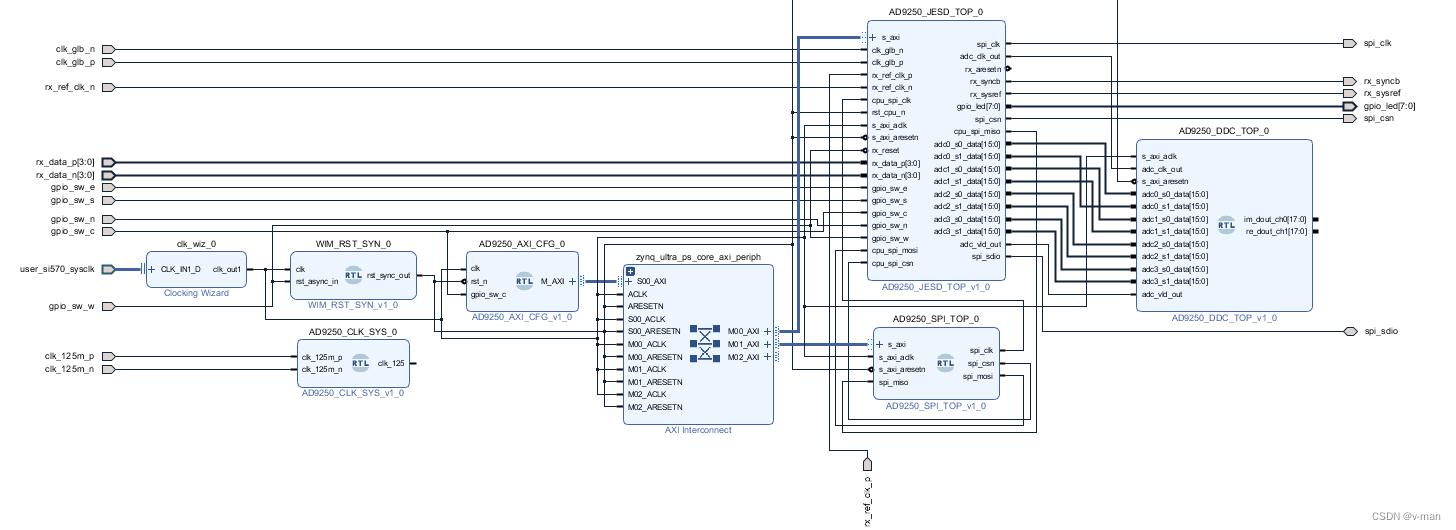

本阶段将配置脚本固化封装为一个AXI Master,只需要将该AXI Master替换掉原来PS系统的AXI Master端口。这便于移植到其它FPGA平台。

本阶段的系统架构如下:

589

589

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?