一·、设计要求

利用试验箱上的八个发光二极管和最上端的拨码开关,实现如下功能:

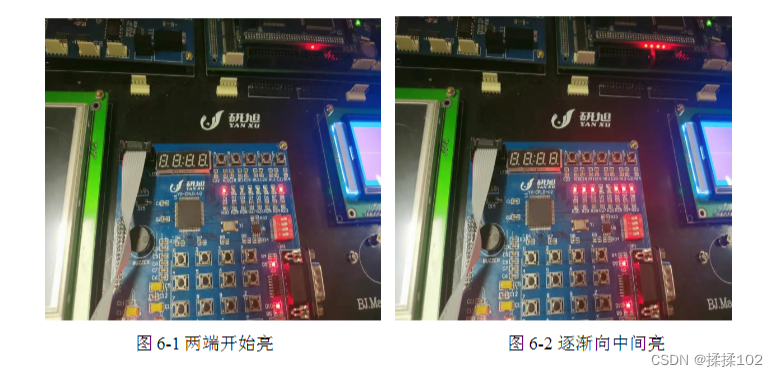

功能一: 拨码开关拨到高电平由两端向中间,每次点两个灯,全亮后,从左向右一次熄灭,循环上述过程,变化速度1s/一次

功能二: 拔码开关拨到低电平全亮, 从右往左依次熄灭,从左往右依次点亮, 循环上述过程, 变化速度1S/一次

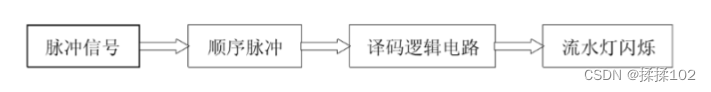

二、设计总体思路

1.设计原理:

CPLD 时钟端口接来自外部晶振产生的6MMMM的时钟信号, 通过对6MMMM 时钟方波上升沿或者下降的计数(3000000),产生一个频率为1hz hz 的方波;以方波信号驱动process 进程根据当前状态驱动八个发光二极管以要求的顺序点亮。

2.设计思路采用CPLD芯片以及外围电路实现。

系统总体包括 最小系统、时钟输入 、LED灯显示。时钟输入后,并在CPLD中译码输出,8个LED灯就显示COLD中设置的模式。实现较为简单 ,功能模块在CPLD里用Verilog HDL 编程实现。可以任意 功能 扩展,增加LED组数,修改方便,很容易在QuetusII中仿真系统工作时序。系统框图如下:

三、系统核心模块设计实现

library ieee;

use ieee.std_logic_1164.all;

entity herong is

port (

clk6m: in std_logic;

reset: in std_logic;

control : in std_logic;

q: out std_logic_vector(7 downto 0) );

end entity;

architecture bhv of herong is

signal clks: std_logic;

begin

process(clk6m)

variable cnt :integer range 0 to 3000000 :=0;

begin

if (clk6m'event and clk6m = '1') then

cnt := cnt + 1;

if (cnt = 3000000) then

clks <= not clks;

cnt := 0;

end if;

end if;

end process;

process(clks, reset)

variable current_stat : integer range 0 to 15 := 0;

variable flag : std_logic:= '0' ;

begin

if (reset = '0') then

flag := '0'; current_stat := 0; q <= "00000000";

elsif (clks'event and clks = '1') then

if (control = '0' and flag = '1') then flag := '0';

current_stat := 0;

elsif (control = '1' and flag = '0') then

flag := '1';

current_stat := 0;

end if;

if (flag = '0') then

case current_stat is

when 0 => q<="01111110"; when 1 => q<="00111100"; when 2 => q<="00011000"; when 3 => q<="00000000"; when 4 => q<="10000000"; when 5 => q<="11000000"; when 6 => q<="11100000"; when 7 => q<="11110000"; when 8 => q<="11111000"; when 9 => q<="11111100"; when 10 => q<="11111110"; when 11 => q<="11111111"; when 12 => q<="11111111"; when 13 => q<="11111111"; when 14 => q<="11111111"; when 15 => q<="11111111";

end case;

current_stat := current_stat +1;

elsif (flag = '1') then

case current_stat is

when 0 => q<="00000001"; when 1 => q<="00000011"; when 2 => q<="00000111"; when 3 => q<="00001111"; when 4 => q<="00011111"; when 5 => q<="00111111"; when 6 => q<="01111111"; when 7 => q<="11111111"; when 8 => q<="01111111"; when 9 => q<="00111111"; when 10 => q<="00011111"; when 11 => q<="00001111"; when 12 => q<="00000111"; when 13 => q<="00000011"; when 14 => q<="00000001"; when 15 => q<="00000000";

end case;

current_stat:=current_stat+1;

end if;

end if;

end process;

end bhv;

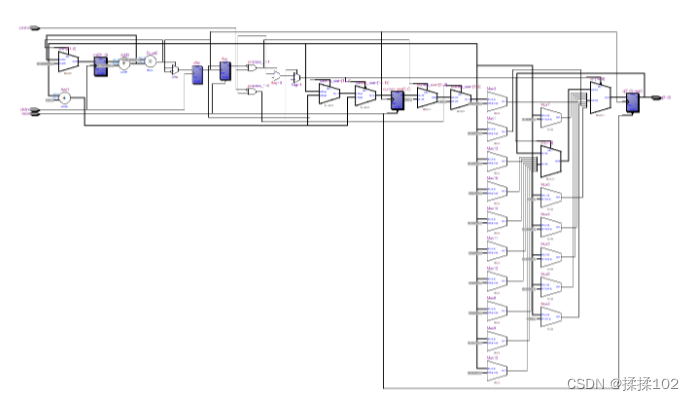

四、RTL级试图

五、管脚绑定

六、下载调试

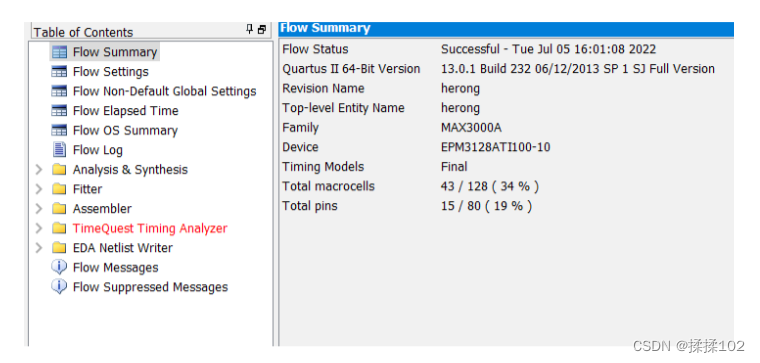

六、资源占用情况

8363

8363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?