代码:

module reg_jcq (

input wire clk,

input wire rst,

input wire [31:0] addr,

input wire [31:0] din,

input wire wr_en, // 写使能

/* input wire [31:0] write_data, // 写数据*/

input wire rd_en, // 读使能

/*input wire [31:0] data_read, // 读数据*/

output reg [31:0] data_out

);

// 定义基地址

parameter BASE_ADDRESS = 32'hC0000000;

// 内部寄存器数组

reg [31:0] registers [0:3]; // 4个32位寄存器

always @(posedge clk) begin

if (!rst) begin

// 复位时,将所有寄存器清零

for (integer i = 0; i < 4; i = i + 1) begin

registers[i] <= 32'h0;

end

end

else begin

// 根据地址和控制信号执行读写操作

case(addr)

BASE_ADDRESS + 0: begin

if (wr_en) begin

registers[0] <= din;

end

if (rd_en) begin

data_out <= registers[0];

end

end

BASE_ADDRESS + 4: begin

if (wr_en) begin

registers[1] <= din;

end

if (rd_en) begin

data_out <= registers[1];

end

end

BASE_ADDRESS + 8: begin

if (wr_en) begin

registers[2] <= din;

end

if (rd_en) begin

data_out <= registers[2];

end

end

BASE_ADDRESS + 12: begin

if (wr_en) begin

registers[3] <= din;

end

if (rd_en) begin

data_out <= registers[3];

end

end

default: begin

if (wr_en) begin

registers[0] <= din;

end

if (rd_en) begin

data_out <= registers[0];

end

end

endcase

end

end

endmodule

仿真代码:

module reg_jcq_test;

// 信号声明

reg clk;

reg rst;

reg [31:0] addr;

reg [31:0] din;

reg wr_en;

/*reg [31:0] write_data;*/

reg rd_en;

/*reg [31:0] data_read;*/

wire [31:0] data_out;

// 实例化被测试的模块

reg_jcq reg_jcq_inst (

.clk(clk),

.rst(rst),

.addr(addr),

.din(din),

.wr_en(wr_en),

/*.write_data(write_data),*/

.rd_en(rd_en),

/*.data_read(data_read),*/

.data_out(data_out)

);

// 时钟周期

parameter PERIOD = 10;

// 初始化

initial begin

clk = 0;

rst = 0;

addr = 0;

din = 0;

wr_en = 0;

/*write_data = 0;*/

rd_en = 0;

/* data_read = 0;*/

// 等待时钟稳定

#PERIOD rst = 1;

clk = ~clk;

// 开始写入数据

addr = 32'hC0000000; // 设置基地址

din = 32'h12345678; // 输入数据

wr_en = 1; // 写使能

/* write_data = 32'h12345678; // 写入的数据*/

#PERIOD wr_en = 0; // 等待一个时钟周期

// 开始读取数据

addr = 32'hC0000000; // 设置基地址

rd_en = 1; // 读使能

#PERIOD rd_en = 0; // 等待一个时钟周期

//

addr = 32'hC0000004; // 设置基地址

din = 32'h12346666; // 输入数据

wr_en = 1; // 写使能

/* write_data = 32'h12346666; // 写入的数据*/

#PERIOD wr_en = 0; // 等待一个时钟周期

//

addr = 32'hC0000004; // 设置基地址

rd_en = 1; // 读使能

#PERIOD rd_en = 0; // 等待一个时钟周期

// 显示读取的数据

$display("Read data: %h", data_out);

// 仿真结束

$finish;

end

// 时钟生成

always #((PERIOD / 2)) clk = ~clk;

endmodule

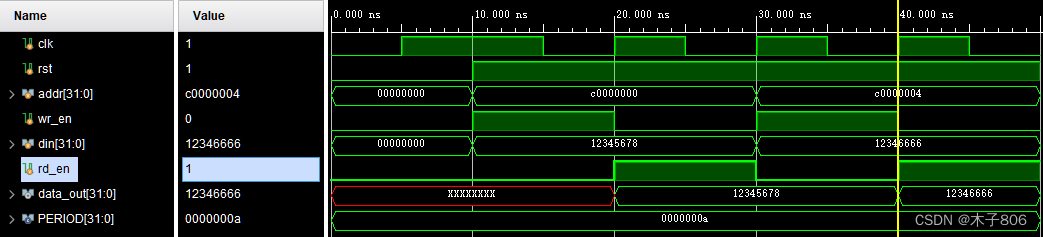

仿真波形:

是一个比较基础的寄存器,写的不太好希望大家指正,感谢观看

852

852

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?