现代逻辑设计中,时序逻辑设计是核心,而寄存器又是时序逻辑的基础,下面将介绍几种常见的寄存器的Verilog设计代码供初学者进行学习理解。

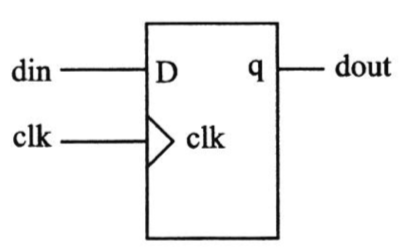

1、简单寄存器

基本寄存器

module dff(clk, din, dout)

input clk;

input din;

output dout;

reg dout;

always @ (posedge clk)begin

dout <= din;

end

endmodule

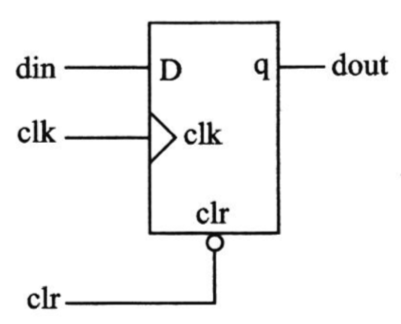

2、异步复位寄存器

异步复位寄存器

module dff(clk, rst_n, din, dout);

input clk;

input rst_n;

input din;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n)begin

if(! rst_n)dout <= 1'b0;

else dout <= din;

end

endmodule

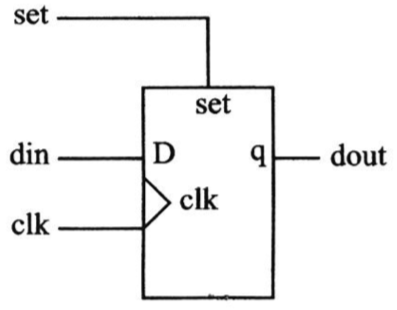

3、带异步置位的寄存器

异步置位寄存器

module dff(clk, set, din, dout);

input clk;

input din;

input set;

output dout;

reg dout;

always @ (posedge clk or posedge set)begin

if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

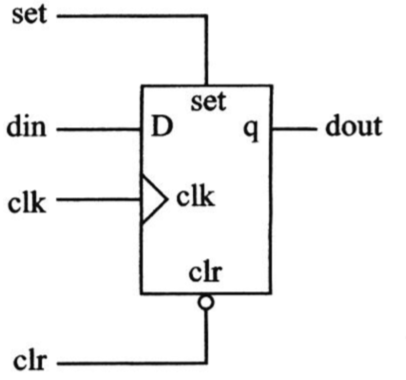

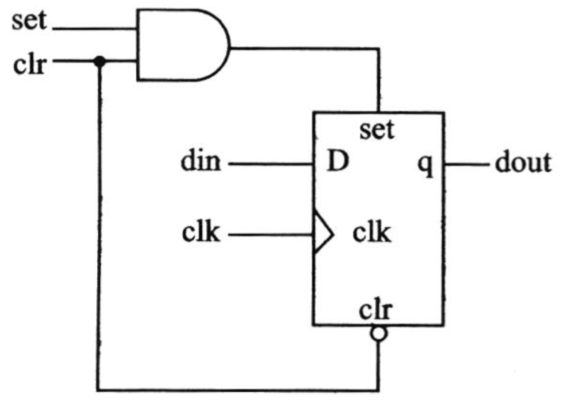

4、既带异步复位又带异步置位的寄存器

异步复位和置位寄存器

异步复位和置位寄存器(复位优先级高)

module dff(clk, rst_n, set, din, dout);

input clk;

input din;

input rst_n;

input set;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n posedge set)begin

if(! rst_n) dout <= 1'b0;

else if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

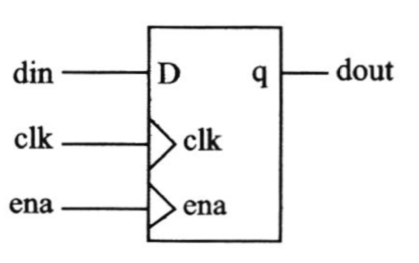

5、同步使能功能的寄存器

带同步使能的寄存器

module dff(clk, ena, din, dout);

input clk;

input din;

input ena;

output dout;

reg dout;

always @ (posedge clk) begin

if(ena) dout <= din;

end

endmodule

910

910

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?