·前言

课程需要简单设计一个加法器,需要使用VerilogHDL,下面以模拟一个加法器介绍使用vivado过程。

·创建新工程

create project

设置工程文件名以及路径(路径名中不能包含中文)

选择FPGA芯片(根据自己情况选择)

Add or create design sources

Create File

选择文件类型Verilog,输入文件名

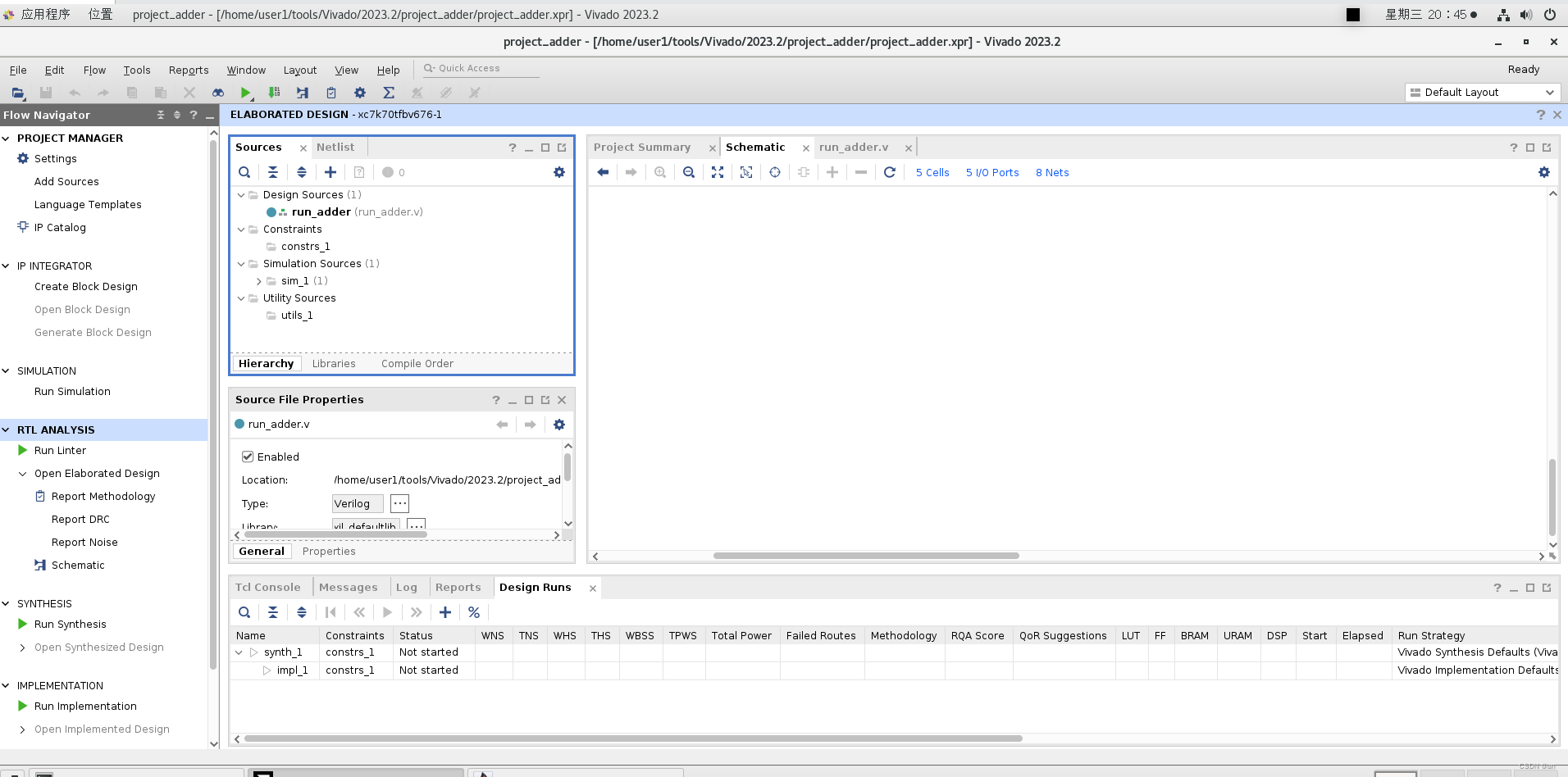

完成上述步骤之后,点击Add Source,进入之后创建自己的文件。完成之后如下:

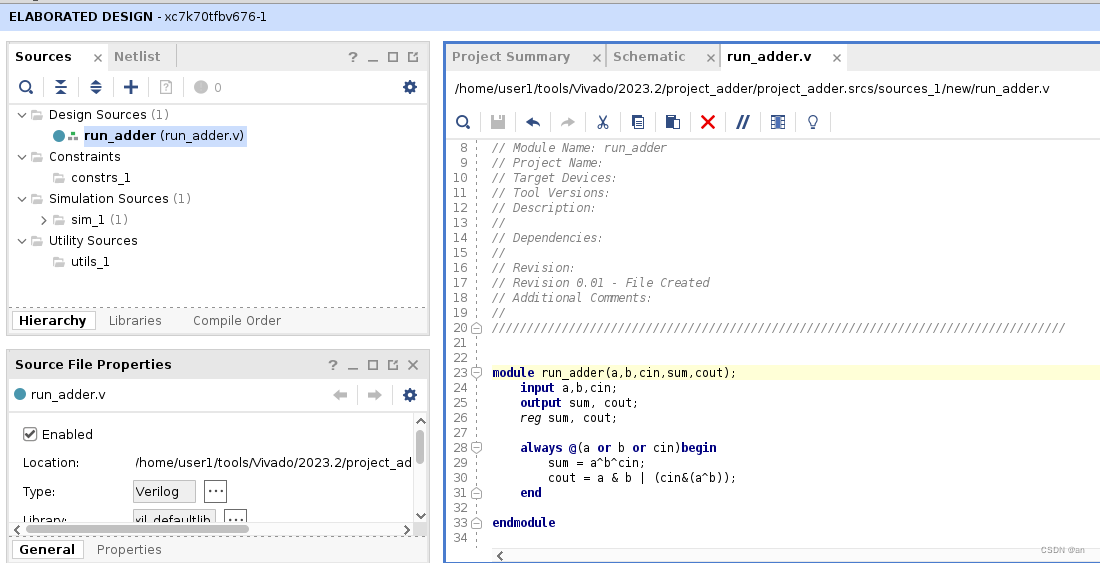

·编辑run_adder.v文件,直接上图:

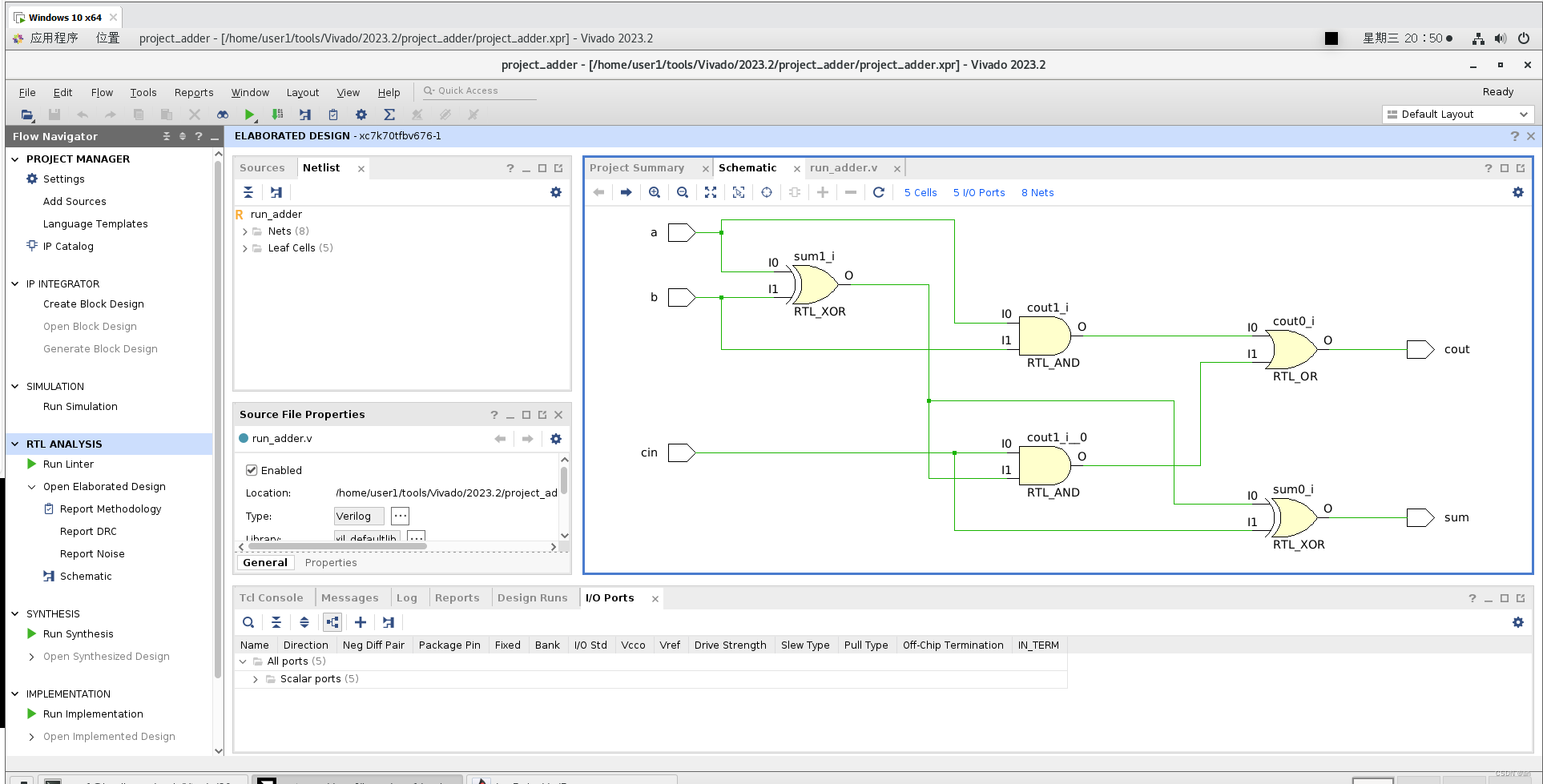

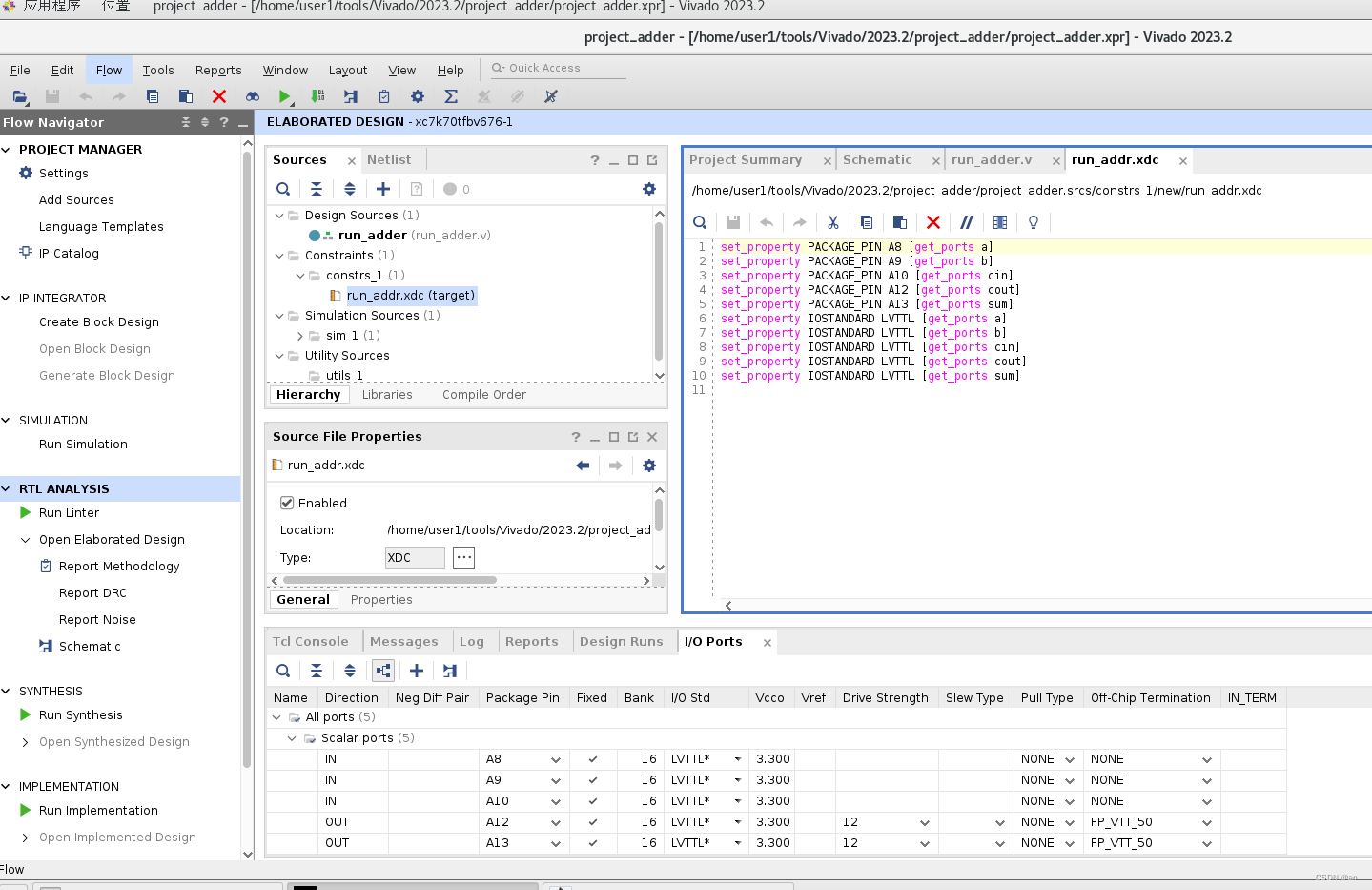

·添加管脚约束,点击Open Elaborated Design,然后点击上方菜单栏Window下的I/O Ports

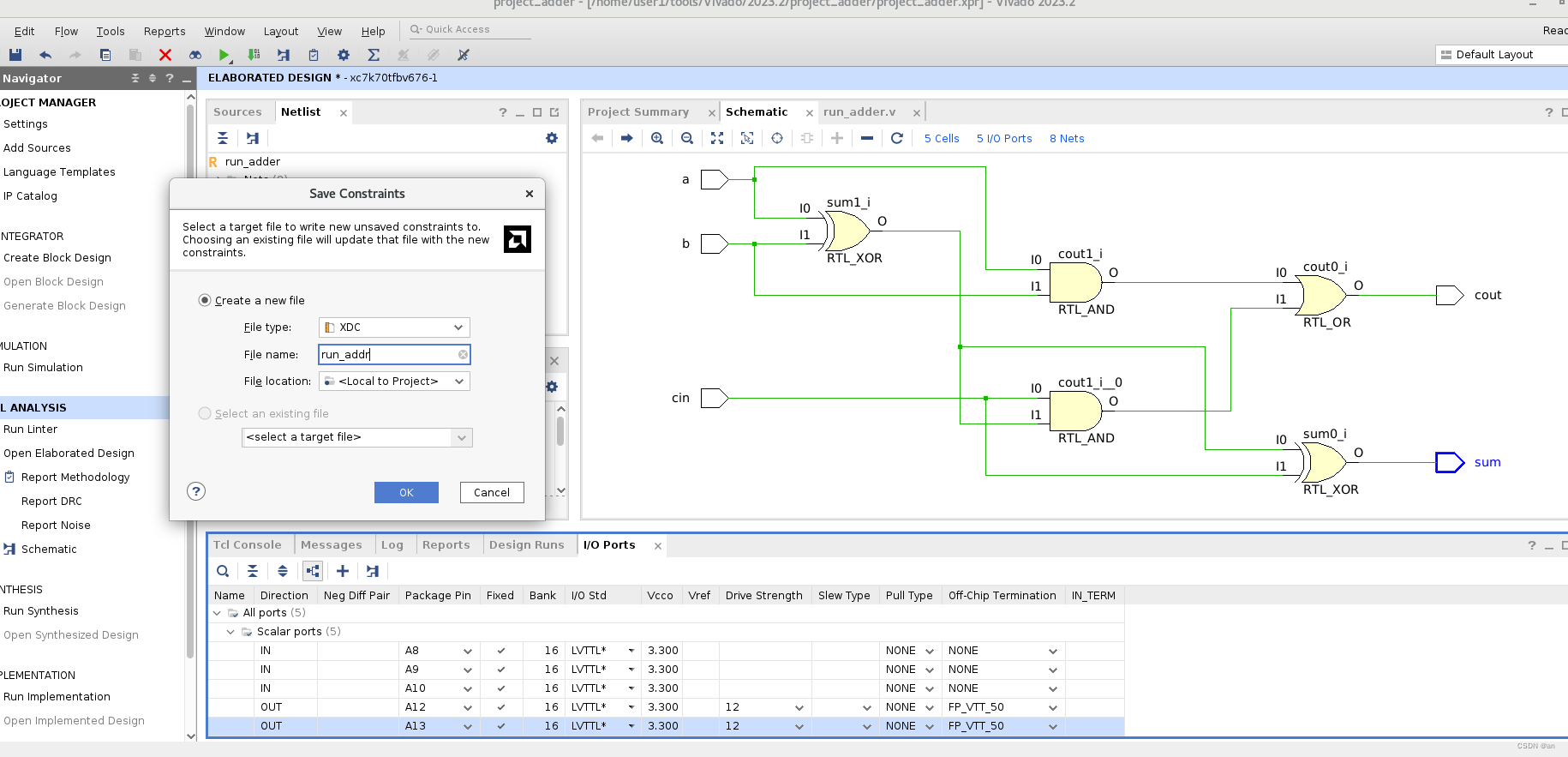

配置Ports信息:

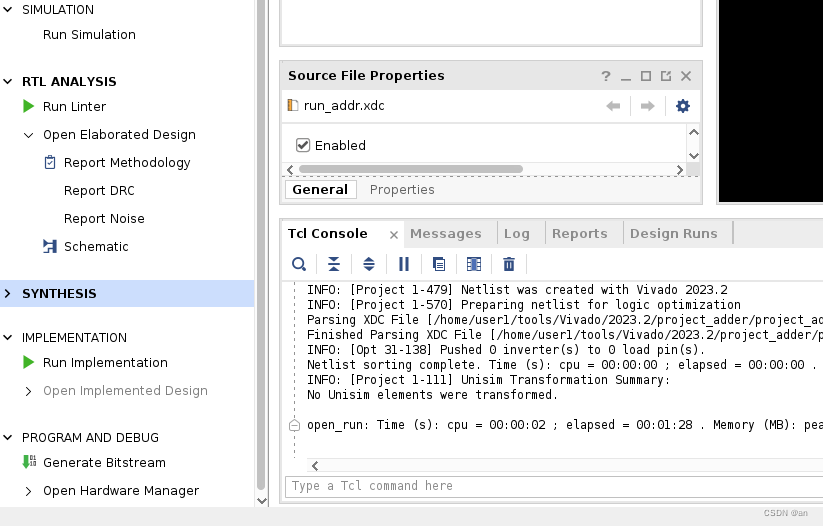

下图是刚刚生成的run_addr.xdc文件:

·时间约束

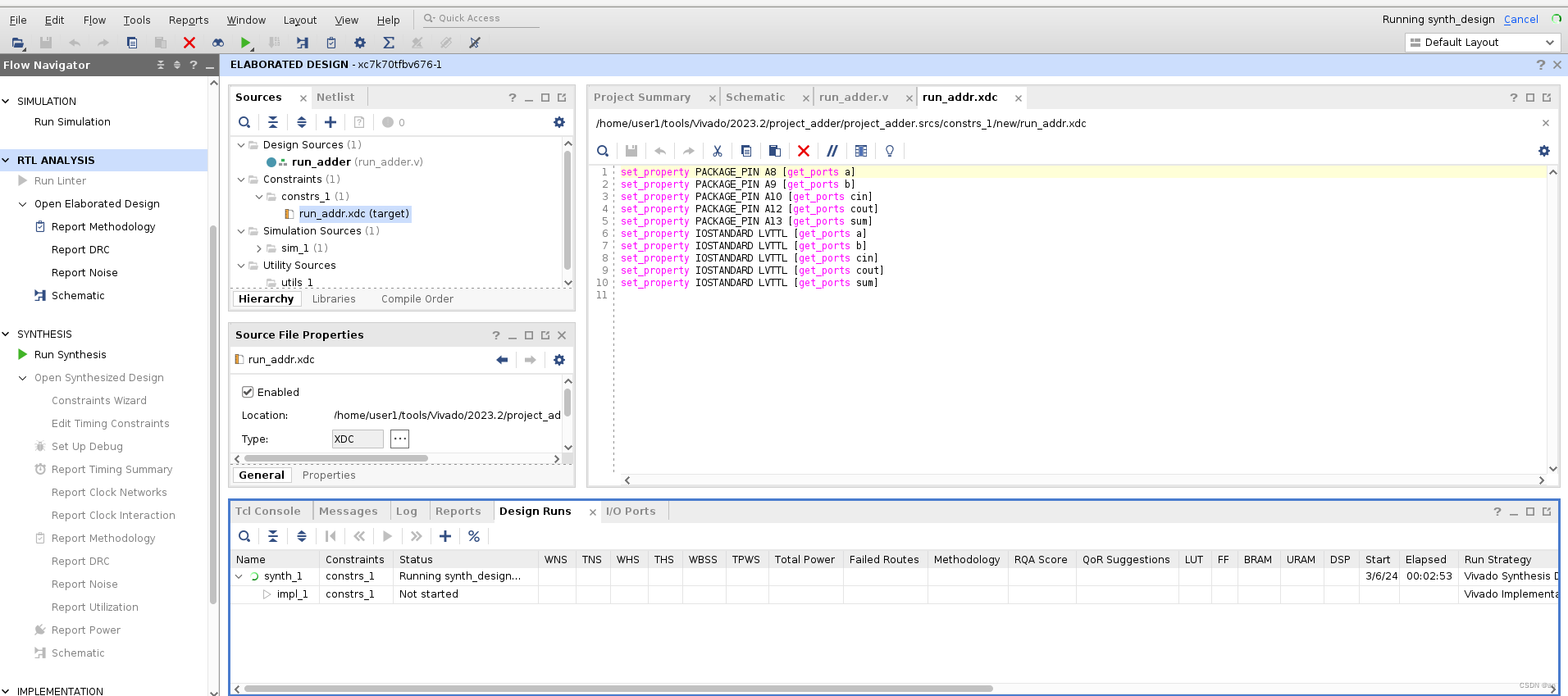

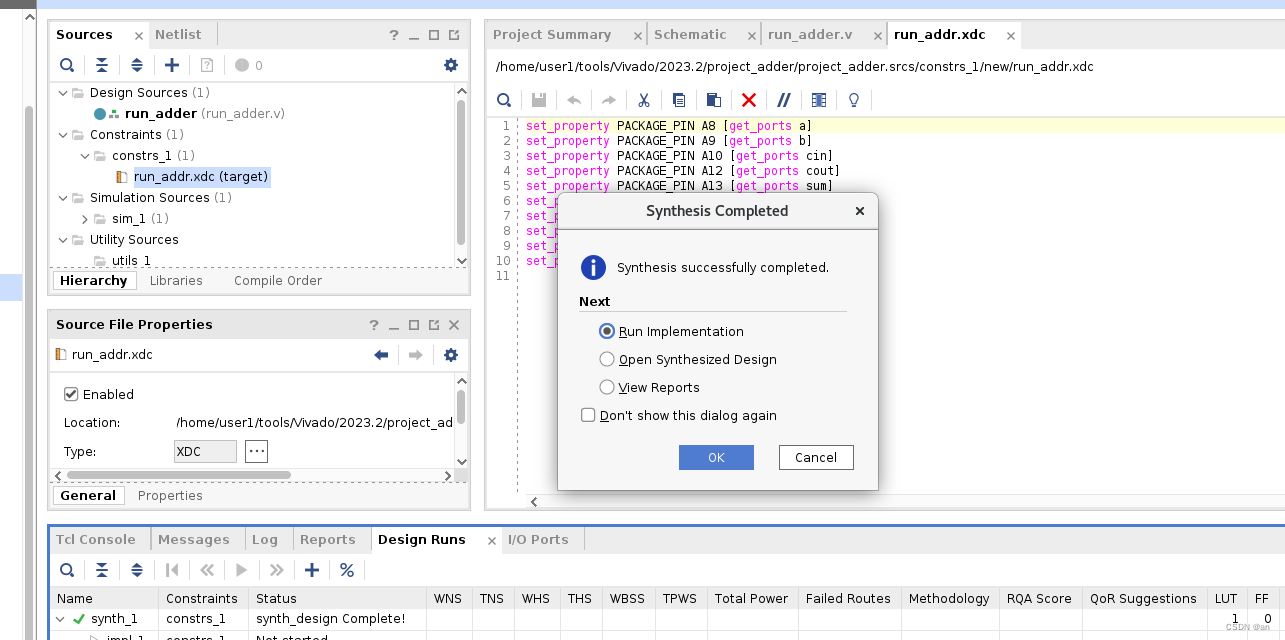

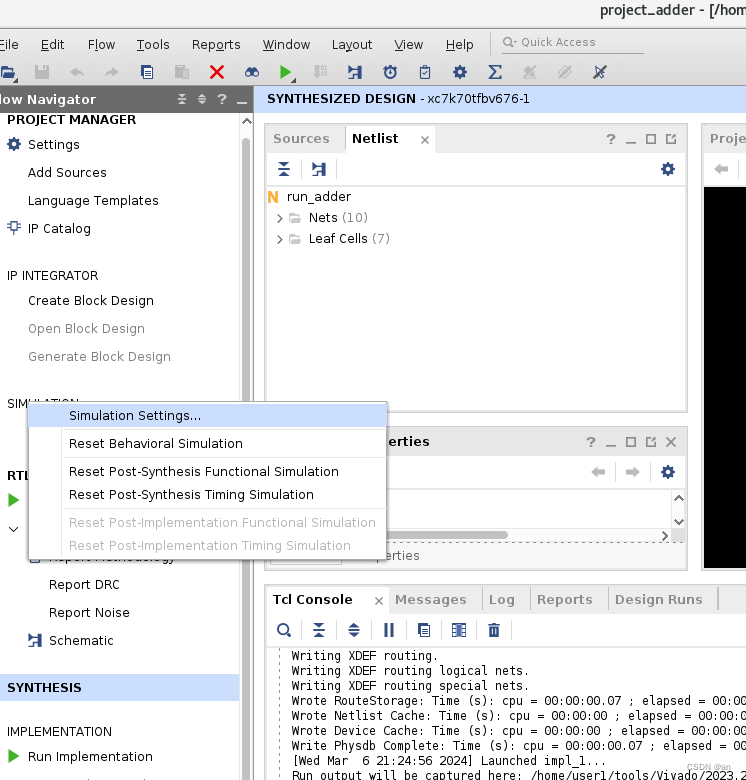

点击 Run Synthesis,然后OK,然后等待完成弹出窗口后点击Cancle

上图为还在进行 synthesis,下图完成:

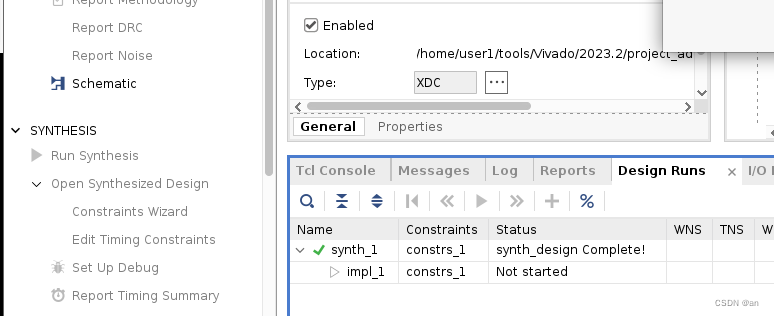

之后点击 open synthesized design 下的 constraints wizard

由于本次的加法器中并不需要时钟,所以该项可以忽略。

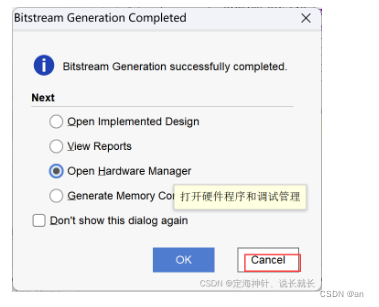

·生成BIT文件

点击Program and debug 下的 generate bitstream

由于本次实验只是进行虚拟仿真,所以弹出下面窗口时点击取消

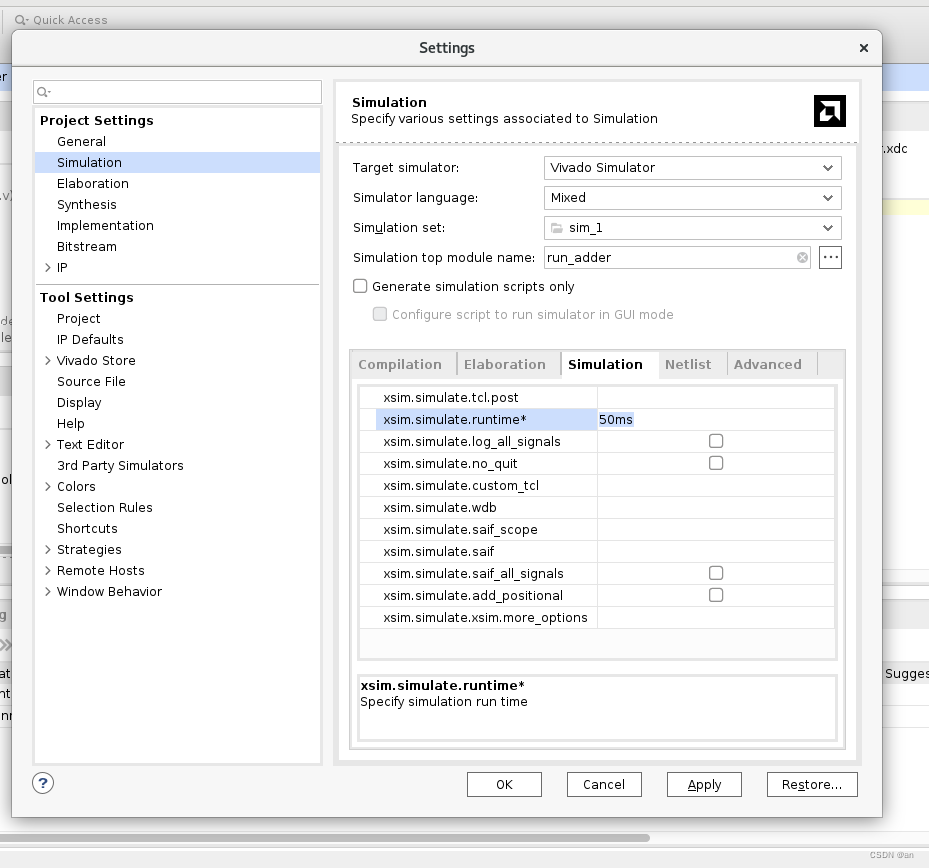

·然后右键点击

会弹出下列界面,根据需要设置时长,然后点击apply:

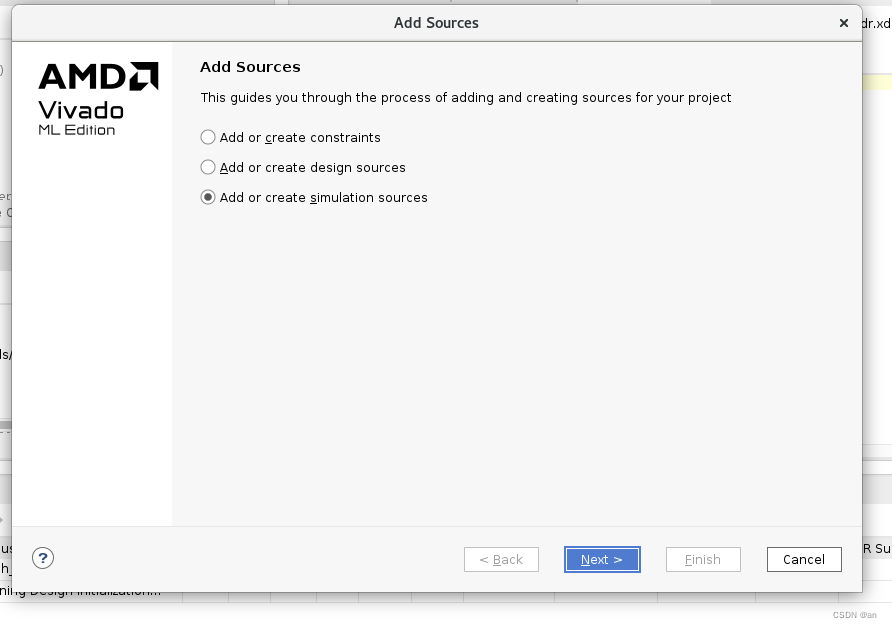

·点击project manager下的add sources,然后根据下图进行选择:

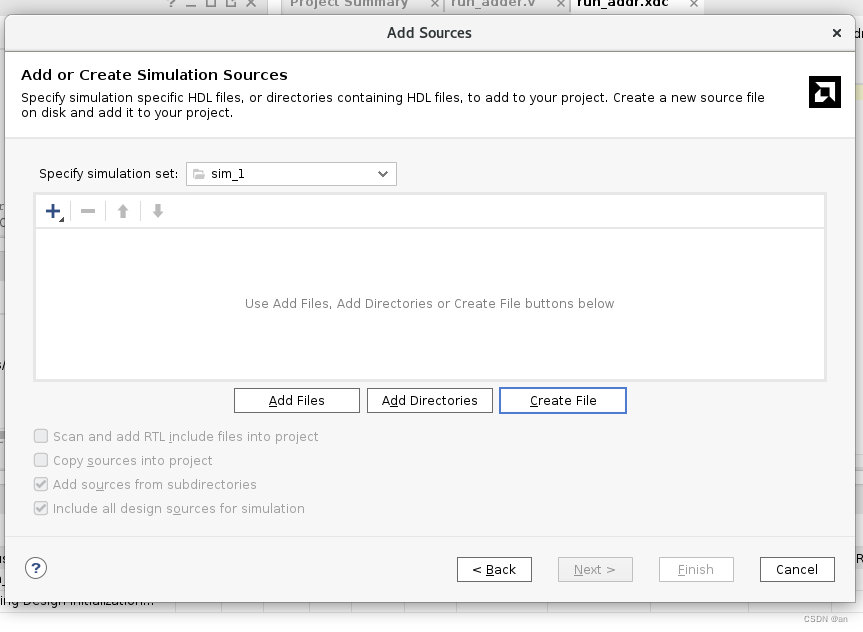

点击creat file:

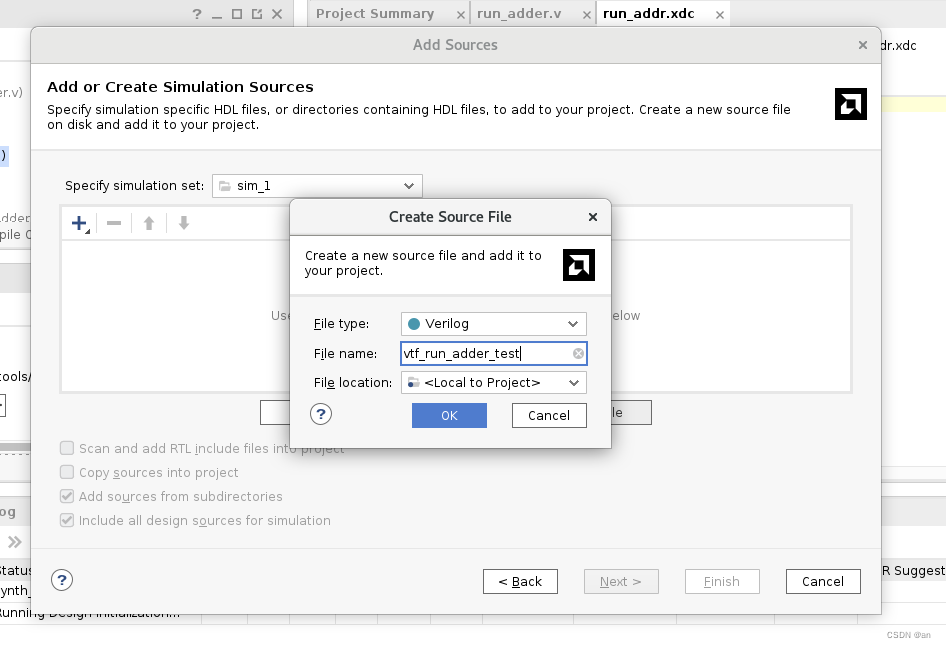

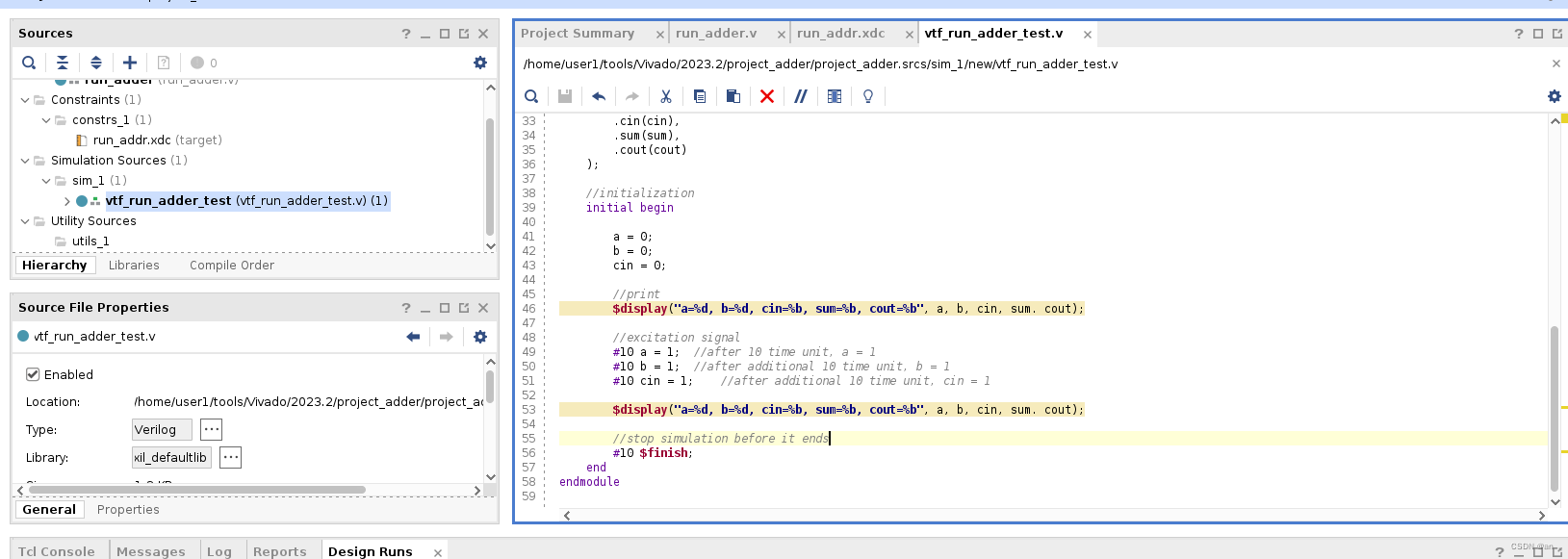

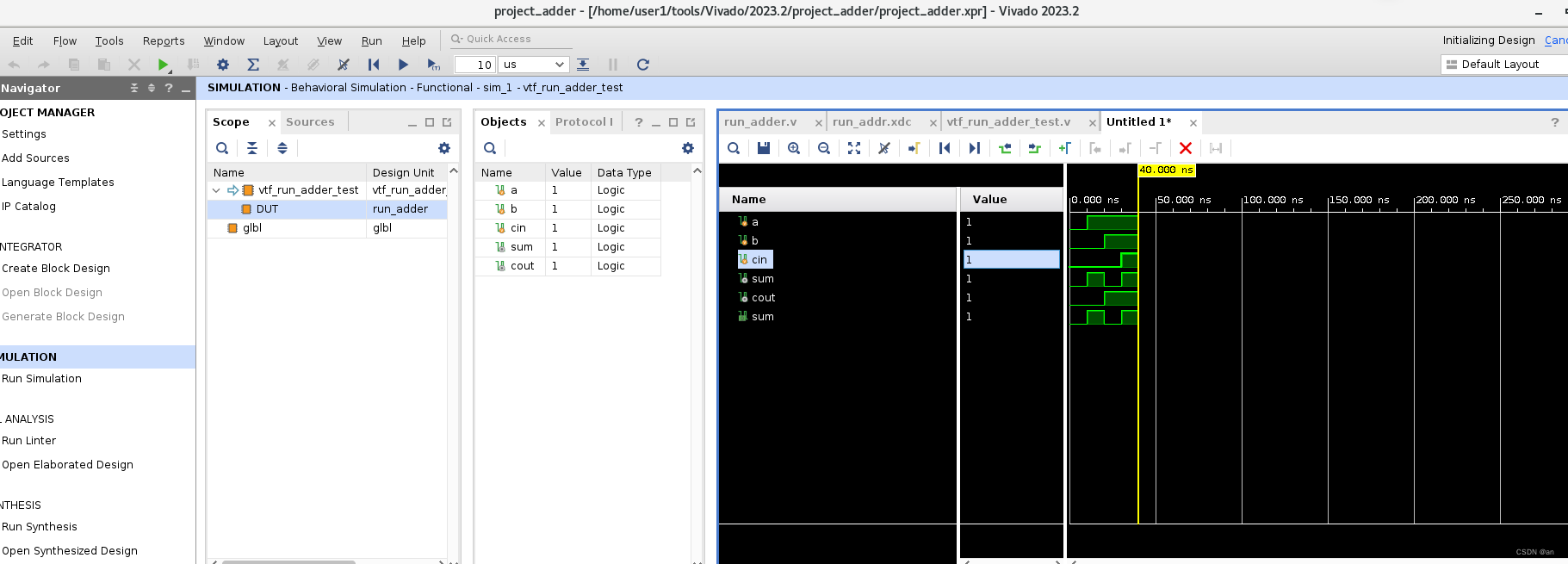

然后点击OK,点击Finish,弹出窗口让添加I/O,先不选择,点击cancle,点击Sources下的 simulation_Source下刚刚生成的仿真激励文件vtf_run_adder_test,进行编辑:

下面是代码:

`timescale 1ns / 1ps

module vtf_run_adder_test;

//define signal

reg a, b, cin;

wire sum, cout;

//instantiating the tested module

run_adder DUT(

.a(a),

.b(b),

.cin(cin),

.sum(sum),

.cout(cout)

);

//initialization

initial begin

a = 0;

b = 0;

cin = 0;

//print

$display("a=%d, b=%d, cin=%b, sum=%b, cout=%b", a, b, cin, sum. cout);

//excitation signal

#10 a = 1; //after 10 time unit, a = 1

#10 b = 1; //after additional 10 time unit, b = 1

#10 cin = 1; //after additional 10 time unit, cin = 1

$display("a=%d, b=%d, cin=%b, sum=%b, cout=%b", a, b, cin, sum. cout);

//stop simulation before it ends

#10 $finish;

end

endmodule保存之后,点击Run Simulation

仿真之后查看波形图:

后续深入的学习,等我学习之后有时间再记录。

本文介绍了如何在Vivado环境下设计一个简单的加法器,包括创建新工程、编辑Verilog文件、添加管脚约束、时间约束、生成BIT文件以及进行虚拟仿真和波形观察的过程。

本文介绍了如何在Vivado环境下设计一个简单的加法器,包括创建新工程、编辑Verilog文件、添加管脚约束、时间约束、生成BIT文件以及进行虚拟仿真和波形观察的过程。

3794

3794

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?