一 实验要求

1实验目的及实验内容要求

1.1 实验目的

1.设计并实现一个7段数码管控制接口,要求:在输入四位数据为0~15时,数码管显示0~F;

2.进一步熟悉VIVADO环境中电路的设计仿真及综合实现方法;

3.熟悉下载方法及实验系统调试方法。1.2 实验内容

1.VIVADO 环境下源程序的编写、编译

2.模拟仿真

3.程序下载

1.3实验要求

1. 在VIVADO 环境下完成输入四位数据为0~15时,数码管显示0~F的设计仿真;

2.完成配置程序的下载,并在EGo1开发板上对程序进行最终验证。

二 实验内容及过程

1 实验设计及分

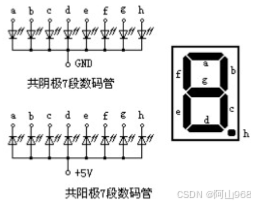

图1 数码管原理图

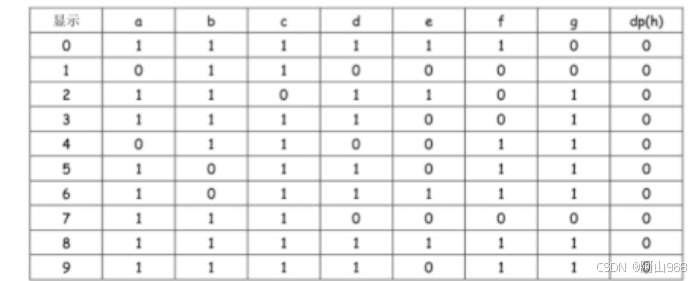

在数码管上显示数字就是将相应的段位点亮组成要显示的数字,共阴数码管的码值表如下所示,‘1’代表相应的管脚输出高电平,点亮相应段位,‘0’代表相应的管脚输出低电平,不点亮相应段位。

图2 共阴数码管对应的码值表

(1)编译文件:

module shiyansi(

input wire[3:0] x,

output wire an,

output reg[6:0] a_to_g

);

assign an=1;

always @(*)

case(x)

0:a_to_g=7'b1111110;

1:a_to_g=7'b0110000;

2:a_to_g=7'b1101101;

3:a_to_g=7'b1111001;

4:a_to_g=7'b0110011;

5:a_to_g=7'b1011011;

6:a_to_g=7'b1011111;

7:a_to_g=7'b1110000;

8:a_to_g=7'b1111111;

9:a_to_g=7'b1111111;

'hA:a_to_g=7'b1110111;

'hB:a_to_g=7'b0011111;

'hC:a_to_g=7'b1001110;

'hD:a_to_g=7'b0111101;

'hE:a_to_g=7'b1001111;

'hF:a_to_g=7'b1000111;

default:a_to_g=7'b1111110;

endcase

endmodule(2)仿真文件:

`timescale 1ns / 1ps

module test;

reg[3:0]x;

wire an;

wire[6:0]a_to_g;

shiyansi uut(x,an,a_to_g);

initial begin

x=0000;

end

always #10 x=x+1;

endmodule

(3)约束文件:

set_property PACKAGE_PIN P5 [get_ports x[3]]

set_property IOSTANDARD LVCMOS33 [get_ports x[3]]

set_property PACKAGE_PIN P4 [get_ports x[2]]

set_property IOSTANDARD LVCMOS33 [get_ports x[2]]

set_property PACKAGE_PIN P3 [get_ports x[1]]

set_property IOSTANDARD LVCMOS33 [get_ports x[1]]

set_property PACKAGE_PIN P2 [get_ports x[0]]

set_property IOSTANDARD LVCMOS33 [get_ports x[0]]

set_property PACKAGE_PIN G6 [get_ports an]

set_property IOSTANDARD LVCMOS33 [get_ports an]

set_property PACKAGE_PIN D4 [get_ports a_to_g[6]]

set_property IOSTANDARD LVCMOS33 [get_ports a_to_g[6]]

set_property PACKAGE_PIN E3 [get_ports a_to_g[5]]

set_property IOSTANDARD LVCMOS33 [get_ports a_to_g[5]]

set_property PACKAGE_PIN D3 [get_ports a_to_g[4]]

set_property IOSTANDARD LVCMOS33 [get_ports a_to_g[4]]

set_property PACKAGE_PIN F4 [get_ports a_to_g[3]]

set_property IOSTANDARD LVCMOS33 [get_ports a_to_g[3]]

set_property PACKAGE_PIN F3 [get_ports a_to_g[2]]

set_property IOSTANDARD LVCMOS33 [get_ports a_to_g[2]]

set_property PACKAGE_PIN E2 [get_ports a_to_g[1]]

set_property IOSTANDARD LVCMOS33 [get_ports a_to_g[1]]

set_property PACKAGE_PIN D2 [get_ports a_to_g[0]]

set_property IOSTANDARD LVCMOS33 [get_ports a_to_g[0]]

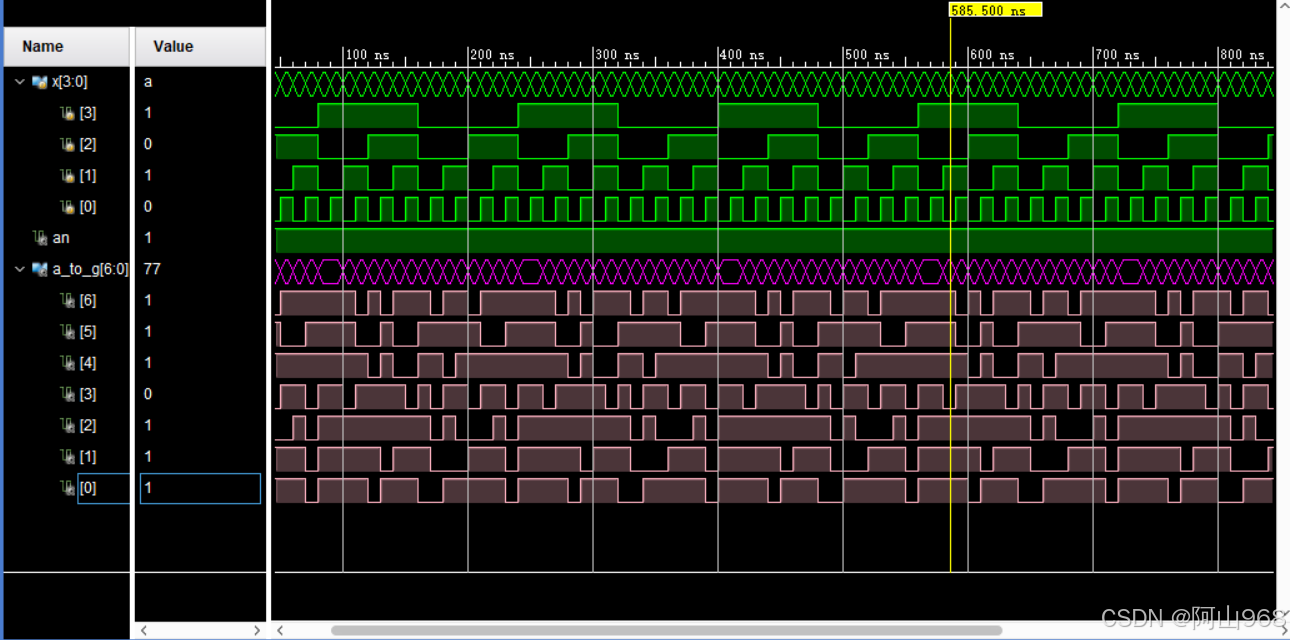

1.仿真波形

分析: 根据数码管的显示原理,需要将显示的数字转换成相关的二进制码,转化的条件如下:

输入0000,输出1111110,对应显示0

输入0001,输出0110000,对应显示1

输入0010,输出1101101,对应显示2

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1713

1713

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?