目录

Dff8ar

题目:

创建带高电平有效异步复位的8位 D触发器。所有dff都应由clk的正沿触发。

正确答案:

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output [7:0] q

);

always@(posedge clk or posedge areset)

begin

if (areset==1)

q <= 0;

else

q <= d;

end

endmodule

同时以时钟和复位信号的上升沿作为触发条件,进入always语句块后判断触发信号是否为高就好了。但由于我执着于题目中的高电平复位,误解为复位信号的触发条件只能是电平触发,为了在always的敏感条件中加入areset的电平触发,犯了如下错误。

错误答案1:

想着在always的触发条件中检查时钟上升沿和复位信号电平,使用了与逻辑

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output [7:0] q

);

always@(posedge clk | areset)

begin

if (areset==1)

q <= 0;

else

q <= d;

end

endmodule

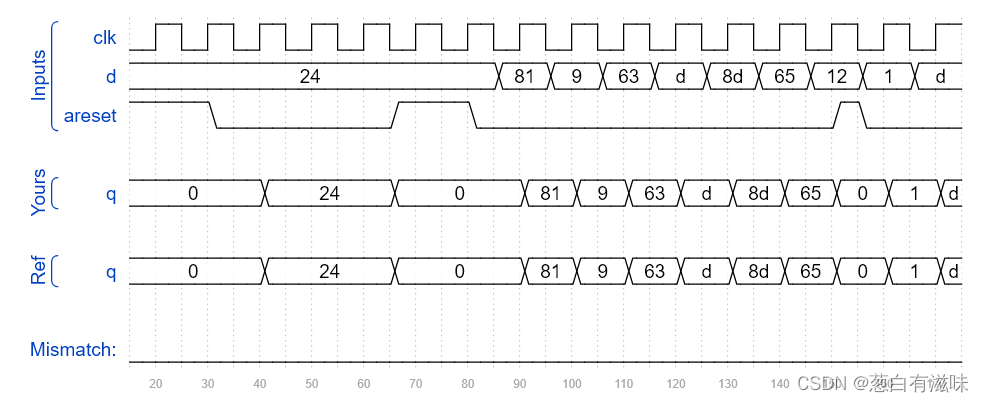

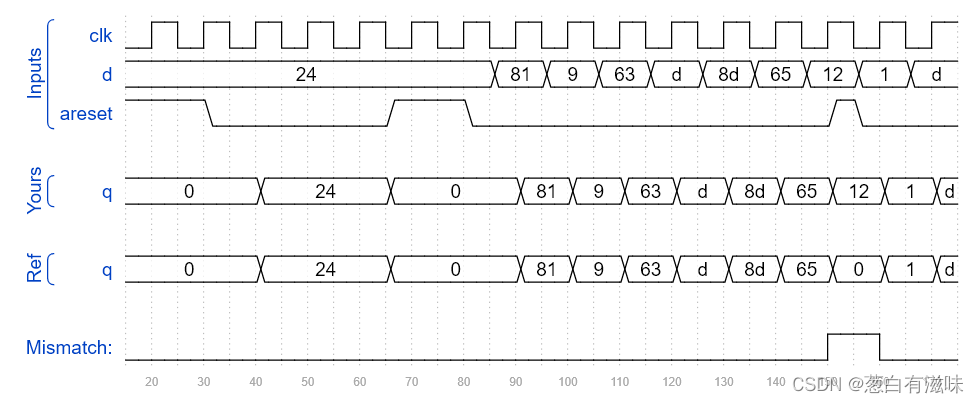

但在最后的信号中有一个mismatch,由下图可见是因为这个复位信号在始终上升沿之后到来,而此时输出刚好被d赋值,所以没能实现复位。

在尝试的过程中再次犯错

always@(posedge clk or areset)注意此处是不能同时对电平和边沿敏感的。

错误答案2:

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output [7:0] q

);

always@(posedge clk)

begin

q <= d;

end

always@(areset)

begin

q <= 0;

end

endmodule一个变量是不能在被多个块驱动赋值的

Exams/ece241 2014 q4

正确答案:

module top_module (

input clk,

input x,

output z

);

reg Q0=0,Q1=0,Q2=0;

wire din0,din1,din2;

assign din0 = x ^ Q0;

assign din1 = x & ~Q1;

assign din2 = x | ~Q2;

dff dff1(clk,din0,Q0);

dff dff2(clk,din1,Q1);

dff dff3(clk,din2,Q2);

assign z = ~(Q0 | Q1 | Q2);

endmodule

module dff(

input clk,

input d,

output reg q

);

always@(clk)

begin

q <= d;

end

endmoduleExams/ece241 2013 q7

正确答案:

module top_module (

input clk,

input j,

input k,

output Q);

wire jkffin;

wire [1:0] jk;

assign jk = {j,k};

always@(*)

begin

case (jk) //直接写成位拼接模式也行case({j,k})

2'b00: jkffin <= Q;

2'b01: jkffin <= 1'b0;

2'b10: jkffin <= 1'b1;

2'b11: jkffin <= ~Q;

endcase

end

dff1 dff11(clk,jkffin,Q);

endmodule

module dff1(input clk,input d,output reg q);

always@(posedge clk)

begin

q <= d;

end

endmodule错误答案:

module top_module (

input clk,

input j,

input k,

output Q);

wire jkffin;

wire [1:0] jk;

assign jk = {j,k};

always@(*)

begin

case (jk)

2'b00: jkffin = Q;

2'b01: jkffin = 1'b0;

2'b10: jkffin = 1'b1;

2'b11: jkffin = ~Q;

endcase

end

dff dff1(clk,jkffin,Q);

endmodule

/*

module dff(input clk,input d,output reg q);

always@(posedge clk)

begin

q <= d;

end

endmodule

*/自己写了个D触发器,但因为报错所以误以为内部有dff模块的触发器,因此屏蔽掉了,但实际上不行

1833

1833

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?