一、中断的基本概念

定义:CPU执行正常程序时,系统中出现特殊请求(中断申请),CPU暂时中止当前执行的程序,转去处理更紧急的事件(中断服务程序),处理完毕后,CPU自动返回原程序(中断返回)的过程。

作用:

①提高CPU的工作效率;

②可使多项任务共享一个资源(CPU);

③可及时处理突发事件,实现分时处理、实时处理;

④解决CPU与外设之间的速度矛盾,使CPU高效率地对多个外部设备进行管理。

二、MCS-51的中断源

8051有5个中断源:2个外部中断、2个定时器中断、一个串行口中断。

2.1 MSC-51单片机中断系统的结构:

2.2 中断标志寄存器

(1)控制寄存器TCON(SFR地址为88H)

| TCON | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| 位地址 | 8F | 8E | 8D | 8C | 8B | 8A | 89 | 88 |

IT0:外部中断/INT0的触发位,用来选择外部中断/INT0是低电平触发(0)还是下降沿触发(1);

IE0:外部中断/INT0的标志位,当IE0=1时,说明外部/INT0有中断信号,CPU开始处理,当IE0=0时,硬件复位;

IT1:外部中断/INT1的触发位,用来选择外部中断/INT0是低电平触发(0)还是下降沿触发(1);

IE1:外部中断/INT1的标志位,当IE0=1时,说明外部/INT1有中断信号,CPU开始处理,当IE1=0时,硬件复位;

TF0:T0中断标志位;

TF1:T1中断标志位。

(2)串行口控制寄存器SCON(SFR地址为98H)

| SCON | SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

| 位地址 | 9F | 9E | 9D | 9C | 9B | 9A | 99 | 98 |

RI:串行口接受请求标志;

TI:串行口发送请求标志。

三、中断的控制

3.1 中断的开放与关闭控制

由中断允许寄存器IE(SFR地址0A8H)实现两级控制

| IE | EA | X | X | ES | ET1 | EX1 | ET0 | EX0 |

| 位地址 | AF | AE | AD | AC | AB | AA | A9 | A8 |

EA:总允许位(一级控制)

ES:串行口中断允许位(二级控制)

ET1:定时器T1中断允许控制(二级控制)

EX1:外部中断/INT1中断允许控制(二级控制)

ET0:定时器T0中断允许控制(二级控制)

EX0:外部中断/INT0中断允许控制(二级控制)

例如:

想允许外部中断/INT1开放,需要:

SETB EA

SETB EX1

或 MOV IE,#84H

3.2 中断优先级的控制

由中断优先级寄存器IP(SFR地址0B8H)实现两级控制(1为高级、0为低级)

| IP | X | X | X | PS | PT1 | PX1 | PT0 | PX0 |

| 位地址 | BC | BB | BA | B9 | B8 |

PS:串行口中断优先级设置位;

PT1:定时器T1中断优先级设置位;

PX1:外部中断/INT1中断优先级设置位;

PT0:定时器T0中断优先级设置位;

PX0:外部中断/INT0中断优先级设置位;

优先级排队:高级>低级

同一级别中,按:/INT0>/INT1>T0>T1>串行口中断

CPU对中断的处理:先高后低,按序执行,高打断低,高不理低。

四、中断的查询与响应

4.1 中断的查询

每个机器周期中,所有的中断源都按照其顺序检查一遍;

到当前机器周期的S6状态时,就能查到所有被激活的中断申请并拍好优先顺序;

在下一个机器周期的S1状态,只要不受阻断,就可以开始响应高级中断。

中断被阻止的情况:

①同级或高级的中断正在执行;

②当前的机器周期不是指令的最后一个机器周期,需要等指令执行完后;

③CPU正在执行的指令是RETI或访问IE或IP寄存器时,CPU不会响应中断,而且要等到该指令的下一条指令执行完后中断才能响应。

4.2 中断的响应过程

①CPU查询到某一中断源后,使相应的“优先级激活触发器”置位用以阻断同级或低级中断;

②在硬件的控制下,自动将当时PC的内容(断点地址)压入堆栈,以备返回;

③然后将相应的中断矢量(中断入口地址)装入PC,使CPU转向对应的中断服务程序;

ROM中的六个特殊单元,五个存放中断的入口地址

0003H:/INT0的中断入口地址

000BH:T0的中断入口地址

0013H:/INT1的中断入口地址

001BH:T1的中断入口地址

0023H:串行口的中断入口地址

④中断服务程序最后一条指令是RETI,他将清除“优先级激活触发器”,从堆栈中弹出断点地址并装入PC中,使CPU回到原来主程序断点处继续运行。

五、外部中断

5.1 外部中断的触发方式

两个外部中断输入:/INT0&/INT1

两种触发方式:低电平触发、下降沿触发,由控制寄存器TCON中的IT0、IT1位控制

5.2 MCS-51对外部中断触发信号的要求

(1)边沿触发方式

在相邻的两个机器周期内,若第一次采集到的是高电平,第二次采集到的是低电平时,则TCON中的标志位IE0或IE1置位。因此外部设备发出的边沿信号的时间应该大于一个机器周期。

(2)电平触发方式

CPU在每个机器周期的S5P2期间采集到的/INT0(/INT1)的引脚为低电平时,将激活TCON中的标志位IE0(IE1)。所以电平触发方式中,外部的低电平至少保留一个机器周期。

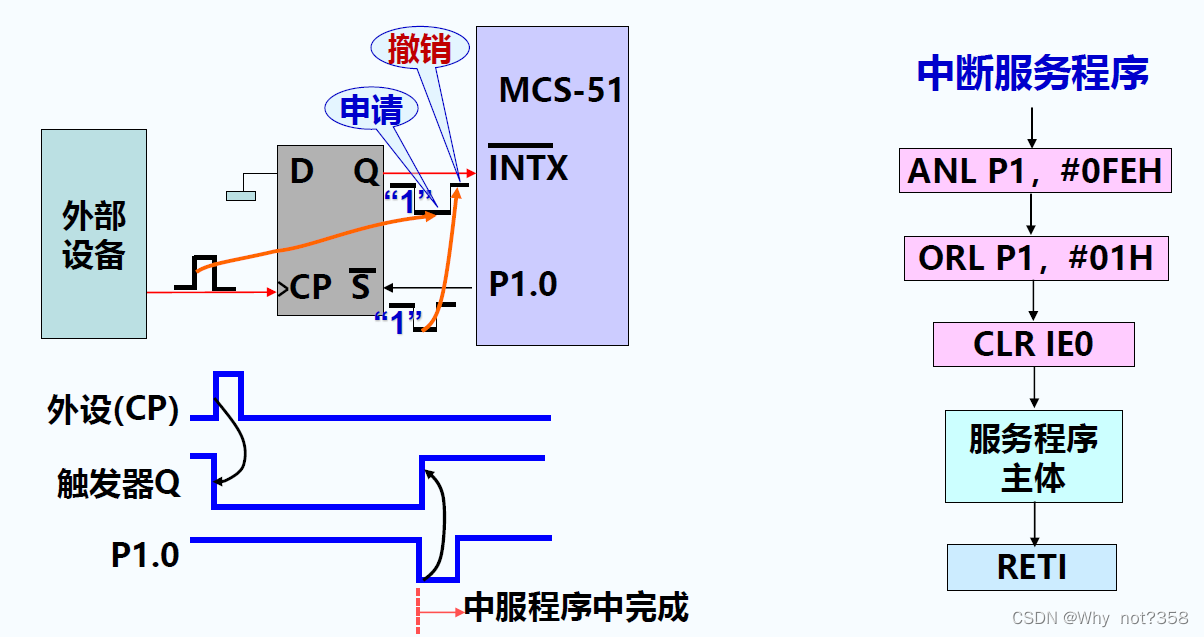

若外部信号不能满足要求,可用触发器等硬件电路解决。

六、中断请求的撤除

要求:在CPU进入中断服务程序后,执行RETI返回主程序前,外部的低电平必须撤掉,否则CPU返回主程序后,由于外部低电平时间过长导致再次进入中断,这样不仅造成一次多余的错误操作,还会使主程序不能正常运行。

6.1 解决外部电平信号过长的硬件方案

6.2 解决外部电平信号过长的软件方案

在中断处理程序的最后,RETI之前,对外部中断信号进行判断、等待,只有外部中断信号消失后再执行RETI返回主程序。

优点:硬件电路简单

缺点:程序执行速度慢,且不能解决外部中断信号过窄的问题。

6.3 MSC-51各中断请求的撤除方法

| 中断源 | 中断标志 | 说明 | 撤出方法 |

| INT0、INT1 | IE0、IE1 | 外部边沿触发 | 无影响 |

| INT0、INT1 | IE0、IE1 | 外部电平触发 | 电路、软件撤除 |

| T0、T1 | TF0、TF1 | 定时计数器触发 | 自动清除标志 |

| ES | RI、TI | 串行口中断 | 软件清除标志 |

此表是使用中断服务程序处理中断事件的情况,若采用查询方式来处理事件,都需要软件清除标志

七、中断的响应时间

中断响应时间:从终端有效(中断标志置1)到转向中断入口地址所需要的响应时间。

7.1 最短时间

中断请求有效,中断查询(一周期)+长调用,转向入口地址(两周期)

所以是三个机器周期

7.2 最长时间

如果中断信号发生在前面所说的三种阻断的情况,响应时间就要变长:

①若CPU正在执行同级或更高级中断,则取决于正在执行的中断的执行时间;

②若CPU执行的是多周期指令,如乘除法指令(4周期),最坏的情况还要再等三个周期才能开始进行本次中断的执行,所以是3+3=6;

③若CPU当前执行的指令是RETI或是访问寄存器IE或IP,则需要执行完本指令(一个周期)的下一条指令,若下一条指令是乘除法(四个周期),则为1+4+3=8。

若不考虑第①种情况,最长时间为8个机器周期。

3643

3643

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?