用Verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真。

module BinaryCounter8Bit(

input wire clk,

input wire rst,

output wire [7:0] count

);

reg [7:0] count;

always @(posedge clk or negedge rst) begin

if (!rst) begin

count <= 8'b0;

end else begin

count <= count + 1;

end

end

assign count = count;

endmodule

点此处编译

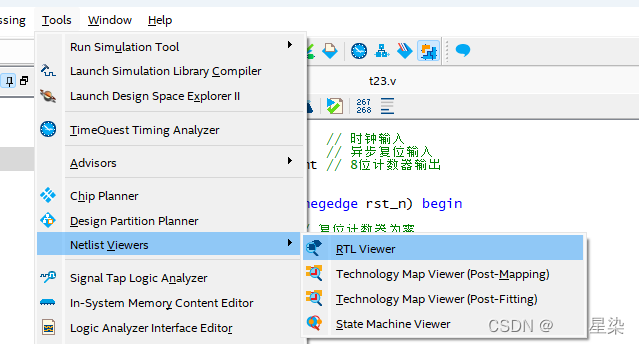

综合

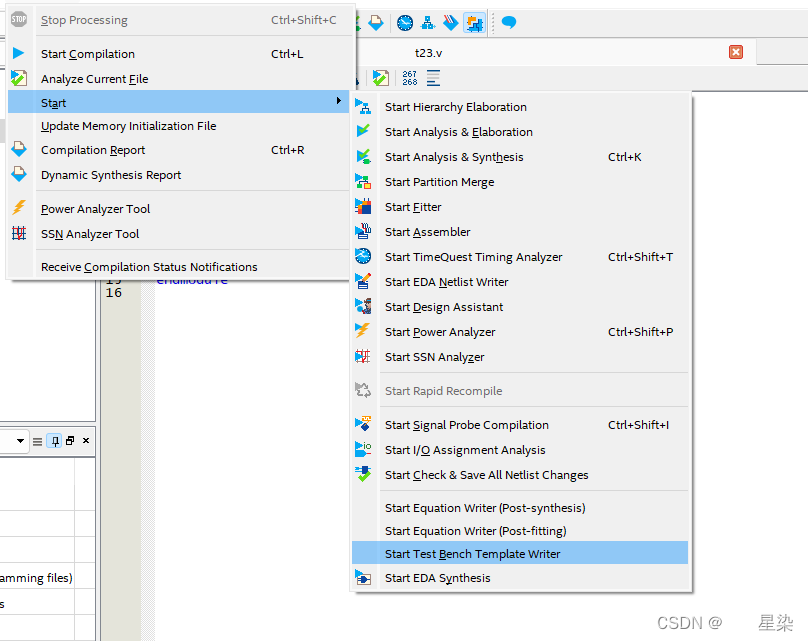

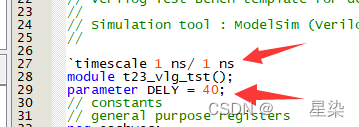

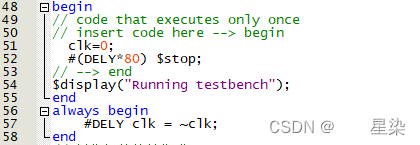

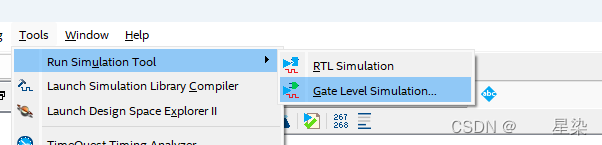

仿真

这里还需将rst置1才有效

- 可以在clk=0;后加rst=1;

- 或者在clk=0;后加rst=0;

并且在#DELY clk=~clk;后加#(DELY*20) rst=~rst;

仿真即可

本文介绍了如何使用Verilog语言设计一个带异步复位功能的8位二进制加法计数器,包括模块定义、逻辑实现以及模拟器中的复位策略。着重讲解了计数器的时序逻辑和仿真过程。

本文介绍了如何使用Verilog语言设计一个带异步复位功能的8位二进制加法计数器,包括模块定义、逻辑实现以及模拟器中的复位策略。着重讲解了计数器的时序逻辑和仿真过程。

2660

2660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?