Branch direction predictors are often structured as tables of counters indexed by the program counter and branch history. Each table entry usually uses two-bits of state because one-bit of state (remember last outcome) does not have enough hysteresis and flips states too easily.

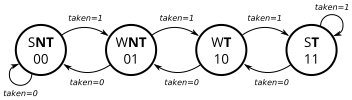

A two-bit state machine that works fairly well is a saturating counter[1], which counts up to 3 (or 2'b11) or down to 0 (or 2'b00) but does not wrap around. A "taken" result increments the counter, while a "not-taken" result decrements the counter. A branch is predicted to be taken when the count is 2 or 3 (or 2'b1x). Adding some hysteresis prevents a flipping of the prediction when a strongly-biased branch occasionally takes a different direction, requiring two increments in the opposite direction before the prediction is flipped.

References

- Jump up↑ R. Nair, "Optimal 2-bit branch predictors", IEEE Trans. Computers, vol. 44 no. 5, May, 1995

-

Description

Build a two-bit saturating counter.

The counter increments (up to a maximum of 3) when

train_valid= 1 andtrain_taken= 1. It decrements (down to a minimum of 0) whentrain_valid= 1 andtrain_taken= 0. When not training (train_valid= 0), the counter keeps its value unchanged.aresetis an asynchronous reset that resets the counter to weakly not-taken (2'b01). Output is the two-bit counter value.state[1:0]

AI翻译:

分支方向预测器的结构通常为计数器表,这些计数器由程序计数器和分支历史记录编制索引。每个表条目通常使用两位状态,因为一位状态(记住最后的结果)没有足够的滞后,并且很容易翻转状态。

运行良好的两位状态机是饱和计数器[1],最多计数 3(或 2'b11)或减少到 0(或 2'b00),但不环绕。“采取”的结果会增加计数器,而“未采取”的结果会减少计数器。当计数为 2 或 3(或 2'b1x)时,预计将获取一个分支。添加一些滞后可以防止当强偏偏分支偶尔采用不同的方向时,预测的翻转,需要在相反方向上增加两次,然后才能翻转预测。

引用

- Jump up↑ R. Nair,“最优 2 位分支预测器”,IEEE Trans. Computers,第 44 卷第 5 期,1995 年 5 月

描述

构建一个 2 位饱和计数器。

当 train_valid= 1 和 train_taken= 1 时,计数器递增(最多 3)。 当 train_valid= 1 和 train_taken= 0 时,它会递减(最小为 0)。当不训练即( train_valid= 0) 时,计数器保持其值不变。

areset是一种异步复位,将计数器复位为弱未取 (2'B01)。输出是两位计数器值。state[1:0]

分析:根据题目所给状态转换图运用三段论

实现代码如下:

module top_module(

input clk,

input areset,

input train_valid,

input train_taken,

output reg [1:0] state

);

parameter SNT = 2'b00;

parameter WNT = 2'b01;

parameter WT = 2'b10;

parameter ST = 2'b11;

reg [1:0] next_state;

always @(*) begin

case(state)

SNT:next_state<=train_taken?WNT:SNT;

WNT:next_state<=train_taken?WT:SNT;

WT :next_state<=train_taken?ST:WNT;

ST :next_state<=train_taken?ST:WT;

default:;

endcase

end

always @(posedge clk or posedge areset) begin

if(areset)

state<=WNT;

else if(train_valid)

state<=next_state;

else

state<=state;

end

endmodule

97

97

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?