视频链接

QDR硬件电路设计

1、QDR基本介绍

QDR是Quad Data Rate Static Random Access Memory(QDR SRAM)的缩写,也就是四倍数据速率静态随机存取存储器的意思。QDR的四倍数据速率是相对普通SRAM而言的。

QDR(Quad Data Rate):四倍数据倍率,在DDR的基础上,拥有独立的写接口和读接口,以此达到4倍速率。

QDR在保留DDR特征的基础上,对其数据总线进行了升级,DDR只有一条数据通道,数据读/写操作共用,属于半双工工作方式,而QDR拥有两独立条数据通道,数据读/写操作可以同时进行,属于全双工工作方式,因此,QDR的数据存取速率又是DDR的两倍。

QDR器件规范是由Cypress、IDT、NEC、Samsung和Renesas等公司组成的QDR联盟共同定义和开发的。

2、QDR-II、QDR-II+和QDR-IV的区别

具体细节参考《QDR-IV 设计指南》。P34-44

细节已明确指出。可以从三方面比较。

1、架构、带宽、功耗以及特性比较

2、RTR比较

3、QDR-II、QDR-II+和QDR-IV器件中的引脚差异

3、简谈SDR、DDR、QDR存储器的比较

SDR:Single Data Rate, 单倍速率

DDR:Dual Data Rate, 双倍速率

QDR:Quad Data Rate, 四倍速率

4、QDR-XP介绍(整版以CY7C4142KV13为例)

4.1、QDR-IV系列包括:HP和XP

QDR-IV高性能(HP)SRAM:为两字突发架构器件,在每个周期中能够以最高667MHz的频率进行两次访问,并且读取操作的延时为5个时钟周期。

QDR-IV极高性能(XP)SRAM:为分页的两字突发架构器件,在每个周期中能够以最高1066 MHz的频率进行两次访问,并且读取操作的延迟为8个时钟周期。由于频率增大,QDR-IV XP能够提供2132MT/s的RTR和153.5 Gb/s的带宽。

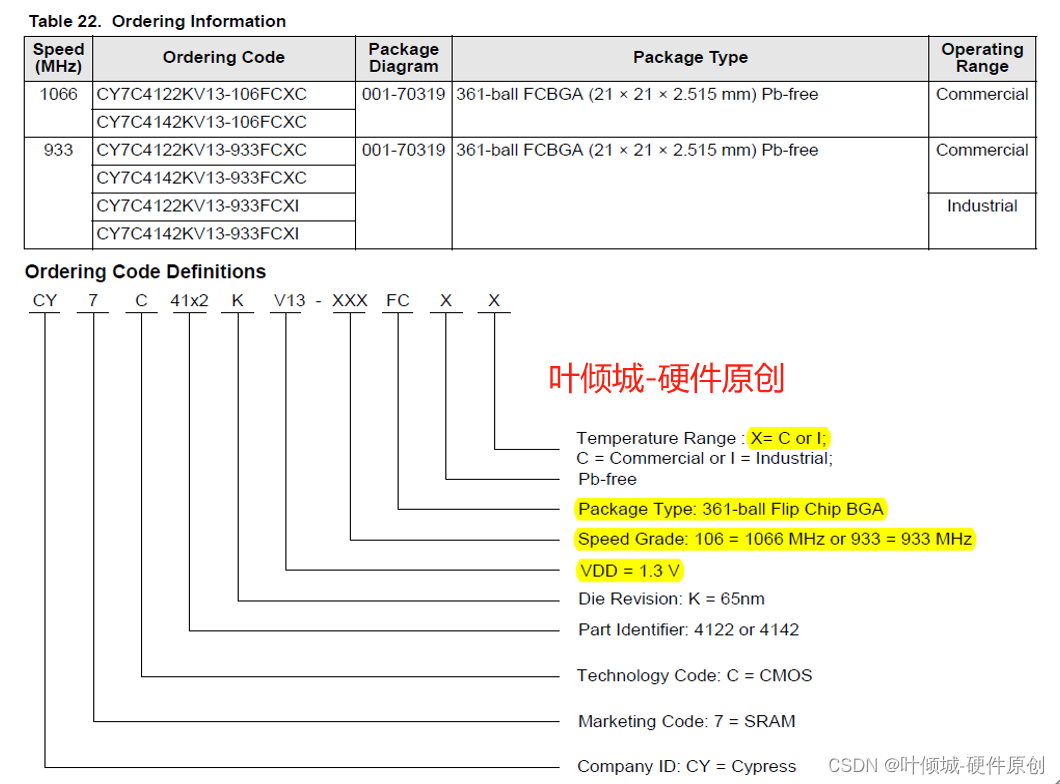

4.2、QDR-IV命名规范

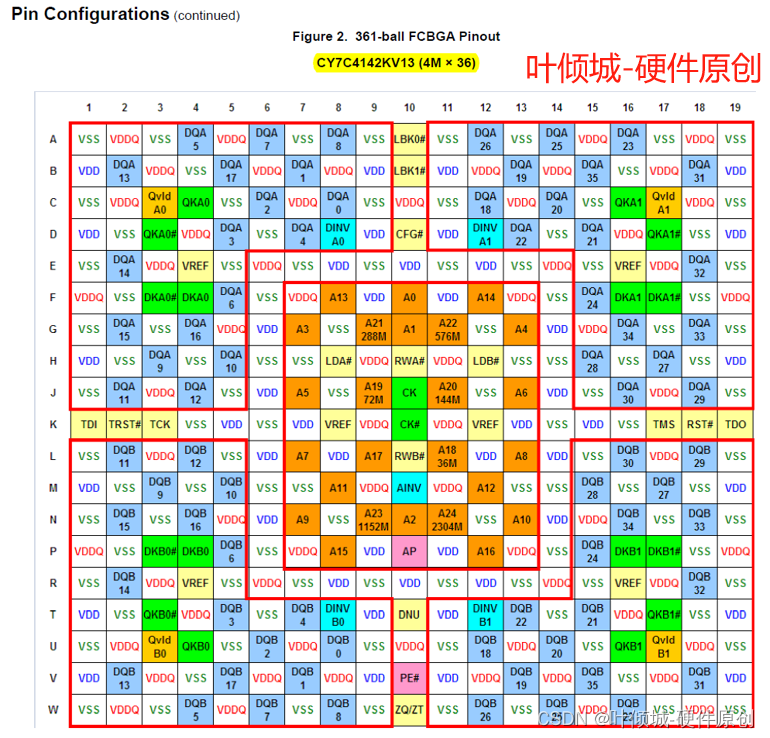

4.3、QDR-IV封装(361-ball BGA)

CY7C4122KV13-8M X 18

CY7C4142KV13-4M X 36

X18和X36的封装是一样的,但是管脚的定义不一样!!!(具体详见器件手册)

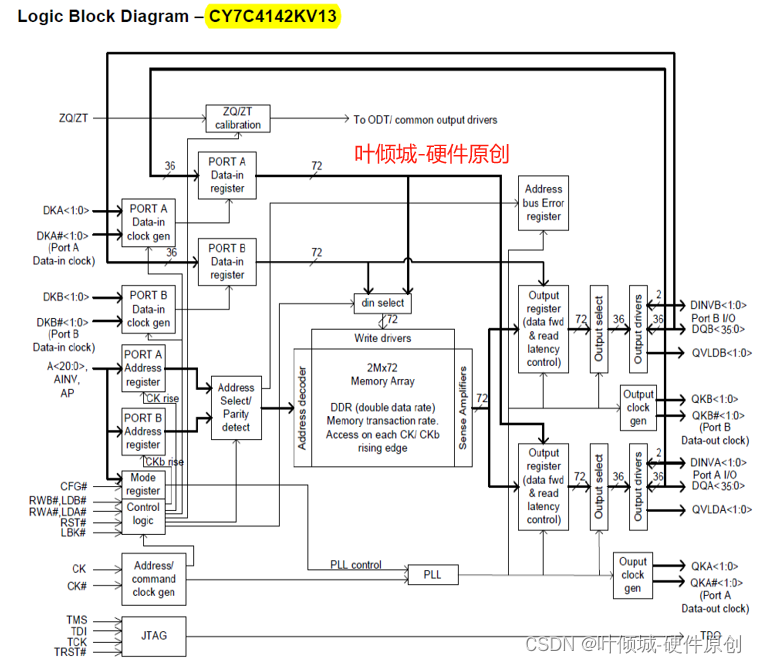

5、QDR框图(注意区别 整版以CY7C4142KV13为例)

在原理图设计的时候尤其要注意。(X18和X36的区别)

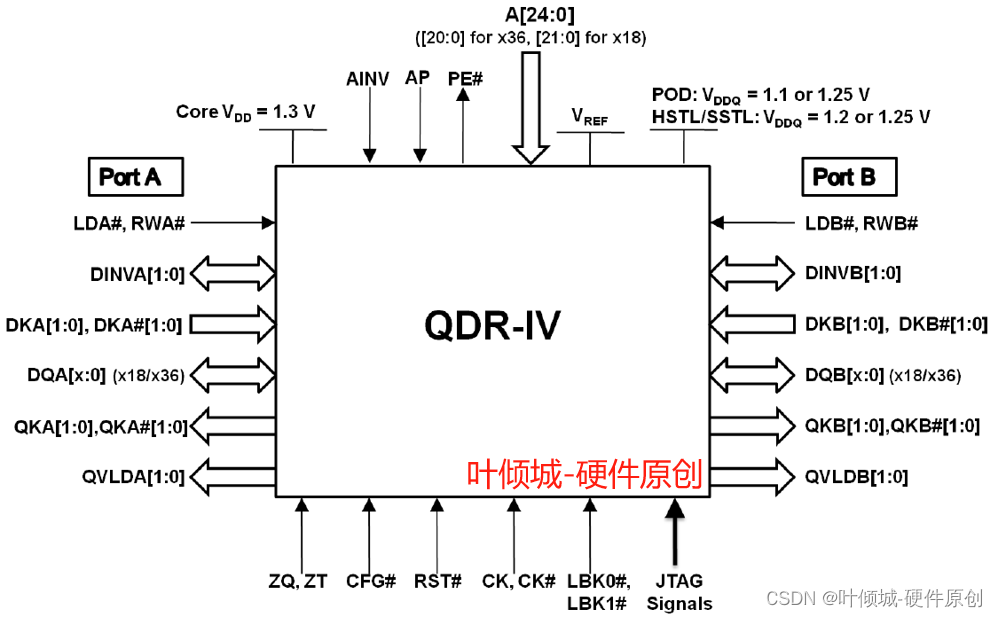

显示的是QDR-IV的通用接口框图。这些接口的设计与POD和HSTL/SSTL类的接口相兼容。

功能描述:

QDR-IV SRAM具有两个数据I/O端口,即端口A和端口B。

由于可以独立访问这两个端口,所以对存储器阵列进行的任何读/写访问组合均可得到最大的随机数据传输速率。

6、QDR-IV的特性

参考《QDR-IV 设计指南》(远不止下面所列出来的)

7、QDR管脚定义(以X36 为例子)

QDR的管脚可以分为电源线、时钟、数据线、地址线和控制线。

7.1、电源线

对于电源电压,QDR SDRAM系统要求三个电源,分别为VDD、VDDQ和VREF。

| 管脚符号 | 类型 | 描述 |

| VDD | Supply | Power Supply Inputs to the Core of the Device。 内核供电电压,1.3V |

| VDDQ | Supply | Power Supply Inputs for the Outputs of the Device DQ。DQ电源,1.2V。 |

| VREF | Supply | Reference Voltage Input. Static input used to set the reference level for inputs, outputs, and AC measurement points. 参考电压输入。静态输入用于设置输入、输出和交流测量点的参考电平。 |

| VSS | Supply | 地。 |

Datasheet P30

1、电源VDD

VDD是给内核供电。电压为1.3V

2、电源VDDQ

VDDQ是给设备输出供电。工业级为1.2V,商业级为1.1V

3、参考电源VREF

注意VREF的参考电压,对应的是POD接口,还是HSTL/SSTL接口。

VREF生成

1、VREF消耗的电流量可以忽略不计,因为它是差分放大器的输入。POD信令模式和HSTL/SSTL信令模式要求的最大VREF电流分别为3μA和1μA。

2、VREF大小取决于VDDQ电压。VREF等于VDDQ/2(HSTL/SSTL接口),并等于VDDQ * 0.7(POD接口)。因此,可以通过电阻分压器对VDDQ进行分压,或通过调节器IC生成VREF。

VDD要先于VDDQ上电,VDDQ要先于VREF或与之同时上电。

终端原理图建议 《具体详见QDR-IV 设计指南 P21-23》

不匹配阻抗使信号将沿着传输线而反射,这样会导致振铃并会损坏系统。振铃会缩小接收器的动态范围(由于阈值移位),并能导致误触发。为了消除来自信号源的反射,信号源的阻抗必须与走线的阻抗相匹配。

7.2、时钟

QDR-IV使用三种不同的时钟:

1、(CK, CK#),用于地址和指令信号

2、(DKA, DKA#, DKB, DKB#),用于数据输入信号

3、(QKA, QKA#, QKB, QKB#),用于数据输出信号

| 管脚符号 | 类型 | 描述 |

| CK、CK# | Input Clock | Address/Command Input Clock。 |

| DKA,DKA# DKB,DKB# | Input | Data Input Clock。 |

| QKA,QKA# QKB,QKB# | Output | Data Output Clock。 |

时钟信号说明

7.3、数据组

数据端口:QDR-IV具有两个独立的双向数据端口,它支持同时进行两字突发架构的读和写操作。两个数据端口均以双倍数据速率工作。 QDR-IV的每个端口的宽度可以为18位或36位I/O。

| 管脚符号 | 类型 | 描述 |

| DQA[35:0] DQA[35:0] | I/O | 数据输入/输出,双向数据总线。 For (×36) data width DQA[35:0]; DQB[35:0] For (×18) data width DQA[17:0]; DQB[17:0] |

7.4、地址、控制

地址端口:QDR-IV包含一个运行速度为双倍数据速率的地址端口,该端口用于控制两个数据端口。

控制信号:QDR-IV中的所有控制信号均以单倍数据速率(SDR)工作。

| 管脚符号 | 类型 | 描述 |

| A[24:0] | Input | For (×36) data width - Address inputs A[20:0] are used and A[24:21] are reserved。 |

| AP | Input | Address Parity Input。地址奇偶校验输入 |

| PE# | Output | Address Parity Error Flag。 地址奇偶校验错误标志。 |

| AINV | Input | Address Inversion Pin for Address and Address Parity Inputs。 地址和地址奇偶校验输入的倒置管脚。 |

| ZQ/ZT | Input | Output Impedance Matching Input。 输出阻抗匹配输入。 |

| CFG# | Input | Configuration bit。This pin is used to configure different mode registers。 配置bit |

| RST# | Input | Active Low Asynchronous RST。同步低有效RST This pin is active when RST# is LOW and inactive when RST# is HIGH。The RST# pin has an internal pull-down resistor。 |

| LDA#, LDB# | Input | Synchronous Load Input。 同步负载输入 |

| RWA#, RWB# | Input | Synchronous Read/Write Input。 同步读/写输入 |

| QVLDA[1:0] QVLDB[1:0] | Output | Output Data Valid Indicator。 输出数据有效指标 |

| LBK0_#、LBK1_# | Input | Loopback mode for control and address / command / clock deskewing。 用于控制和地址/命令/时钟同步的环回模式 |

| DINVA[1:0] DINVB[1:0] | I/O | Data Inversion Pin for DQ Data Bus。 用于DQ数据总线的数据反转管脚 |

7.4.1、总线反转

7.4.2、地址总线反转

7.4.3、数据总线反转

7.5、JTAG组

| 管脚符号 | 类型 | 描述 |

| TMS | Input | Address/Command Input Clock。 |

| TDI | Input | Data Input Clock。 |

| TCK | Input | Data Output Clock。 |

| TDO | output | Test Data Output pin for JTAG。 |

| TRST# | Input | Test Reset Input pin for JTAG。This pin must be tied to VDD if the JTAG function is not used in the system。TRST# input is applicable only in JTAG mode。 |

以X36为例 19X19=361 PIN

DQA[35:0]、DQB[35:0]: 72根

A[17:0]地址输入线 18根

A18 1根

A19 1根

A20 1根

A21 1根

A22 1根

A23 1根

A24 1根

DKA0_P/N、DKA1_P/N、QKA0_P/N、QKA1_P/N[1:0]:差分时钟 8根

DKB0_P/N、DKB1_P/N、QKB0_P/N、QKB1_P/N[1:0]:差分时钟 8根

CK_P/N 2根

LDA#, LDB# 2根

RWA#, RWB# 2根

QVLDA[1:0]、QVLDB[1:0] 4根

DINVA[1:0]、DINVB[1:0] 4根

LBK0_#、LBK1_# 2根

AP 1根

AINV 1根

CFG_N 1根

RST_N 1根

PE_N 1根

ZQ_ZT 1根

DUN 1根

TMS: 1根

TDI: 1根

TCK: 1根

TDO: 1根

TRST#: 1根

VREF:参考电压 6根

VDDQ:电源 64根

VDD:电源 44根

VSS:GND 106根

合计:72+25+18+21+5+220=361

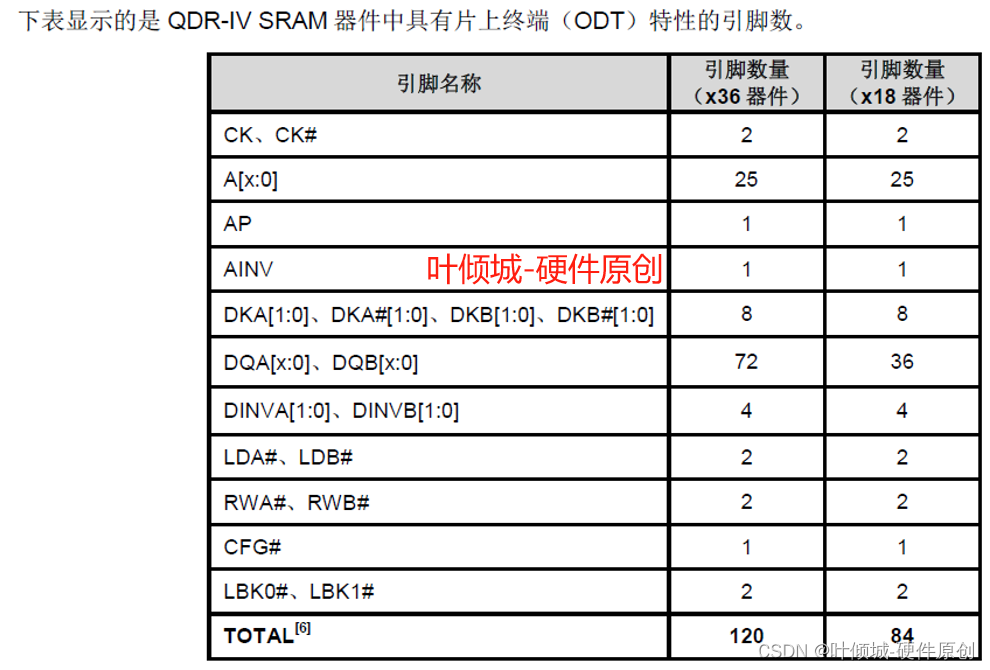

7.6、X36和X18的区别

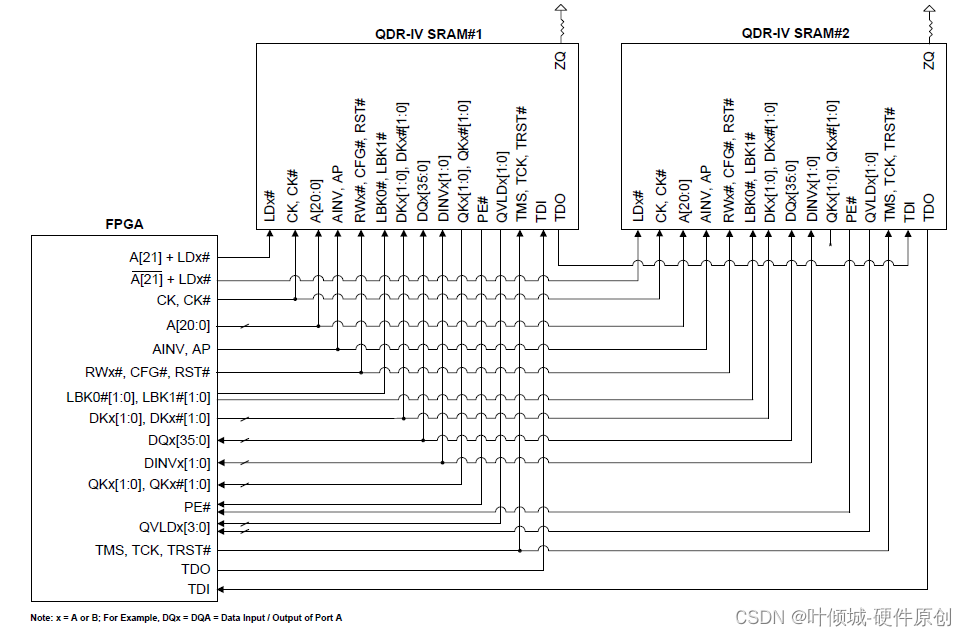

8、QDR硬件电路设计要点(★)

本文详细介绍了QDR静态随机存取存储器的工作原理、QDR-II和QDR-IV的不同之处,以CY7C4142KV13为例,涵盖了电源管理、时钟信号、地址线和控制线的定义,以及硬件电路设计的关键要点。视频内容深入浅出,适合学习QDR技术的工程师参考。

本文详细介绍了QDR静态随机存取存储器的工作原理、QDR-II和QDR-IV的不同之处,以CY7C4142KV13为例,涵盖了电源管理、时钟信号、地址线和控制线的定义,以及硬件电路设计的关键要点。视频内容深入浅出,适合学习QDR技术的工程师参考。

3478

3478

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?