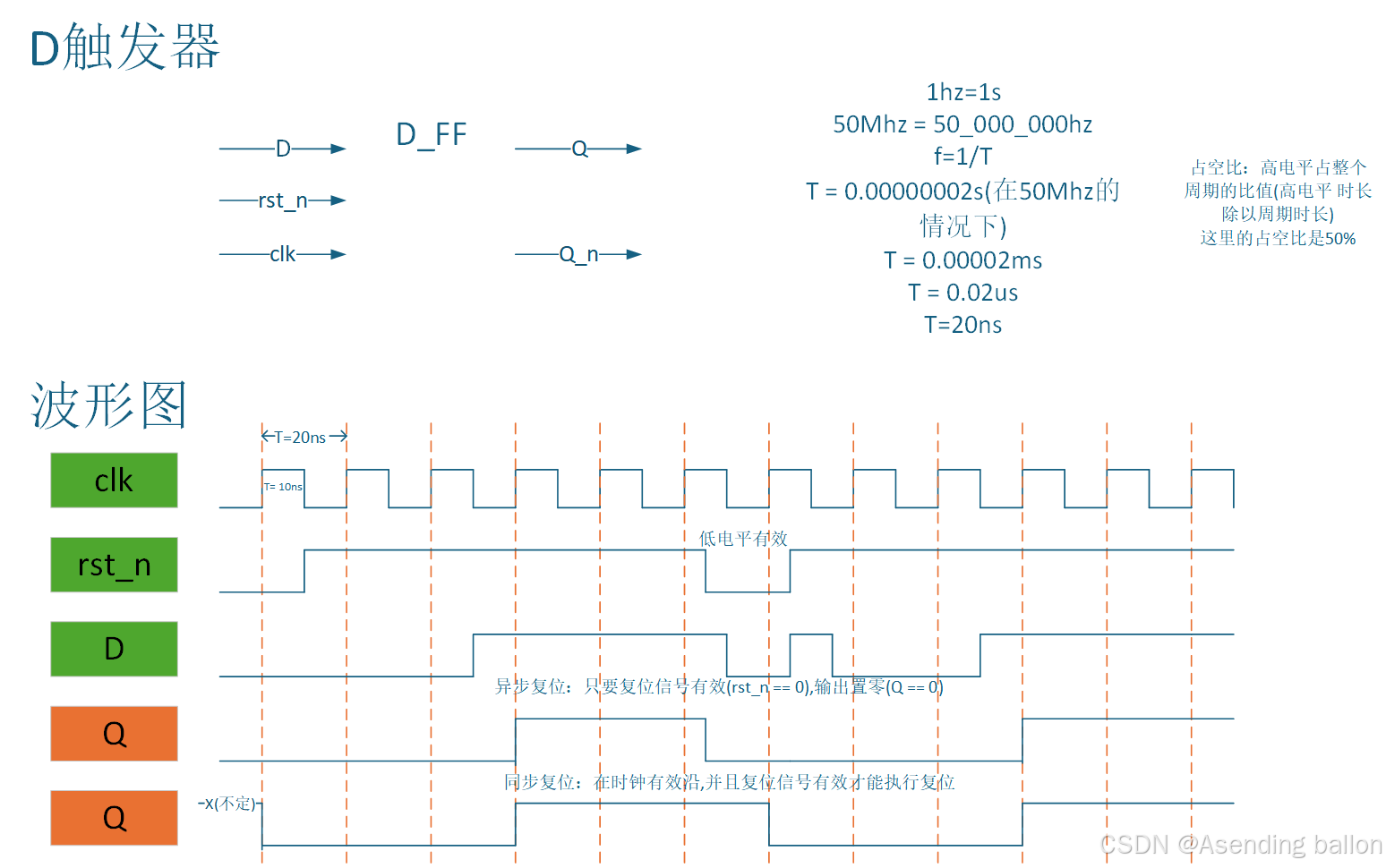

在实现偶分频之前,首先先介绍一下D触发器

触发器(D Flip-Flop)是一种常用的时序逻辑电路,其主要功能是存储一位二进制数据,并在时钟信号的控制下实现数据的锁存和传输。以下是D触发器的基本逻辑和特性:

1. 基本功能

D触发器的核心功能是将输入信号(D端)在时钟信号(CLK)的上升沿或下降沿锁存到输出端(Q端)。其基本逻辑可以表示为:

CLK D Q(下一个状态)

上升沿/下降沿 0 0

上升沿/下降沿 1 1

D端:数据输入端,用于提供要存储的数据。

Q端:数据输出端,表示当前存储的数据。

CLK端:时钟信号输入端,用于控制数据的锁存时刻。

2. 工作原理

D触发器的工作原理基于时钟信号的边沿触发。具体过程如下:

在时钟信号的某个边沿(通常是上升沿或下降沿)到来时,D端的值会被锁存到触发器内部的存储单元。

锁存后的值会出现在Q端,并保持稳定,直到下一个时钟边沿到来。

3.工程实现

通过D触发器我们可以实现偶分频,以下为使用D触发器编写偶分频的工程

3.1visio图

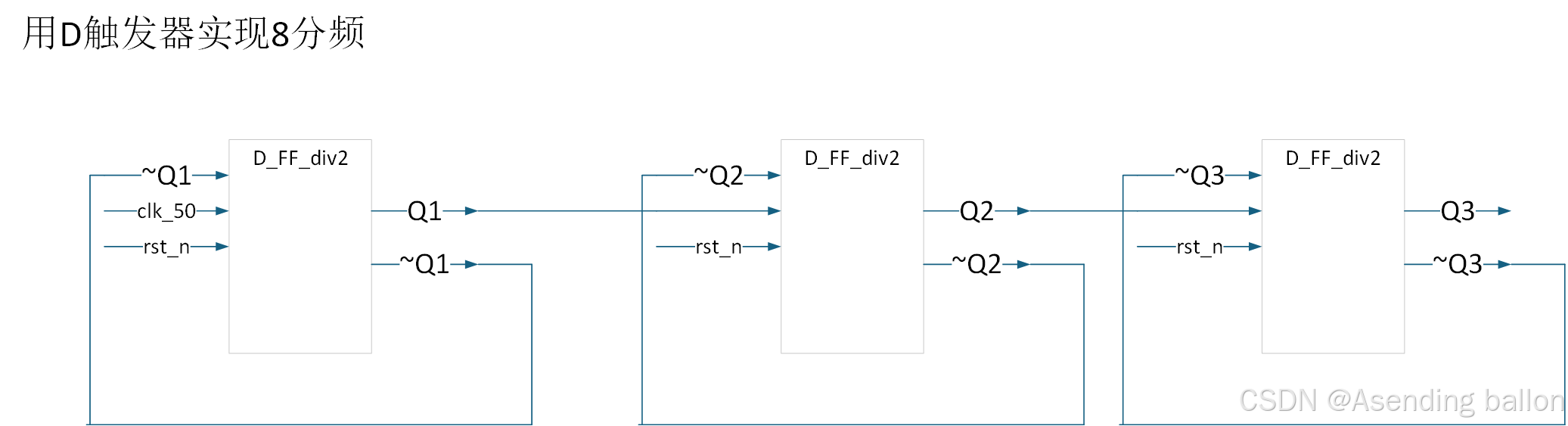

以下Visio图是D触发器的图,以及用D触发器实现8分频的图

图一(D触发器)

图二(D触发器实现8分频)

3.2 通过Verilog编写代码实现功能

3.2.1 D触发器

//D触发器 代码实现

//在时钟脉冲上升沿或者下降沿到来的时候将输入信号送到输出端

//如果边沿未到,即使输入端的数据发生改变,输出只会保持原来的样子

module D_FF (

input wire D ,//数据输入

input wire rst_n ,//低电平复位,Q为零

input wire clk ,//50Mhz,20ns周期信号

output reg Q ,//因为要用always书写,是存储型变量,所以用reg,数据输出

output wire Q_n//Q_n=~Q

);//异步复位 always @ (posedge clk or negedge rst_n)

//同步复位 always @ (posedge clk)/always @ (negedge clk)

//时钟上升沿工作,低电平复位

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin//if()判断必须要括号内为真,所以if (~rst_n)就等同于if (rst_n == 0)

Q <= 1'd0 ;//时序逻辑用"<="非阻塞赋值

end

else begin

Q <= D ;

end

end

assign Q_n = ~Q ;endmodule

3.2.2 用D触发器实现8分频

module D_FF_div8(

input wire clk_50,

input wire rst_n,

output reg Q3

);reg Q1 ;

reg Q2 ;

always @(posedge clk_50 or negedge rst_n) begin

if (~rst_n) begin

Q1 <= 1'd0;

end

else begin

Q1 <= ~Q1 ;

end

endalways @(posedge Q1 or negedge rst_n) begin

if (~rst_n) begin

Q2 <= 1'd0;

end

else begin

Q2 <= ~Q2 ;

end

endalways @(posedge Q2 or negedge rst_n) begin

if (~rst_n) begin

Q3 <= 1'd0;

end

else begin

Q3 <= ~Q3 ;

end

endendmodule

通过上面的visio图可以很明显的看出,当一个D触发器的输出Q非与输入D连在一起时,此时D触发器就变成了一个二分频器,因此若将三个D触发器像这样连接之后,再相互连起来,如图二所示,就可构成八分频,由此可通过D触发器实现偶分频。

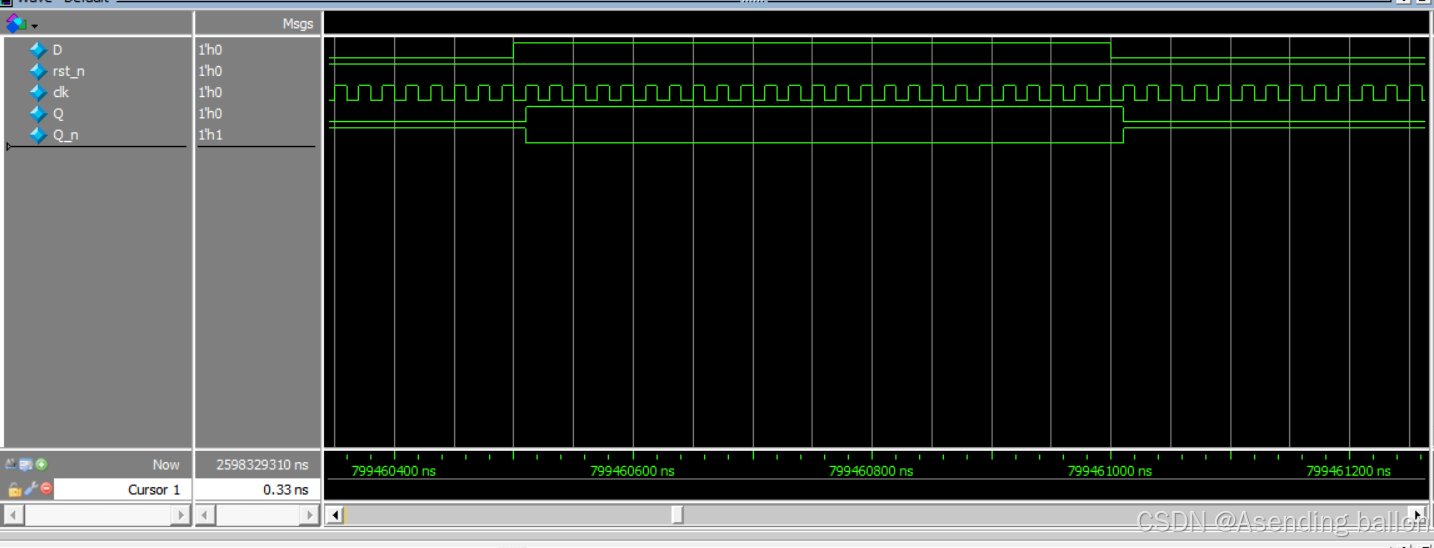

3.3 tb文件及其仿真图

3.3.1 D触发器

`timescale 1ns/1ps

module D_FF_tb ();

//定义测试信号

reg D ;

reg rst_n ;

reg clk ;

wire Q ;

wire Q_n ;

//初始化测试信号

initial begin

D = 1'd0 ;

rst_n = 1'd0 ;

clk = 1'd0 ;

#201 ;

rst_n = 1'd1 ;

end

//生成时钟信号,50Mhz,20ns,占空比50%

always #10 clk = ~clk ;

//随机数初始化D

always #500 D = {$random}%2;

//调用测试模块即例化

D_FF D_FF_1 (

.D (D ),

.rst_n (rst_n),

.clk (clk ),

. Q ( Q ),

. Q_n ( Q_n )

);

endmodule

3.3.3 用D触发器实现8分频

`timescale 1ns/1ns

module D_FF_div8_tb();

reg clk_50 ;

reg rst_n ;

wire Q3 ;

//初始赋值

initial begin

clk_50 = 1'd0 ;

rst_n = 1'd0 ;

#200

rst_n = 1'd1 ;

end//提供时钟信号,周期为20ns

always #20 clk_50 = ~clk_50;//例化

D_FF_div8 D_FF_div8_1(

.clk_50 (clk_50),

.rst_n (rst_n ),

. Q3 ( Q3 )

);

endmodule

4.总结

D触发器是一种简单而强大的时序逻辑元件,它通过时钟信号的边沿触发,将输入数据锁存到输出端。其广泛应用于寄存器、计数器、同步电路等数字电路设计中。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?