目录

MCS-51中断源:

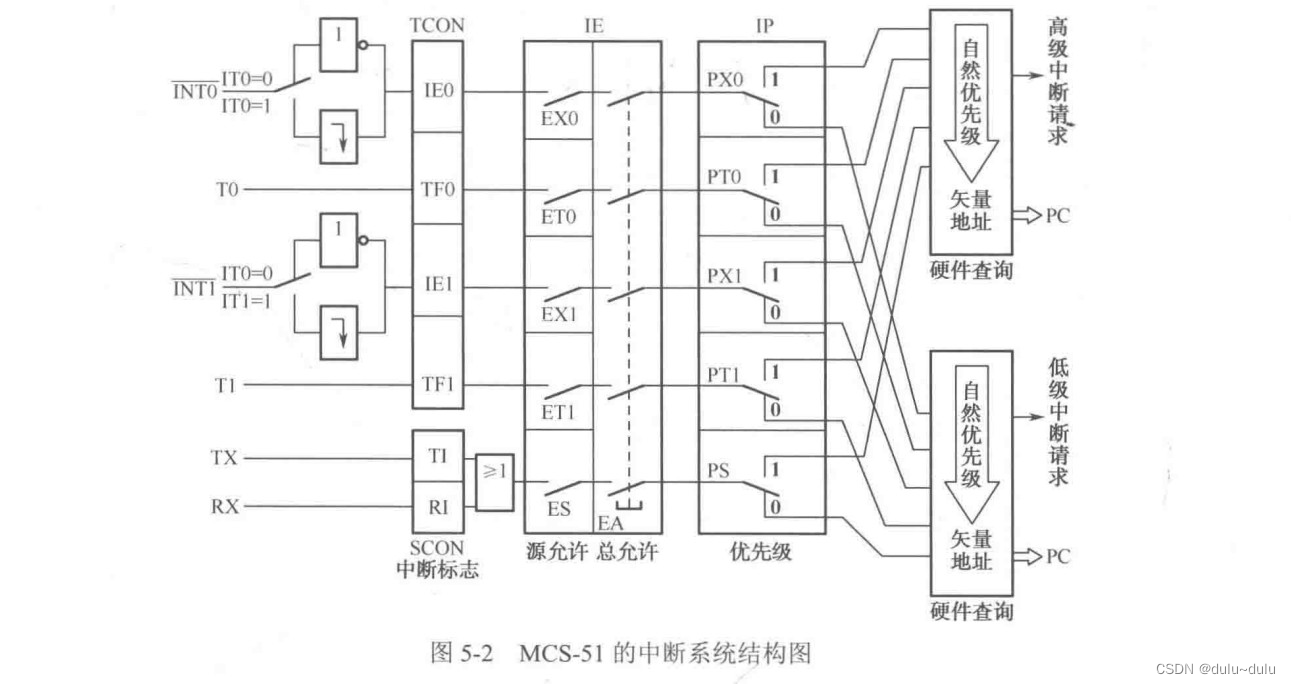

MCS-51中断系统如下所示:

1.外部中断源

8051有两个外部中断源,即外部中断0和外部中断1。它们的中断请求信号分别有引脚INT0(P3.2)和INT1(P3.3)引入。

外部中断请求有两种触发方式:电平触发方式和边沿触发方式。具体可通过对寄存器TCON的控制位IT0,IT1的设定进行选择。

•电平触发方式是低电平有效。在这种方式下,只要单片机在中断请求输入端(INT0和INTI)上采样到有效的低电平信号,就激活外部中断。

•边沿触发方式是脉冲的负跳变有效。在此方式下,CPU 在两个相邻机器周期对中请求输入端(INT0 和 INTI)进行的采样中,如果前一次检测为高电平,后一次检测为低电平,即为有效的中断请求。

2.定时器中断源

定时器中断是一种内部中断,是为满足定时或计数的需要而设置的。8051内部有两个16

位的定时/计数器,可以实现定时和计数功能。这两个定时/计数器在内部定时脉冲或从T0/T1引脚输入的计数脉冲作用下发生溢出(从全“1”变为全“0”)时,即向CPU 提出溢出断请求,以表明定时时间到或计数已满。定时器溢出中断常用于需要定时控制的场合。

3.串行口中断源

串行口中断也是一种内部中断,它是为串行数据传送的需要而设置的。串行口中断分为串行口发送中断和串行口接收中断两种。每当串行口发送或接收完一帧串行数据时,就会自动向CPU发出串行口中断请求。

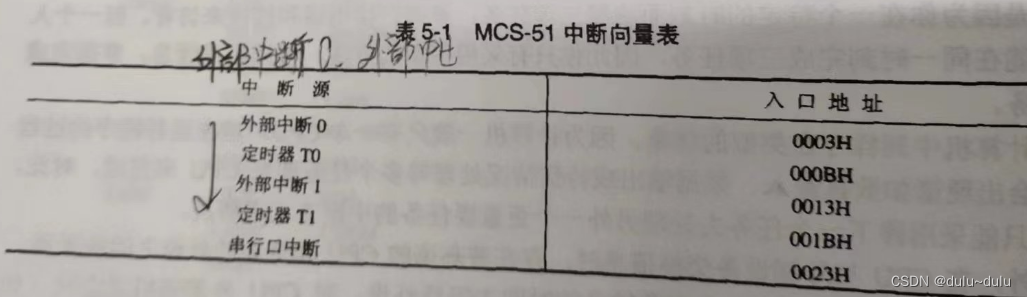

当某中断源的中断请求被 CPU 响应之后,CPU将把此中断源的入口地址装入程序计数器PC 中,中断服务程序即从此地址开始执行。此地址称为中断入口地址,亦称为中断矢量在8051单片机中各中断源与中断入口的对应关系见表:

中断控制:

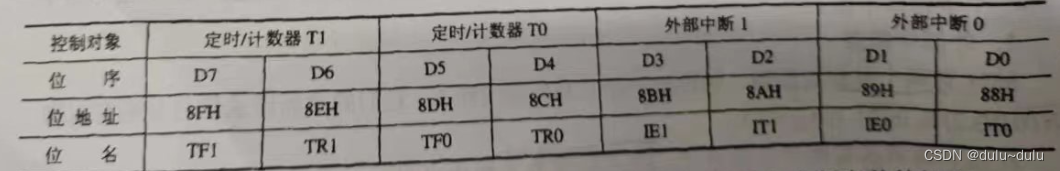

1.定时控制寄存器(TCON)

该寄存器单元地址为88H,位地址为88H~8FH,格式如下:

该寄存器具有定时/计数器的控制功能和中断控制功能,其中与中断有关的控制位共有六位:

•TF1:定时/计数器T1溢出中断标志。

当定时器 T1产生溢出中断时,该位由硬件自动置位(即TFI=1),当定时器溢出中断被CPU响应之后,该位由硬件自动复位(即TF=0)。定时器溢出中断标志位的使用有两种情况:采用中断方式时,该位作为中断请求标志位来使用。南应断后自动清零;采用查询方式时,该位作为查询状态位来使用,此时需要用性清除标志位。

•TF0:定时/计数器TO溢出中断标志。其功能与TF1类似

•IE1:外部中断1中断请求标志。

当CPU检测到INT1上中断请求有效时,IE1由硬件自动置位:在CPU应中断请求进入相应中断服务程序执行时,该位由硬件自动复位。

•IT1:外部中断1触发方式控制位。

若IT1=1,则将外部中断1设置为边沿触发方式(负跳变有效):IT1=0则将外部中断1设置为电平触发方式(低电平有效)。该位可由软件置位或复位。

•IE0:外部中断0中断请求标志。其功能与EI类似

•IT0:外部中断0触发方式控制位。其功能与ITI类似

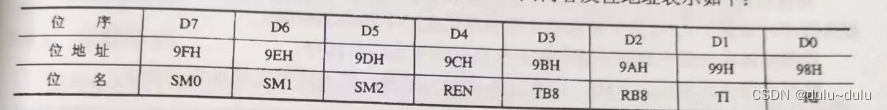

2.串行口控制寄存器(SCON)

该寄存器单元地址为 98H,位地址为 98H~9FH,其内容及位地址表示如下:

其中与中断有关的控制位共有两位:

•T1:串行口发送中断标志。

当串行口发送完一顿串行数据后,该位由硬件自动置位,但在CPU 响应串行口中断转向中断服务程序执行时,该位是不能由硬件自动复位的,用户应在串行口中断服务程序中通过指令来使它复位。

•R1:串行口接收中断标志。

当串行口接收完一帧串行数据后,该位由硬件自动置位,同样该位不能由硬件自动复位,用户应在中断服务程序中通过指令使其复位。

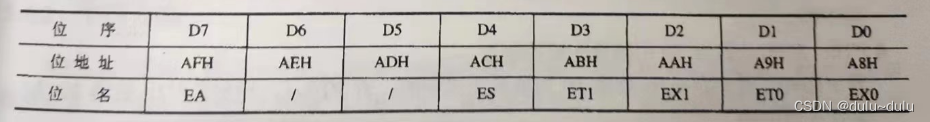

3.中断允许寄存器(IE)

该寄存器单元地址为A8H,位地址为 A8H~AFH,其内容及位地址表示如下:

•EA:CPU中断总允许位

该位状态可由用户通过程序设置: EA=0,CPU 禁止所有中断源的中断请求,亦称关中断;EA=1,CPU开放所有中断源的中断请求,但这些中断请求最终能否为 CPU响应,还取决于IE中相应中断源的中断允许位的状态。

•ES:串行口中断允许位

ES=0,禁止串行口中断:若ES=1,允许串行口中断。

•ET1:定时/计数器T1中断允许位

若ET1=0,禁止定时/计数器T1中断;若ET1=1,允许定时/计数器T1中断

•EX1:外部中断1中断允许位

若EX1=0,禁止外部中断1中断;若EX1=1,允许外部中断1中断

•ET0:定时/计数器T0中断允许位

若ET0=0,禁止定时/计数器TO中断;若ET0=1,允许定时/计数器T0中断

•EX0:外部中断0中断允许位

若EX0=0,禁止外部中断0中断;若EX=1,允许外部中断0中断。

MCS-51单片机复位以后,E寄存器中各中断允许位均被清“0”,禁止所有中断。

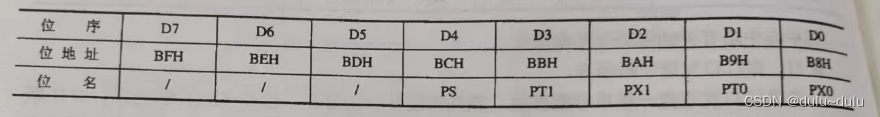

4.中断优先级控制寄存器(IP)

MCS-51 单片机的中断优先级控制比较简单,系统只定义了高、低两个优先级。用户可利用软件将每个中断源设置为高优先级中断或低优先级中断,并可实现两级中断嵌套。高优先级中断源可以中断正在执行的低优先级中断服务程序,除非在执行低优先级中断服务程序时设置了CPU关中断或禁止某些高优先级中断源的中断。

同级或低优先级中断源不能中断正在执行的中断服务程序。

IP寄存器单元地址为B8H,位地址为 B8H~BFH,其内容及位地址表示如下:

•PS:串行口中断优先级控制位。

若 PS=0,设定串行口中断为低优先级中断;若 PS=1,设定串行口中断为高优先级中断。

•PT1:定时计数器T1中断优先级控制位。

若PT1=0,设定定时/计数器 T1 为低优先级中断;若 PT1=1,设定定时/计数器T1为高优先级中断。

•PX1:外部中断1中断优先级控制位。

若PX1=0,设定外部中断1为低优先级中断,若 PX1=1,设定外部中断1为高优先级中断。

•PT0:定时/计数器T0中断优先级控制位。

若PT0=0,设定定时/计数器TO为低优先级中断;若PT0=1,设定定时/计数器TO为高优先级中断。

•PX0:外部中断0中断优先级控制位。

若PX0=0,设定外部中断0为低优先级中断,若 PX0=1,设定外部中断0为高优先级中断。

系统复位后,IP寄存器中各优先级控制位均被清“0”,即将所有中断源设置为低级中断。

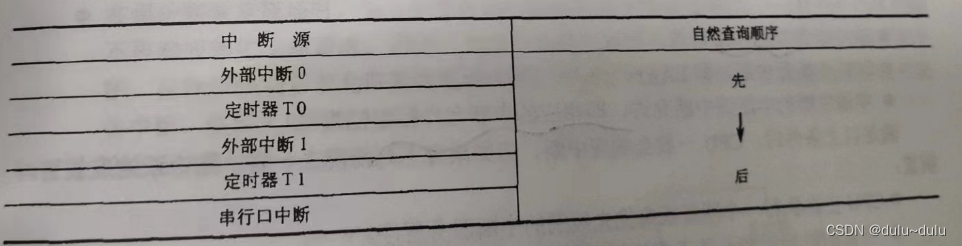

由于MCS-51单片机只有两个中断优先级,在工作过程中如果遇到几个同一优先级的中断源同时向 CPU 发出中断请求,CPU 将如何来响应中断呢?此时,CPU 将通过内部硬件查询逻辑按自然优先级顺序决定应该响应哪个中断请求,其自然优先级顺序由硬件电路形成,见表

中断处理:

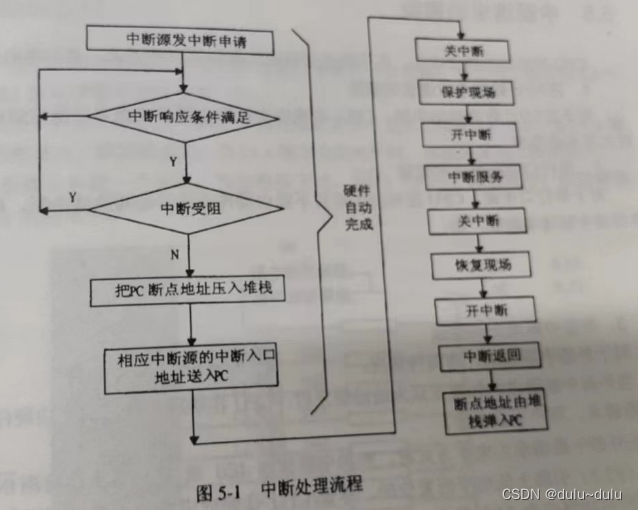

中断处理过程可分为四个阶段:中断采样、中断查询、中断响应及中断返回。

中断采样:

采样是中断处理的第一步,主要针对外部中断请求信号。因为这类中断发生在单片机的外部,要想知道是否有中断请求发生,采样是惟一可行的办法。

所谓采样,就是在每个机器周期的 S5p2期间对INT0和INT1引脚进行检测,根据检测的结果,设置相应中断标志位IE0或IE1的状态。

对于电平触发方式的外部中断请求,若采样为高电平,表明没有中断请求,对应的 IE0或I1保持为0状态;若为低电平,表明有中断请求,则使对应的 IE0或IE1置位。由于采样是直接针对中断请求信号,因此对中断请求信号就有一定的要求,其有效电平的持续时间至少要保持一个机器周期才能被采样到。

对于脉冲触发方式的外部中断请求,若在两个相邻的机器周期采样到的先高后低的电平信号,则中断请求有效,将对应的标志位 IE0或E1置位;否则,IE0或E1保持0状态。对于脉冲触发方式的外部中断请求,其高电平和低电平的持续时间都要保持至少1 个机器周期,才能被正确采样。

中断查询:

MCS-51 系列及兼单片机,在每个机器周期的最后一个状态(S6)期间,都要按先后顺序对各个中断标志位进行查询,以确定是否有中断请求发生。若查询到某个中断标志位为1,将在接下来的机器周期S1期间按优先级进行中断处理。中断系统通过硬件自动将相应的中断矢量地址装入PC,以便进入相应的中断服务子程序。

中断查询由硬件自动完成,其查询顺序为:IE0(外部中断 0)一>TF0(定时/计数器0)—>IE1(外部中断1)—>TF1(定时/计数器1)—>R1和T1(串行口收发中断)。

中断响应:

中断响应就是对中断源提出的中断请求的接受,当 CPU 查询到有效的中断请求时,紧接着就进行中断的响应。

1.中断响应的条件

CPU并非任何时刻都响应中断请求,而是在中断响应条件满足之后才会响应。CPU响应中断的条件有:

•有中断源发出中断请求。

•CPU中断开中断,即EA=1。

•申请中断的中断源中断允许,即相应的中断允许标志位为1。

满足以上条件时,CPU一般会响应中断。但如果有下列情况之一时,则中断响应被暂时搁置:

•CPU正在执行一个同级或高优先级别的中断服务程序。

•当前的机器周期不是正在执行的指令的最后一个周期,即只有在当前指令执行完毕后,才能进行中断响应。

•当前正在执行的指令是返回指令(RET,RETI)或访问IE,IP的指令。按MCS-51单片机中断系统的特性规定,在执行完这些指令之后,还应再执行一条指令,然后才能响应中断。

若存在上述任何一种情况,中断查询结果即被取消,CPU不响应中断请求而在下一机器周期继续查询,否则,CPU在下一机器周期响应中断。

2.中断响应

中断响应过程包括保护断点和将程序转向终端服务程序的入口地址(通常称矢量地址),首先,中断系统通过硬件自动生成长调用指令(LACLL),该指令将自动把断点地址压入堆栈保护(不保护累加器 A、状态寄存器 PSW 和其他寄存器的内容),然后,将对应的中断入口地址装入程序计数器 PC(由硬件自动执行),使程序转向该中断入口地址,执行中断服务程序。MCS-51 系列单片机各中断源的入口地址由硬件事先设定,矢量地址的分配见表所示。例如对于定时/计数器T0的中断响应,自动生成的长调用指令为: LCALL 000BH

由于每个中断源的中断区只有 8 个单元,一般难以安排一个完整的中断服务程序。因此通常是在各中断区入口地址处放置一条无条件转移指令,使程序转向在其他地址存放的中断服务程序。

3.中断处理

中断处理就是执行中断服务程序。中断服务程序从中断入口地址开始执行,到返回指令“RETI”为止,一般包括两部分内容:一是保护现场,二是完成中断源请求的服务。通常主程序和中断服务程序都会用到累加器 A、状态寄存器 PSW 及其他一些寄存器,当CPU 进入中断服务程序用到上述寄存器时,会破坏原来存储在寄存器中的内容,一旦中断返回,将会导致主程序的混乱。因此,在进入中断服务程序后,一般要先保护现场,然后,执行中断处理程序,在中断返回之前再恢复现场。

编写中断服务程序时还需注意以下几点:

•各中断源的中断入口地址之间只相隔 8 个字节,容纳不下普通的中断服务程序,因此,在中断入口地址单元通常存放一条无条件转移指令,可将中断服务程序转至存储器的其他任何空间。

•如果在执行当前中断程序时想禁止其他更高优先级中断,需先用软件关闭CPU中断,或用软件禁止相应高优先级的中断,在中断返回前再开放中断。

•在保护和恢复现场时,为了不使现场数据遭到破坏或造成混乱,一般规定此时 CPU不再响应新的中断请求。因此,在编写中断服务程序时,要注意在保护现场前关中断,在保护现场后若允许高优先级中断,则应开中断。同样,在恢复现场前也应先关中断,恢复之后再开中断。

4.中断的响应时间

中断响应时间是指从中断请求标志位置位,到CPU 开始执行中断服务程序的第一条指令所持续的时间。CPU 并非每时每刻对中断请求都予以响应,另外,不同的中断请求其响应时间也是不同的,因此,中断响应时间形成的过程较为复杂。以外部中断为例,CPU在每个机器周期的S5P2期间采样,其输入引脚INT0或INT1,如果中断请求有效,则置位中断请求标志位 IE0或IE1,然后在下一个机器周期再对这些标志位进行查询。这就意味着中断请求信号的低电平至少应维持一个机器周期。

这时,如果满足中断响应条件,则 CPU 响应中断请求,在下一个机器周期执行一条硬件长调用指令“LACLL”,使程序转入中断矢量入口。该调用指令执行时间是两个机器周期,因此,外部中断响应时间至少需要3个机器周期,这是最短的中断响应时间。

如果中断请求不能满足前面所述的三个条件而被搁浅,则中断响应时间将延长。例如一个同级或更高级的中断正在进行,则附加的等待时间取决于正在进行的中断服务程序的长度。如果正在执行的一条指令还没有进行到最后一个机器周期,则附加的等待时间为 1~3个机器周期(因为一条指令的最长执行时间为4个机器周期)。

5.中断返回

中断返回是指中断服务完后,计算机返回原来断开的位置(即断点),继续执行原来的程序。中断返回由中断返回指令“RETI”来实现。该指令的功能是把断点地址从堆栈中弹出送回到程序计数器 PC。此外,还通知中断系统已完成中断处理,并同时清除优先级状态触发器。特别要注意不能用“RET”指令代替“RETI”指令。

中断请求撤销:

CPU响应某中断请求后,在中断返回前应该撤除该中断请求,否则将引起再次中断。

1.定时/计数器中断请求的撤除

对于定时/计数器溢出中断,CPU在响应中断后由硬件电路自动撤除该中断请求,用户对此可不必考虑。

2.串行口中断请求的撤除

对于串行口中断,CPU在响应中断后不能由硬件电路自动撤除该中断,应由用户利用软件将该中断请求撤除,如:

3.外部中断请求的撤除

对于外部中断请求,有两种情况:

当外部中断请求的触发方式为边沿触发时,CPU在响应中断之后会由硬件电路自动撤除该中断请求,用户不必考虑。

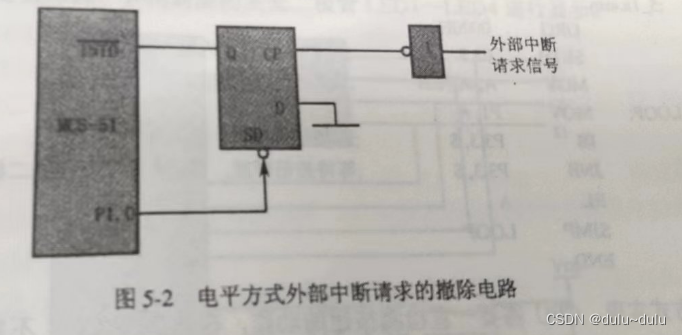

当外部中断请求为电平方式时,外部中断标志 IE0或 IE1 是依靠检测INT0(P3.2)或INTI(P3.3)引脚上低电平而置位的。尽管 CPU 在应中断时相应中断标 IE0或IE1也能被硬件自动复位为“0”状态,但如果外部中断源不能及时撤除它在INT0(P3.2)或INT1(P3.3)引脚上的低电平,就会再次使已经变成“0”的中断标志 IE0或IE1置位为“1”,这是绝对不允许的。因此,电平触发型外部中断请求的撤除需要硬件、软件配合来实现。

如图为一种可供采用的电平触发型外部中断请求的撤除电路。

图中,用D触发器锁存外部中断请求低电平,并通过触发器的Q端送到INT0引脚,所以增加的 D 触发器不影响中断请求。中断响应后,为了撤除中断请求,可利用 D触发器的异步置位端来实现。将

接到单片机的一个口线上 (P1.0),只要 P10输出一个负脉冲就可以使 D触发器置 1,从而撤除了低电平的外部请求信号。所需负脉冲可通过在中断服务程序中增加如下2条指令来得到:

2160

2160

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?