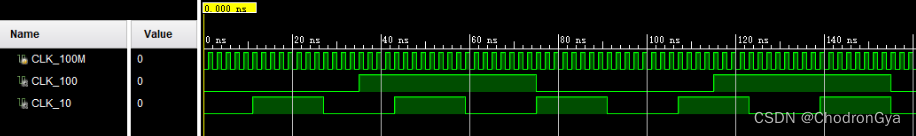

➢可以采用一个寄存器作计数器进行分频,当计数器数满指定数字时,让输出信号翻转,构成分频信号。

➢ 10Hz与100Hz分频器就是采用这种方法,取100MHz的时钟信号,经过第一次分频,得到频率为1Khz的clk_1k寄存器信号,对这个 1KHz的信号进行再次分频,最终得到10Hz与100Hz的两个分频信。

项目源码:

module clk_div_10_100(

input clk_100M,

output clk_100,

output clk_10

);

reg[15:0] cnt_khz;

reg[7:0] cnt_100hz;

reg[7:0] cnt_10hz;

reg clk_1k;

reg clk_100_reg;

reg clk_10_reg;

initial

begin

cnt_khz=0;

cnt_100hz=0;

cnt_10hz=0;

clk_1k = 0;

clk_100_reg = 0;

clk_10_reg = 0;

end

//100000分频,输出clk_1k

always@(posedge clk_100M)

begin

//if(cnt_khz==16'hc34f) // 49999 c34F,100000分频,综合实现时使用

if(cnt_khz==1) //4分频,仿真时使用

begin

clk_1k <= ~clk_1k;

cnt_khz <= 0;

end

else

cnt_khz <= cnt_khz +1;

end

//100分频,输出clk_10_reg

always @(posedge clk_1k)

begin

//if(cnt_10hz ==49) //100分频,综合实现时使用

if(cnt_10hz ==1) //4分频,仿真时使用

begin

clk_10_reg <= ~clk_10_reg;

cnt_10hz <=0;

end

else

cnt_10hz <= cnt_10hz + 1;

end

//10分频,输出clk_100_reg

always @(posedge clk_1k)

begin

if(cnt_100hz == 4)

begin

clk_100_reg <= ~clk_100_reg;

cnt_100hz <=0;

end

else

cnt_100hz <= cnt_100hz + 1;

end

assign clk_100 = clk_100_reg;

assign clk_10 = clk_10_reg;

endmodule仿真文件:

module clk_div_10_100_tb( );

reg CLK_100M;

wire CLK_100;

wire CLK_10;

/*****************begin********************/

// 调用clk_div_10_100模块

clk_div_10_100 u1(

.clk_100M(CLK_100M),

.clk_100(CLK_100),

.clk_10(CLK_10)

);

// 生成占空比50%的时钟波形

parameter PERIOD = 2;

always #(PERIOD/2) CLK_100M = ~CLK_100M;

// 激励信号随时间变化

initial

begin

CLK_100M = 1'b0;

end

endmodule

677

677

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?