目录

预习

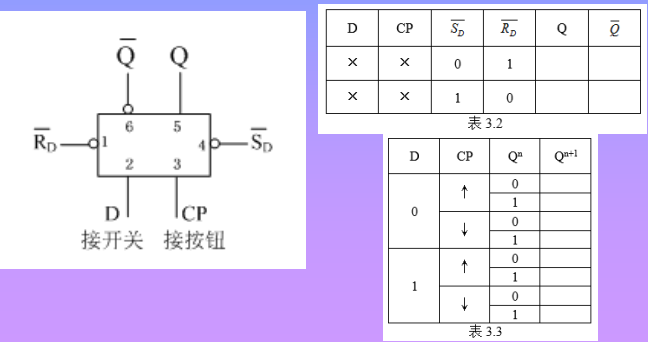

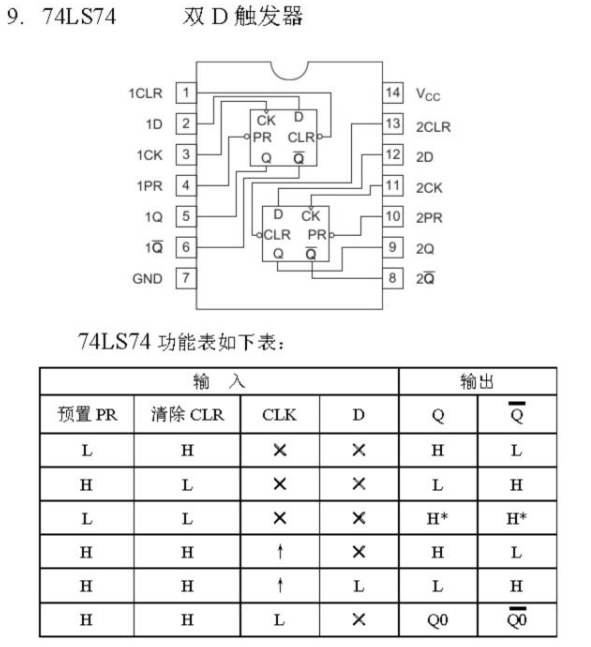

1.集成D触发器功能测试

(1)测试异步置位端~SD和异步复位端~RD的功能

(2)测试D触发器的逻辑功能

1、是异步复位端,作用是令Q=0,

=1;

是异步置位端,作用是令Q=1,

=0。

2、当CP=0时,触发器不起作用,Q与Q的反变量保持不变,CP=1时,触发器才实现相关功能。

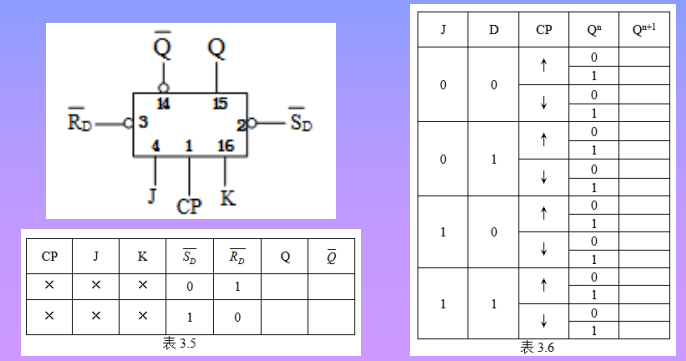

2.集成J-K触发器功能测试

(1)测试异步置位端~SD和异步复位端~RD的功能

(2)测试J-K触发器的逻辑功能

同问题1

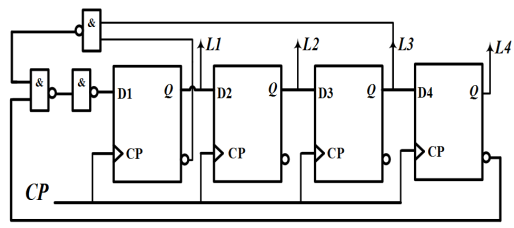

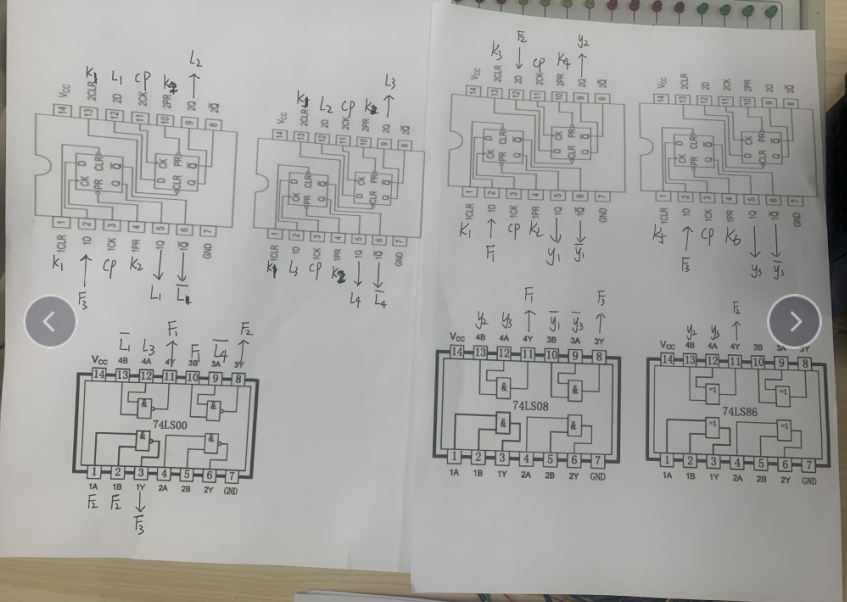

3.移位寄存器型计数器电路分析

(1)分析下图所示的移位寄存器型计数器电路,写出激励函数、状态表和状态转换图。

(2)根据电路图和器件手册,在电路图中并标出引脚号。

注意:D触发器的置0和置1端不能悬空。

(3)连接电路,检查电路无误后接通电源进行实验,记录实验结果并检查实验结果是否正确。

激励函数:反映了存储电路的输入(或者叫组合电路内部输出,即上图的D1 D2 D3 D4)与电路输入(比较特殊,上图无输入)和状态(Q1 Q2 Q3 Q4)之间的关系。

通常不把CP当做输入,而是把它当成一种默认的时间基准。//可以看看课本

//D1左边一个与非门漏了一个输入,应该是自己与自己与非,当然,结果无影响。

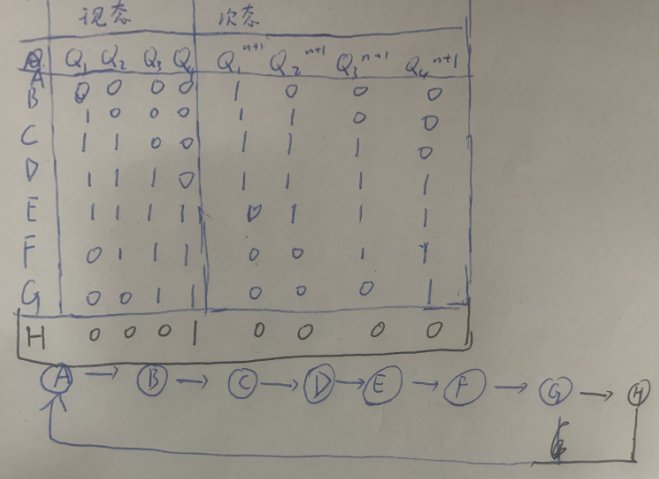

状态表:该电路次态与输出一致,可用moore型状态表。

该电路很特殊,无输入,次态与输出一致,可以大幅简化状态表

状态转换图也无输入。

置0端和置1端的作用:初始化Q1Q2Q3Q4的值,所以不能悬空。

状态表和状态图

4.同步模五计数器电路设计

(1)用D触发器和门电路设计同步模五计数器,电路要求能预置初始状态,并具有自恢复功能。

(2)输入为单脉冲,输出接LED指示灯或七段译码驱动器的输入端。画出电路图,并标出引脚号。(3)连接电路,检查电路无误后接通电源进行实验,记录实验结果。

提示:用3个D触发器(2片74LS74)

1个异或门(1片74LS86)2个与门(1片74LS08)

(不同设计方案可能不一样,允许提供以前用过的芯片)

注意:充分利用无效状态,分析并修改电路并保证电路具有自恢复功能

预置初值的功能:利用置1和置0端的作用

功能表:L即低电平0,H即高电平1。1-反RD,2-D,3-CP,4-反SD,5-Q,6-反Q。

提示,状态图为000->001->010->011->100->000

画出状态图,列出真值表,用卡诺图来找出次态函数表达式。

实验

本次实验比较顺利(主要是队友强)。但中间也有过一些曲折(问题3)。

1、状态表画错了(问题3现在的状态表是我改后的了)。因为当时列出了16个状态,没有发现其中的8个状态是一种环形。

2、没有落实问题3.(2)的要求。下面是好的做法:

3、将7400用成了7408,并检查了两个小时没出结果。

正确的实验结果应该是灯从左到右(或从左到右)挨个亮,从不亮到全亮;然后再从左向右挨个灭。从全亮到全灭。而我们只有全亮到全灭的过程。老师说极可能是D芯片(7474)的R\S端出了问题。因为灯泡亮,说明开关电线电源没问题;因为CP按一下灯会变换,所以CP也没问题;只有可能是芯片,而且有一半是对的,另一半没有结果,说明实现另一半结果的功能有缺失。结果队友换了十几个芯片都没有结果。最后我一看,原来用错了芯片。的确是有缺失,与非门用成了与门。

收获

1、检查要检查芯片、电线、面包板、灯泡等等,其中芯片故障率最大,为检查的重点。

2、CP、R、S端尽量用横着的25个为一组的小孔连。

3、如果按CP,灯泡变化过快,可以用一个类似收音机的东西观察输出的电平信号。有的同学就这样通过的助教测试。

325

325

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?