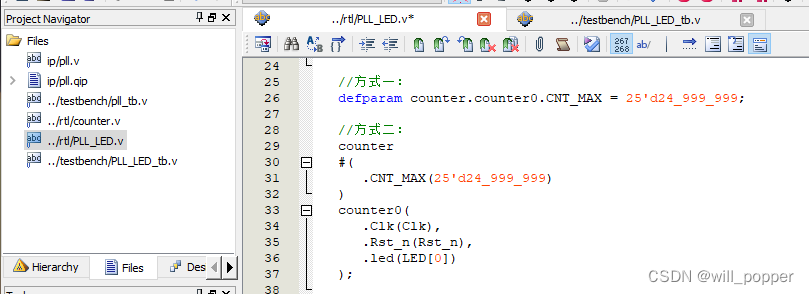

方式一和方式二都能达到例化文件中参数的目的;

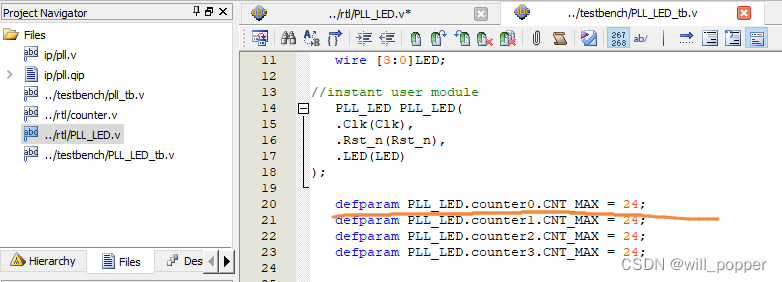

但是方式一中的defparam会影响到 tb 文件中的 defparam,如果 tb 文件中也有一段代码如下图:

则在仿真中 CNT_MAX 的数值会是文件 PLL_LED 中的数值,只有屏蔽了 PLL_LED 中对应代码后,CNT_MAX 才会是 tb 文件中的数值。(虽然tb文件不会影响到板级验证,但会影响到仿真结果)。

如果用方式二,则 tb 文件中的 defparam 级别会高于 PLL_LED 中的例化代码,所以仿真结果是以 tb 文件中的参数为准,而在板级验证中则可以顺利使用 PLL_LED 中的修改参数。

/************************************/

总结:为了同时保证实际逻辑设计和仿真验证时对参数的修改能够共存,互不影响,在实体模块设计中,使用参数例化的方式修改被例化模块中的参数(即方式一)。在仿真验证用的testbench中,使用defparam语句来修改对应的参数(方式二)。

1195

1195

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?