Implementing BIRA and BISR Logic

本节介绍如何在 circuit 中插入 repair logic。重点是插入 BISR 逻辑。只要内存库文件中存在 RepairAnalysis 包装器,并且该实例的 repair_analysis_present 属性未设置为 “Off”,就会在内存 BIST 逻辑(控制器和接口)的其余部分同时为内存实例生成 BIRA 逻辑。

主要的 BISR 逻辑插入任务如下: 1. 在block中插入 BISR 链 2.将 BISR 控制器连接到现有的 BISR 链 3.将 BISR 控制器连接到外部fuse:如果实施了软修复方法,则不需要fuse 4. 将 BISR 控制器连接到系统逻辑

前两个任务用于自下而上的设计方法,其中 BISR 链插入电路块(或内核),然后在芯片顶层连接到 BISR 控制器。这是插入 repair logic(修复逻辑)最常用的方法。

Inserting BISR Chains in a Block

若设计中例化的存储器在其存储器库(Memory Library)文件中声明了冗余资源(如备用行/列),则会自动插入 BISR(内建自修复)链。与可修复存储器相关的 BISR 寄存器将互联组成扫描链(Scan Chains)。

Assigning Memories to Power Domains

默认情况下,所有可修复存储器(Repairable Memories)均归属同一电源域(Power Domain),且仅生成单一 BISR 链。若存在多个电源域,则需构建多个独立的 BISR 链。存储器例化(Memory Instance)的电源域由其 bisr_power_domain_name 属性决定,该属性可通过以下两种方式指定:

推荐方法是通过 read_upf 或 read_cpf 命令加载设计的电源管理文件(UPF/CPF),以自动解析电源域。该文件需在 Tessent Shell 环境初始化阶段完成加载,举例如下:

![]()

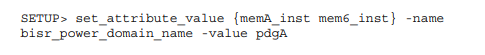

该方法会读取设计模块 moda 对应的 UPF 文件,并自动为所有存储器设置 bisr_power_domain_name 属性。若需手动配置,则可通过 set_attribute_value 命令直接设定该属性。例如以下命令:

将内存实例 memA_inst 和 mem6_inst 分配给标记为 pdgA 的电源域。

注意:“none” 为保留字符串,禁止作为电源域组(PowerDomainGroup)标签。详细约束请参考工具手册中的 PatternsSpecification MemoryBisr/Controller/power_domain_group_labels 属性说明。

若子模块(Sub-Block)或物理块(Physical Block)内含可修复存储器,其内部可能部署多个 BISR 扫描接口。仅在其例化层级设置 bisr_power_domain_name 属性,无法将内部 BISR 链绑定至目标电源域组(PowerDomainGroup)。需通过以下方式显式指定:

在每条目标 BISR 链的 BISR_SI(扫描输入)引脚上单独设置 bisr_power_domain_name 属性。

示例命令:

# 将子模块 blockA 内的 pdgA_bisr_si 引脚绑至电源域组 "pdgA"

SETUP> set_attribute_value {core/blockA/pdgA_bisr_si} -name bisr_power_domain_name -value pdgA 此操作将子模块 blockA 中 pdgA_bisr_si 引脚关联的 BISR 链划归电源域组 pdgA。

该模块内其余 BISR 链将继承子模块 ICL(Instrument Connectivity Language)引脚属性中声明的默认电源域组。

子模块的 BISR_SI 引脚默认电源域组,源自其 process_dft_specification 阶段定义的值。执行 extract_icl 命令时,BISR_SI 电源域组名称将以引脚属性的形式固化在子模块的 ICL 描述中。通过手动指定电源域组,可对大型电源域进行逻辑细分,实现以下优化:在系统上电时,并行修复不同子域中的存储器子集,缩短修复时间。按需激活目标子域的修复逻辑,降低待机功耗。

Controlling the BISR Chain Order

BISR链的连接顺序由 BISR段顺序规范文件(BisrSegmentOrderSpecification) 定义,该文件通过明确列出存储器实例(Memory Instances)的顺序来配置链结构。具体排序规则如下:若提供DEF文件:工具将基于存储器物理坐标(Memory Coordinates)优化布线算法(Routing Algorithm),按空间邻近性生成BISR段顺序。若无DEF文件:在每个电源域组(Power Domain Group)内,按存储器实例名称的字母顺序(Alphabetical Order)排序。

该规范文件包含在自动生成的<设计_name>.bisr_segment_order中,生成条件为:进入分析模式(通过无DRC错误的check_design_rules触发)或手动执行create_bisr_segment_order_file命令,文件路径为当前工作目录。

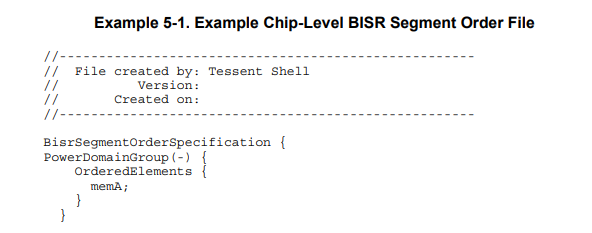

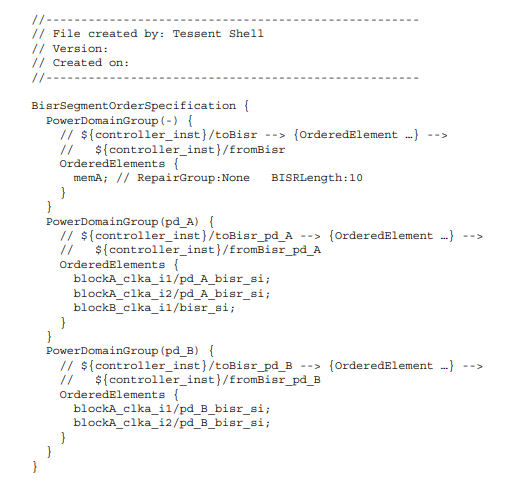

图5-1展示了一个芯片级BISR段顺序文件的内容示例,其中定义了三个电源域(Power Domain)。默认电源域(Default Power Domain)将分配给所有未显式绑定到指定域的可修复存储器,该域通常关联设计中供电永不关闭(如常开电源域)的电路模块。

若默认BISR链顺序不尽人意,可通过两种方式对BISR链排序进行调整。首选方法是使用read_def命令读取与设计对应的DEF文件,创建BISR段排序,MemoryBIST会基于存储器布局以及物理块或子块的BISR_SI引脚坐标自动对该排序进行优化。物理块和子块的MemoryBIST插入以及BISR链排序是分开进行的。您应在Tessent Shell的设置模式下,在读取其他设计文件的同时加载该文件。例如这个命令

SETUP> read_def modA.def

读取与设计modA对应的DEF文件。MemoryBIST会根据在DEF文件中找到的存储器布局和块BISR_SI引脚布局信息来确定BISR链的排序。如果某个块的BISR_SI引脚未指定坐标,但其父块指定了坐标,MemoryBIST会使用父块的坐标来进行排序优化。

此外,您还可通过BisrElement及BisrElement/Pipeline封装单元独立调整BISR寄存器及相关流水线寄存器的布局,并指定其插入特定父设计实例中。工具将根据DEF文件中记录的父设计BISR_SI引脚布局信息,自动确定这些寄存器的BISR链排序关系。

第二种方式需要您在运行process_dft_specification命令前,手动修改<设计名称>.bisr_segment_order文件中的存储器例化名称顺序。若需在同一Tessent Shell会话或后续会话中重新运行check_design_rules,并希望复用已修改的<设计名称>.bisr_segment_order文件,则必须在仍处于设置模式时通过set_dft_specification_requirements命令显式声明。例如:

SETUP> set_dft_specification_requirements -bisr_segment_order_file modA.bisr_segment_order

该命令表示工具应保留modA.bisr_segment_order文件,并在下次执行create_dft_specification命令时,使用其内容确定BISR链顺序。BISR段排序文件的文件名可任意指定,无需使用默认名称。

process_dft_specification命令执行后,会在当前目录生成带有".annotated"后缀的带注释BISR段顺序文件。该注释文件的另一副本将存储在tsdb_outdir目录下的以下路径中:

<tsdb_outdir>/instrument/<design_name><design_id>_rtl_mbisr.instrument/<design_name><design_id>_mbisr.bisr_segment_order

当前目录中的注释文件供您在需要重新调整BISR链顺序时使用,而TSDB(测试数据库)中的BISR段顺序文件则用于记录已实现的BISR链结构,作为参考基准。

注释文件包含指示修复组成员关系及BISR链寄存器长度的注释信息。例如,下方代码段展示了图5-1所示BISR段顺序文件的注释版本:

PowerDomainGroup封装单元的首条注释行有助于理解BISR链顺序逻辑。该注释表明:BISR链扫描输入信号将按自上而下的顺序移入OrderedElement条目,最终到达BISR链扫描输出端。

此外,当前设计中的每个存储器实例均带有注释,标明其所属的修复共享组(若存在)以及该存储器或修复共享组关联的BISR寄存器长度。在上例中,memA不属于任何修复共享组,其对应的BISR寄存器长度为10。关于含修复共享机制的带注释物理块BISR段顺序文件示例,请参见"BISR段顺序文件"专题中的说明。

Turning Off the Insertion of BISR Registers

可通过执行set_memory_instance_option命令,将use_in_memory_bisr_dft_specification选项设为off,以禁用特定存储器实例的BISR寄存器生成。例如:

SETUP> set_memory_instance_option blockA_clka_i1/mem4 use_in_memory_bisr_dft_specification off

此示例将禁用存储器实例mem4的BISR寄存器生成——即使该存储器具备备用资源,此操作仍会生效。需注意,该选项极少使用。

若需完全禁用设计中的BISR插入功能,可执行以下命令:

set_dft_specification_requirement -memory_bisr_chains off

Excluding Child Block BISR Chains

当父设计未实现存储器修复功能,但集成了已包含BISR链的子模块或物理块时,必须将这些BISR链悬置处理(即不连接且保持信号固定)。若无法通过对子模块重新运行禁用BISR链插入的存储器BIST DFT流程,则应采用下述方法实现链隔离。

排除子模块BISR链的首步操作是:在运行create_dft_specification命令前,从<设计名称>.bisr_segment_order文件中移除该链的连接定义。该文件最初由check_design_rules命令生成。若需在后续重新运行check_design_rules时继续使用修改后的<设计名称>.bisr_segment_order文件,则须在设置模式下通过set_dft_specification_requirements命令声明。例如:

SETUP> set_dft_specification_requirements -bisr_segment_order_file modA.bisr_segment_order

该命令指示工具保留modA.bisr_segment_order文件,并在下次执行create_dft_specification时,根据其内容确定BISR链的组成与顺序。需注意,bisr_segment_order文件的命名可自由指定,无需遵循默认命名规则。

第二步需使用set_attribute_value命令,为目标引脚添加allowed_no_destination连接规则选项。例如:

set_attribute_value [get_icl_ports pd_B_bisr_so -of_modules core] -name connection_rule_option -value allowed_no_destination

此步骤通过允许信号悬空的规则定义,防止因意外从.bisr_segment_order文件中移除BISR链连接而导致部分设计无法修复。若未完成此步骤,工具将报出ICL(集成电路锁存)提取错误,提示BISR链不可访问。

对于每个需排除的子模块BISR链,需按需重复上述两步操作。

Generic Fuse Box

多家供应商提供的熔丝盒(fuse box)具有大量互不兼容的接口与协议。为应对此类复杂性,熔丝盒的读写协议需封装在专用接口模块中。

该接口需为每个熔丝盒单独设计,但针对特定工艺只需开发一次。此外,Siemens EDA可基于特定工艺提供现成接口,或在满足条件时开发新接口模块。

保险丝盒(Fuse Box)可内建于BISR控制器内部实例化,也可外置于BISR控制器之外。其位置由DftSpecification中的MemoryBisr Controller/fuse_box_location属性控制。推荐的设计流程是:无论采用内置或外置保险丝盒方案,在处理DftSpecification前都应整合供应商提供的保险丝盒及接口模块。需特别注意的是,该操作是外置保险丝盒方案的强制要求。若在内部保险丝盒实例化时未遵循推荐设计流程,工具将自动生成并使用通用保险丝盒接口模块,但需注意该模块仅适用于基础仿真验证目的。

• Internal Fuse Box

当保险丝盒内置于BISR控制器,且仅存在单个TCD FuseBoxInterface封装模块(tcd_fusebox)时:若未在DftSpecification中显式指定fuse_box_interface_module属性,工具将自动从tcd_fusebox模块推断该属性值。若存在多个tcd_fusebox库文件,则必须显式声明fuse_box_interface_module属性。

若未遵循推荐设计流程(即未提供tcd_fusebox模块),且DftSpecification中也未指定fuse_box_interface_module属性,工具将生成通用保险丝盒接口模型。该模型包含一个封装特定熔丝盒读写协议的通用保险丝盒,生成的通用接口与保险丝盒模型将以模板文件形式存在,且仅用于仿真用途。

• External Fuse Box

当保险丝盒外置于BISR控制器时,设计中必须实例化熔丝盒接口模块,以便为BISR控制器提供有效的熔丝读写接口。通常,当熔丝盒需要用于内存修复之外的多重功能共享时,建议采用外置方案。更多实现细节请参阅《BISR控制器与外部熔丝盒连接指南》章节。

Fuse Box Interface Signals

BISR控制器与熔断盒接口之间的交互非常简单。如果在DftSpecification中将Controller/fuse_box_location参数设置为external(外部),则会在熔断盒接口与BISR控制器之间建立连接。若fuse_box_location设置为internal(内部),且未在tcd_fusebox包装器或DftSpecification的fuse_box_interface_module属性中指定熔断盒接口模块,则BISR控制器将实例化通用熔断盒接口模块,且其端口名称必须与TSDB中以下文件生成的端口名称一致:

tsdb_outdir/instruments/<design_name>_generic_fusebox_interface.v

表5-6列出了BISR控制器用于与熔断盒接口通信的所有熔断盒接口端口。该表格同时提供了接口的输入/输出引脚、对应的通用熔断盒名称及其功能描述。所有控制信号均采用高电平有效端口极性。

Fuse Box Protocol

所有熔断盒均支持两种通用操作:读取和写入。非可寻址熔断盒还具备两种特有操作:数据传输和编程操作。对于非可寻址熔断盒,必须将TCD FuseBoxInterface/programming_method属性或DftSpecification AdvancedOptions/FuseBoxOptions/programming_method设置为缓冲模式(buffered)。此时还需将额外的programFB信号连接至fuse box interface。

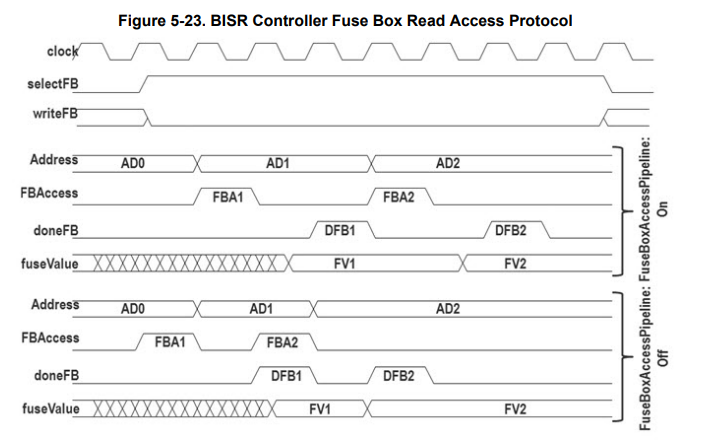

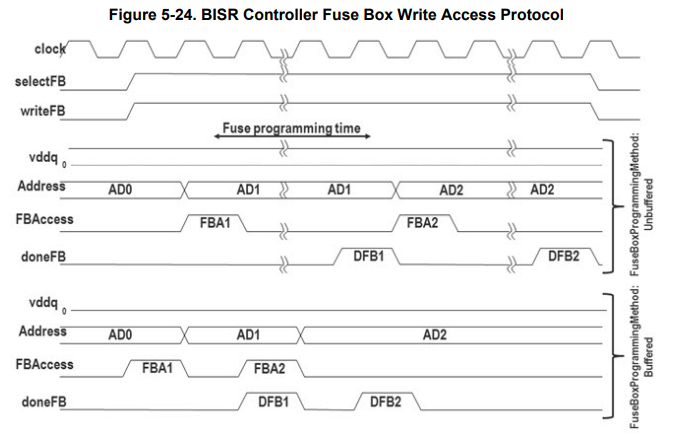

图5-23展示了BISR controller在读操作周期内访问fuse box的协议,图5-24展示了写操作周期的协议。这些图未显示programFB信号,但若存在该信号,则其值默认为0。

除doneFB信号和fuseValue输出外,表5-6中"通用Fuse Box端口名称"列所列信号均由BISR控制器生成。doneFB和fuseValue输出由通用fuse box接口模块内部产生。所有BISR控制器输出信号(selectFB、writeFB、FBAccess、address)在时钟上升沿发生跳变。当fuse box实例化于BISR控制器内部(fuse_box_location:internal)时,doneFB和fuseValue输出在时钟上升沿被采样;当fuse box位于外部(fuse_box_location:external)时,这两个信号则在时钟下降沿被采样。

注意:fuse box接口在doneFB信号上仅维持一个时钟周期的逻辑高电平,随后恢复为逻辑低电平。

当fuse box集成于BISR控制器内部时,fuse box接口使用的时钟可与控制器时钟实现平衡。此时所有触发器(flops)均可在时钟上升沿同步更新和采样,从而实现更高的操作速度。

当fuse box位于BISR控制器外部时,时钟可能存在不平衡状态。控制器采用稍有不同的时序机制:输出信号仍保持时钟上升沿跳变特性,但输入信号(如doneFB和fuseValue)会在时钟下降沿进行采样,以补偿控制器与fuse box接口之间的潜在时钟偏移(skew)。这种情况下可能导致整体操作速度降低。

图5-23展示了两种波形变体,其特性取决于TCD FuseBoxInterface/align_access_en_with_address属性或DftSpecification AdvancedOptions/FuseBoxOptions/align_access_en_with_address属性的设置。当属性值设为on时,FBAccess脉冲会在首个周期与待读取地址对齐;设为off时,FBAccess脉冲会比待读取地址提前一个周期发生,从而允许更快速度的fuse box访问。auto模式下默认行为为:当fuse_box_location设置为external时采用on模式,设置为internal时采用off模式。另一显著区别在于FBAccess脉冲可能与前次访问的doneFB脉冲产生重叠。如图5-23所示,FBA2与DFB1发生在同一时钟周期内。

工具在启用硬增量修复功能时(通过将DftSpecification max_fuse_box_programming_sessions属性设置为大于1的值),会强制将align_access_en_with_address属性设为on状态。当执行硬增量修复时,BISR控制器会在selectFB信号生效后的首个时钟周期内,同步驱动selectFB信号并从fuse box读取测试插入标志(具体时序结构参见图5-52所示的fuse box架构)。这种初始操作模式可能无法满足某些eFuse接口的最小时序裕量要求。通过使能FBAccess与Address信号的对齐机制,可在selectFB与FBAccess信号之间建立额外的时序裕量,从而确保与当前eFuse接口电路的互操作性。当不启用硬增量修复功能时,BISR控制器会在assert selectFB信号后的多个时钟周期才开始执行初始eFuse访问操作,此时selectFB与FBAccess之间的时序裕量已满足eFuse时序规范,无需启用align_access_en_with_address属性。

图5-24展示了两种编程方法的写操作波形:非缓冲模式(默认模式)和缓冲模式。该模式选择通过设置FuseBoxInterface/programming_method或DftSpecification AdvancedOptions/FuseBoxOptions/programming_method属性实现。采用非缓冲模式的写操作耗时显著长于缓冲模式,这是因为非缓冲模式下熔丝实际被烧断,典型编程时间在微秒级量程,且在此操作期间施加fuse box编程电压(vddq)。而缓冲模式仅向fuse box接口的寄存器写入数据,该操作可在两个时钟周期内完成,且此模式下不施加编程电压。

当BISR控制器被启用时,selectFB信号将被驱动为高电平。writeFB信号被置高以指示BISR控制器正在准备执行fuse box写操作周期。随后BISR控制器会设置Address端口(需写入的熔丝地址)并驱动FBAccess端口在单一时钟周期内保持高电平,该端口用于触发写操作周期。BISR控制器将维持Address、writeFB和selectFB信号的稳定状态,直至通用fuse box接口在doneFB输出端口发送逻辑高电平信号,该信号状态表明当前写操作周期已完成。

图5-25展示了采用缓冲编程方法时启动传输(Transfer)和编程(Program)操作的时序协议。在传输操作和编程操作期间,programFB信号保持高电平,这与读取(Read)和写入(Write)操作期间programFB的低电平状态形成对比。writeFB信号在传输操作期间为低电平,在编程操作期间转为高电平。selectFB信号在所有操作期间均保持高电平,但会在每次操作切换时翻转电平状态,这种特性有助于明确标识每个操作的起始边界。这些通过FBAccess和doneFB信号实现的操作不会在TAP控制器与fuse box接口之间建立握手机制。仿真测试平台或测试程序会包含与操作持续时间相对应的暂停周期。

在IEEE 1149.1标准的BISR(Built-In Self-Repair)操作中,"fuse编程(Program)"和"fuse写入(Write)"具有明确的技术区分,其差异主要体现在操作对象、物理效果和时序特性上:

1. 操作对象差异

- 写入(Write):指通过FBAccess信号触发的寄存器级数据加载,仅修改fuse box接口的缓冲寄存器(buffer register)内容,不涉及物理熔丝状态改变。如图5-24所示,该操作在两个时钟周期内完成,无需施加编程电压(vddq)。

- 编程(Program):指通过programFB信号驱动高电平触发的物理熔丝烧断操作,需要将缓冲寄存器中的数据转移到实际熔丝阵列中。如图5-25所示,该操作需要先执行传输(Transfer)阶段的寄存器写入,再通过Program阶段的高压脉冲实现熔丝永久性修改。

2. 物理效果差异

- 写入操作是可逆的数字信号操作,仅影响逻辑状态,断电后数据丢失(缓冲模式下)。

- 编程操作是不可逆的物理改变,通过vddq电压烧断熔丝(典型值≥2.5V),实现永久性存储(如芯片ID、配置信息等关键数据)。

3. 时序特性差异

- 写入操作:在缓冲模式下,仅需2个时钟周期(TCK)即可完成寄存器更新(如图5-24的Write cycle)。

- 编程操作:包含两个阶段(Transfer + Program),需要多个时钟周期(具体数量取决于熔丝阵列规模)。

4. 应用场景差异

- 写入操作用于临时配置或调试阶段的数据预加载(如测试模式设置)。

- 编程操作用于量产阶段的熔丝永久烧录(如修复冗余电路地址)。

IEEE标准关联性说明

根据IEEE 1149.1-2013 Clause 14.3.2的定义:

- 写入操作对应标准中的Write Operation Cycle

- 编程操作对应Program Operation Cycle

两者通过FBAccess信号的触发条件和programFB信号的电平组合实现区分(见Table 14-2 Operation Cycle Control Signals)。

这种区分机制使得BISR控制器既能实现快速寄存器配置(Write),又能确保熔丝编程的可靠性(Program),符合半导体制造中"先验证后烧录"的工艺要求。

| Function | Direction | Generic Fuse Box Port Name | Size | Description |

| FuseBoxClock | Input | clock | 1 | 该端口是fuse box的时钟信号。 该时钟由BISR controller生成,其来源既可能是TAP时钟(TCK),也可能是功能时钟(functional clock)。 当通过TAP启用BISR controller时,时钟由TCK派生并保持自由运行状态。 若进入功能上电模式(functional power-up mode),时钟则从功能时钟派生并启用。 在fuse box interface的selectFB输入信号下降沿之后的20个时钟周期后,该时钟将被禁用。 |

| FuseBoxAddress | Input | Address | n | 该端口用于指定对fuse box的读写地址。 无论fuse box采用何种组织结构,每个地址始终指向fuse box中的一个独立位。 该信号会在时钟上升沿(rising edge)时更新。 |

| FuseBoxWrite | Input | writeFB | 1 | 该端口在fuse box写入周期(write cycle)中使用。 该信号在整个fuse box interface写入周期期间始终维持高电平(high)。 信号状态会在时钟上升沿(rising edge)时更新。 |

| FuseBoxBufferTransfer | Input | programFB | 1 | 该端口为可选配置,仅在采用缓冲编程方法(buffered programming method)时存在。 信号在读取(Read)和写入(Write)操作期间保持低电平(low),在传输(Transfer)和烧录(Program)操作期间维持高电平(high)。 信号状态会在时钟上升沿(rising edge)时更新。 |

| FuseBoxSelect | Input | selectFB | 1 | 该选通端口(select port)在启用BISR控制器(内建自修复控制器)对fuse box执行读/写操作时被置为高电平(high)。 信号状态会在时钟上升沿(rising edge)时更新。 |

| FuseBoxAccess | Input | FBAccess | 1 | 当BISR控制器(内建自修复控制器)启动对fuse box接口的读/写操作时,该信号将维持一个完整的时钟周期(clock cycle)的高电平(high)。 信号状态会在时钟上升沿(rising edge)时更新。 |

| Programming VoltagePin | Input | vddq | 1 | 该引脚用于提供熔断熔丝(fuse)所需的高电压(high voltage)。 该引脚通常直接连接至芯片外部引脚(chip pin)以接收供电。 |

| TestMode | Input | TM | 1 | 测试模式端口(Test Mode Port, TM)用于在扫描测试期间隔离fuse box。 在扫描测试模式下,fuse box所有处于未知状态(unknown state)的输出都应通过TM信号进行门控(gated),以防止未知值(unknown values)传播至可扫描寄存器(scannable registers)。 |

| WriteDurationCounter | Input | strobeCntVal | 32 | 该总线输入端口(bus input port)在执行fuse box写入周期时由BISR controller驱动。 默认写入延迟时长(default write duration delay)由DftSpecification/AdvancedOptions/FuseBoxOptions/write_duration属性定义,并可通过PatternsSpecification/MemoryBisr/Controller/fuse_box_write_duration属性覆盖。 测试平台(testbench)根据时钟频率(clock speed)和指定的fuse_box_write_duration属性值计算初始写入时长计数器(write duration counter)的初值。 在选通计数器(strobe counter)归零前,fuse box需保持所有interface端口信号(如数据、控制信号)处于静态(无跳变)。 此端口为可选(optional)配置。若fuse box无需通过计数器控制写入时长,则相关属性(write_duration或fuse_box_write_duration)可省略。 |

| FuseBoxInterfaceReset | Input | FBreset | 1 | 该可选输入由 BISR controller 驱动,用于复位 fuse box interface 中的触发器。其有效值为 1,当 BISR controller 处于非激活状态或配置为 bisr_chain_access 模式时,该复位信号会 异步(相对于时钟)生效。 当 BISR controller 配置为 autonomous 或 fuse_box_access 运行模式时,复位信号会 同步 释放。此信号仅在以下情况存在: TCD FuseBoxInterface/Interface/reset 属性被指定,或 |

| FuseValue | Output | fuseValue | 1 | 该端口为 fuse box 的 1 位输出值,其输出值(fuse value)对应于 Address 端口指定地址所存储的 fuse box 数据。 当 fuse_box_location 设为 external 时,fuseValue 信号在 BISR clock 的 下降沿 采样。 |

| FuseBoxDone | Output | doneFB | 1 | 该端口用于向 BISR controller 指示 fuse box 的访问(写入或读取)操作已完成。 当 fuse_box_location 设为 external 时,FuseBoxDone 信号在 BISR clock 的 下降沿 采样。 当通过 TAP(fuse_box_access 模式)访问 fuse box 时,该信号不会被监测。 |

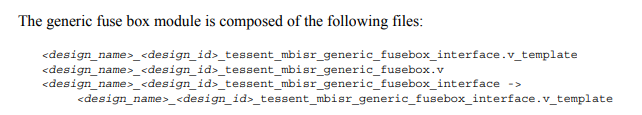

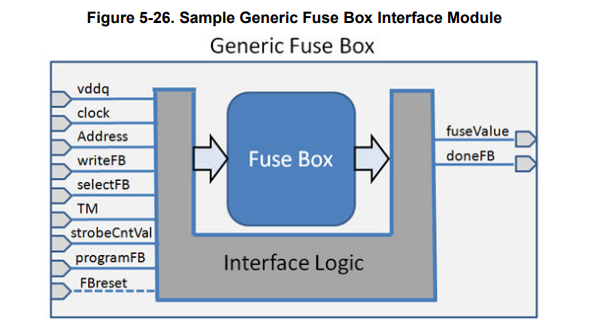

Generic Fuse Box Module

当 DftSpecification 中的 MemoryBisr/Controller/fuse_box_location 属性设置为 internal,且未在 tcd_fusebox wrapper 或 DftSpecification 的 fuse_box_interface_module 属性中指定 fuse box interface 时,系统会自动生成一个通用的 fuse box interface module。

该通用的 fuse box interface module 由 BISR controller 实例化,提供对 fuse box 的简单 interface 访问。该模块包含实际的 fuse box 存储体及其 interface 控制逻辑。

图 5-26 展示了通用的 fuse box interface module 的高层架构示意图。根据实际使用的 fuse box module 类型,某些输入端口可能不会被 interface 逻辑使用。该通用模块在 TSDB 中的存储路径为:

tsdb_outdir/instruments/<design_name>_<design_id>_mbisr.instrument/

该模板可作为编写自定义通用 fuse box interface module 的参考范例。此行为级仿真 interface 模型兼容以下两种编程模式:

buffered 模式

unbuffered 模式

(通过 AdvancedOptions/FuseBoxOptions/programming_method 配置)

列出的最后一个文件是指向该模板文件的符号链接。

请注意:若重新处理 DftSpecification,对该模板或符号链接(symbolic link)的任何自定义修改都将被覆盖并丢失。

重要说明:

此通用 fuse box 模板仅限用于评估或实验目的,严禁在实际设计中使用。

关键限制:

通用 fuse box 仿真模型 不会 对 fuse 写入/读取的时序要求执行任何验证

缺乏生产级设计必需的时序检查和可靠性保障机制

BISR 控制器以逐位(bit-by-bit)方式读写 fuse box 数据,并默认所有未被编程的 fuse box 地址位存储逻辑 0。该控制器仅在需要写入逻辑 1 时才访问 fuse box,不会主动写入 0。若 fuse box 的输出位宽超过 1 bit,则通用 fuse box 接口必须包含多路选择(muxing)逻辑,以确保 BISR 控制器能独立寻址每一位。此逻辑属于接口逻辑(Interface Logic),位于 fuse box 右侧(参考 Figure 5-26),其设计必须确保在写入周期仅目标 bit 被修改,而其余位保持不变。

在写入周期中,地址端口(Address port)用于指定待写入逻辑 1 的 fuse box 位置,因此接口逻辑必须正确解码地址信号,确保仅目标 fuse 被写入,同时防止非目标位在写入过程中被意外修改。需注意的是,通用 fuse box 模型不会自动验证时序,实际设计需额外加入时序检查逻辑。对于多比特 fuse box,必须手动实现 bit-level 访问控制(如 MUX 或解码逻辑),以确保正确的读写操作。

Determining the Fuse Box Size

BISR controller 采用高效压缩算法来最小化存储修复信息所需的 fuse box 数量。以下公式可用于估算该数值。

如果实施了软修复方法,则不需要 fuse box。

由于 fuse box 通常采用固定尺寸规格,该计算公式可帮助您选择合适的容量。通过配置 Tessent Core Description (TCD) 中 FuseBoxInterface/number_of_fuses 属性,既可设定 fuse box 的总熔丝数量,亦可基于公式计算结果进行配置——后者适用于存储非内存修复信息的场景。默认配置下,熔丝数量设置为2的幂次方,幂指数由 TCD FuseBoxInterface/Interface/address 属性指定的地址端口数量决定。

系统提供两种计算方案:适用于单 BISR 链的简化公式,以及支持多链架构的通用公式。具体实施细节请参阅"单链场景"与"多链场景"章节说明。

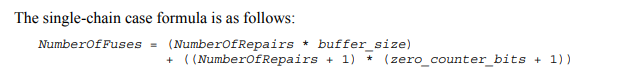

Single-Chain Case

NumberOfRepairs 表示芯片整体预期所需的最大修复次数,该数值通常介于3至10次之间。绝大多数需要修复的芯片仅需单次修复即可。若芯片需要10次或更多次修复,则很可能无法通过非存储器类测试(例如扫描测试),导致芯片不可修复并引发可靠性问题。

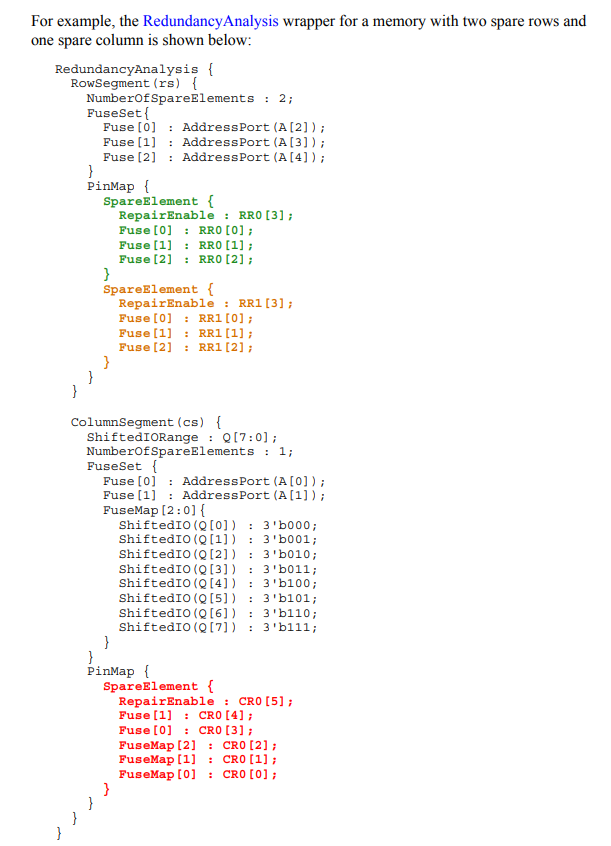

buffer_size 表示 BISR 寄存器中与单个备用行(spare row)或列(column)资源相关联的最大数据段。若存储器具有多个备用资源,则 BISR 寄存器将由所有备用资源的修复数据组成。为确定 buffer_size,需检查存储器 BISR 寄存器的每个数据段及其与各备用资源的对应关系。各备用资源对应的寄存器大小可通过存储器 TCD 文件中的 PinMap/SpareElement 封装信息获取。

在本示例中,存储器的 BISR 寄存器总长度为 14 位,用于存储所有 SpareElement 封装描述的修复数据:

4 位 用于存储第一个备用行(绿色高亮部分)的修复数据

4 位 用于存储第二个备用行(橙色高亮部分)的修复数据

6 位 用于存储备用列(红色高亮部分)的修复数据

由于 buffer_size 定义为 BISR 寄存器中与单个备用资源相关联的最大数据段,因此该存储器的 buffer_size 值为 6。

对于当前设计中的每个存储器,都需要重复上述分析流程,并最终在 NumberOfFuses 计算公式中采用所有存储器里最大的 buffer_size 值。

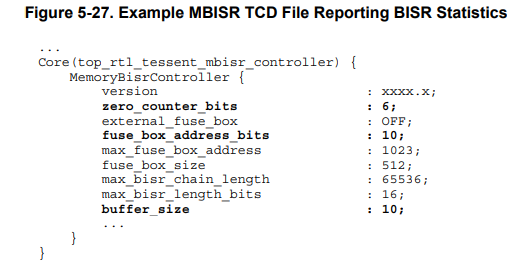

zero_counter_bits 表示在 BISR 链载入 BIRA 结果后,用于统计连续 0 串的计数器的位宽。默认情况下,该计数器位宽为 BISR 链长度的以 2 为底的对数值向上取整(即 log2(链长度) 的进位整数)。

buffer_size 和 zero_counter_bits 参数会自动从电路中提取,并在运行 process_dft_specification 后,记录在以下路径的 TCD 文件中:

TSDB/instrument/<design_name>_<design_id>_mbisr.instrument/<design_name>_<design_id>_mbisr_controller.tcd

如需计算熔丝(fuses)数量,可先运行一次 process_dft_specification,然后在生成的 TCD 文件中查找这些参数值。注意:可能需要预先运行 process_dft_specification 以生成默认的 BISR 链顺序(如 “Controlling the BISR Chain Order” 章节所述)。

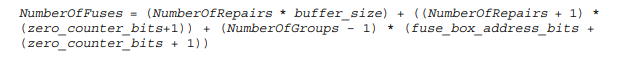

Multi-Chain Case

多链场景的计算公式包含与单链场景完全相同的首项,同时增加了因额外链存在而产生的开销;每条链均关联一个群组。其公式如下:

NumberOfGroups 表示电路中群组的数量。群组通常与电源域相关联,也可用于划分同一电源域内具有不同修复优先级的内存单元。

fuse_box_address_bits — 表示访问 fuse box 所需的地址位宽。

若 fuse box 仅用于存储内存修复信息,其地址位宽即为 fuse box 中熔丝数量的以2为底的对数(log2),该值会如图5-27所示记录在MBISR TCD文件中,并在“单链场景”章节中说明。

但若 fuse box 需共享用于其他用途,则地址位宽会更大。

多链场景下,zero_counter_bits 的值由最长的 BISR 链决定。

各条链的长度以及群组数量会记录在 MBISR TCD 文件中(如图 5-27 所示),并在“单链场景”章节中说明。

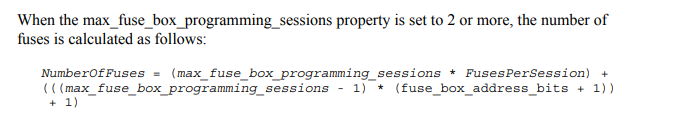

Incremental Repair Case

硬增量修复(Hard incremental repair) 是指在多个测试阶段(如晶圆测试、封装测试、最终测试甚至系统测试)中分步对 fuse box 进行编程。

要实现多阶段编程,需在 DftSpecification/MemoryBisr/Controller 封装中指定 max_fuse_box_programming_sessions 属性,其值需大于默认值 1,或直接选择 “unlimited”(无限制)选项。

当 max_fuse_box_programming_sessions 设为 “unlimited” 时,fuse box 压缩功能会被关闭,此时 BISR 链的修复数据将以未压缩形式直接存入 fuse box,后续写入的修复数据不会覆盖之前测试阶段存储的结果,从而支持无限次的 self_fuse_box_program 自主编程操作。这种情况下,所需的 fuse 数量必须至少等于 BISR 链的总位数。禁用压缩功能在极少数情况下尤其有用,例如预计超过 50% 的修复寄存器会被使用时,压缩算法会变得低效,甚至可能导致所需的 fuse 数量超过 BISR 链的位数。

**FusesPerSession** 表示根据“单链情况”与“多链情况”章节所述方法计算出的单次编程会话所需的 **fuse** 数量。该计算公式稍显保守,因其假设首次编程会话中几乎需执行全部修复操作,且所有编程会话均被使用。然而,实际所需的 **fuse** 数量可能因修复操作的统计分布而大幅减少。反之,若编程会话使用次数较少,则基于该计算值可完成的修复总量可能显著高于预期。

例如,假设在计算单条 BISR 链的 FusesPerSession 时,将 NumberOfRepairs 设为 10,计算结果为 250 个 fuse。同时,假设 max_fuse_box_programming_sessions 设为 2,因此在增量修复情况下,NumberOfFuses 总数为 512。这一 fuse 数量支持在以下两种情况下进行修复:若两个编程会话均被使用,且大部分修复在首次编程会话中完成,则可执行最多 10 次修复;

若所有修复均在单一编程会话中完成,则该 fuse 数量可支持最多 20 次修复。

**fuse_box_address_bits** — 表示访问 **fuse box** 所需的地址位宽。 - **若 fuse box 仅用于存储存储器修复信息**,则地址位宽为 **fuse box 中 fuse 数量的以 2 为底的对数**(即 `log2(NumberOfFuses)`),该值会在 MBISR TCD 文件中报告(如图 5-27 所示),并在“单链情况”部分进行说明。 - **若 fuse box 被共享用于其他用途**(如存储额外的配置数据),则所需的地址位宽会更大(需覆盖所有用途的寻址需求)。

例如:

- 如果 **fuse box** 包含 512 个 **fuse**,且仅用于修复,则 `fuse_box_address_bits = log2(512) = 9`。

- 如果 **fuse box** 还包含其他非修复数据,则可能需要额外地址位,如 10 位或更多,具体取决于共享存储的总容量。

Creating and Inserting the BISR Controller

Understanding the BISR Controller

BISR controller硬件在芯片顶层自动生成,该硬件实现了多项功能,可用于执行以下操作:压缩修复信息并将结果写入fuse box;对fuse box内容进行解压缩并将其移入芯片BISR链;通过TAP接口初始化或观察BISR链内容;以及通过TAP接口读取和编程熔丝。

BISR controller通过TAP接口进行访问,其控制端口已自动连接至BISR控制器,同时该控制器也与fuse box相连。BISR controller通过TAP接口为外部提供访问BISR链和fuse box的通道,并支持自主运行模式(Autonomous run mode),在此模式下仍可访问BISR链与fuse box,从而处理芯片内部所有修复信息。

芯片上电时,BISR链的内容处于未知状态。由于BISR链直接驱动存储器修复端口,在使用芯片前必须清除其内容或写入修复信息。当保持BISR controller的功能修复使能输入引脚为激活状态时,BISR链将执行异步复位。为BISR链注入修复信息的初始化方法主要有两种:

• Apply a low-to-high transition on the BISR controller functional repair enable input pin

当发生状态转换时,BISR controller会从fuse box中加载修复信息至BISR链。通常该方法用于BISR controller修复使能端口与上电复位信号绑定的系统。 若存在多电源域组,BISR controller会配备名为PowerDomainGroupEnable_<pdg_label>的输入端口,每个端口对应一个电源域组。这些输入端口用于在启用BISR controller时选择需要初始化的BISR段。通过此类端口,系统可从选定的电源域单独上电启动BISR链,同时保留其他电源域中的修复信息。

• Initialize through the TAP using the Autonomous run mode

其中一项自主操作是 power_up_emulation,它模拟功能性上电复位。通常,此方法用于制造阶段,此时仅能通过 TAP 访问芯片。

BISR controller 提供多种方式对 fuse box 进行编程。既可通过 TAP 接口进行外部编程,也可采用自主 self-fuse box 编程模式,利用 BISR 链中的修复信息内容进行内部编程。

BISR Controller Run Modes

BISR controller 有三种运行模式:

• autonomous

在此模式下,控制器操作无需测试机台提供任何数据模式。修复信息及压缩/解压缩操作均在芯片内部完成。可执行七种自主操作:

- self_fuse_box_program(自主熔丝盒编程)

- power_up_emulation(上电复位仿真)

- verify_fuse_box(熔丝盒校验)

- rotate_bisr_chain(BISR链轮转)

- calculate_bisr_chain_length(BISR链长度计算)

- load_bisr_chain(BISR链加载)

- clear_bisr_chain(BISR链清零)

• bisr_chain_access

在此模式下,芯片级BISR链通过TAP接口的TDI和TDO端口进行访问。该模式下支持的有效操作包括:

- enable_rotation(启用轮转模式,当不存在BISR控制器时)

- enable_bira_capture(启用BIRA捕获功能)

- select_bisr_registers(选择BISR寄存器组)

• fuse_box_access

在此模式下,可通过TAP经由BISR controller访问fuse box。该模式下仅支持编程和读取两种有效操作:编程操作允许通过TAP向单个熔丝地址写入数据,读取操作则可通过TAP从单个熔丝地址读取数据。无论fuse box的实际结构如何,其寻址方式始终以单比特为单位进行。

多家供应商提供的fuse box具有大量互不兼容的interface和通信协议。鉴于这种复杂性,针对fuse box的读写协议被封装在专用interface中——这些interface需为每个fuse box单独定制。不过对于特定工艺技术而言,这种定制仅需完成一次。此外,Siemens EDA可为部分工艺技术提供现成的interface,或在特定条件下开发新的interface。

fuse box既可以实例化在BISR controller内部,也可以作为外部组件独立于BISR controller存在。

当fuse box位于BISR controller内部时,系统会使用一个通用fuse box模型来包含封装了特定读写协议的fuse box。该通用fuse box模型以模板文件的形式生成,使用时必须实例化fuse box,并在此模块内实现具体的读写协议。

当fuse box位于BISR controller外部时,设计中必须实例化一个fuse box interface,以便为BISR controller提供有效的读写接口。通常,当fuse box需要用于内存修复以外的其他用途时,会采用外部fuse box方案。

Connecting the BISR Controller to an External Fuse Box

BISR controller支持外接fuse box方案。通常在以下两种场景会采用外部fuse box:一是当fuse box需要支持多项功能共享,且通过TAP接口访问的方式不适用于读写与内存修复无关的功能时;二是当fuse box具备BISR controller不支持的特定功能时。

当使用外部fuse box时,必须将MemoryBisr/Controller封装中的fuse_box_location属性设置为external。同一封装内的fuse_box_interface_module属性可用于指定外部fuse box的库模块。若未指定此属性,则库模块将从ExternalFuseBoxOptions封装的design_instance属性所指定的设计实例中推断。若这些属性均未指定且设计中仅存在单个tcd_fusebox文件,则fuse box模块将从该tcd_fusebox描述中自动推断。

外部fuse box的设计实例必须已在设计中实例化。通常,fuse box会被实例化在一个同时包含interface逻辑的模块内。若外部fuse box仅用于存储器修复,则该模块的所有输入端口应置为固定值,输出端口保持悬空。运行process_dft_specification命令时,所有输入端口会先断开,再连接至BISR controller模块。若外部fuse box还需用于功能用途,则interface逻辑的输入输出端口应已与功能逻辑相连。此时,process_dft_specification命令会对输入端口进行多路复用,并利用现有输出端口连接实现fuse box的接入。

外部fuse box的核心描述可在模块匹配时自动读取。关于指定搜索路径的说明,请参阅set_design_sources -format tcd_fusebox命令描述;显式读取核心描述的方法请参考read_core_descriptions命令;名称匹配流程的详细信息可查看set_module_matching_options命令文档。

若实例化模块的核心描述包含FuseBoxInterface封装,则BISR controller与fuse box interface之间的连接将自动完成。若核心描述不可用或不完整,可在MemoryBisr/Controller/ExternalFuseBoxOptions/ConnectionOverrides封装中手动建立连接。需注意,在DftSpecification的ConnectionOverrides封装内完成显式连接时,必须指定以下属性:

• done

• read_data

• write_en

• select

• access_en

• address

• write_duration_count

不得在**tcd_fusebox**中省略上述任一端口,并仅通过**ConnectionOverrides**封装补充单个缺失端口。Siemens EDA建议**fuse box** **interface**的核心描述应尽可能完整。核心描述**interface**封装中定义的所有端口必须存在于实际设计模块实例中。只要在运行**process_dft_specification**命令前于**ConnectionOverrides**封装中明确声明,设计模块实例允许存在库模块**Interface**封装未描述的额外端口。

Connecting a BISR Controller to System Logic

通常,系统逻辑会连接到 **BISR controller**,以启动存储器修复并监控操作进度。所有连接均在 **DftSpecification** 配置文件中的 **MemoryBisr/Controller** 封装内指定。系统逻辑至少需要提供三个输入连接,以便在电源启动时触发存储器修复:

- **BISR controller** 的输入 **clk** 必须由适当的功能时钟驱动。该连接通过设置 **repair_clock_connection** 属性完成。

- **BISR controller** 的输入 **resetN** 用于复位 **BISR chain(s)** 并启动存储器修复。该连接通过设置 **repair_trigger_connection** 属性完成。

- **BISR controller** 的 **repair mode** 输入指定了当检测到 **resetN** 上升沿时,控制器启动的自主运行模式。该三位修复模式连接通过设置 **repair_mode_connection** 属性完成。关于此输入的运行模式编码及详细信息,请参阅相关属性说明。

**注意**:

- 若 **resetN** 在控制器运行后保持高电平,则所有 **BISR chain** 将保持其值不变。

- 若 **resetN** 为低电平,且所选运行模式为 **Functional Power-Up** 或 **BISR Chain Length Calculation**,则 **BISR chain** 会被清空。

- 若存在多个电源域组,则仅被启用的 **BISR chain** 会被清空。

如果设计包含多个电源域组,则还需在 MemoryBisr:Controller 封装内部建立以下连接:

BISR controller输出可连接至系统逻辑,用于监控上电操作进度。这些连接为可选但建议配置,以确保在首次访问存储器之前,fuse box的存储器修复信息已成功传输至所有存储器。

BISR controller 输出信号 BisrGo 的值为 1 时,表示 BISR 操作成功。BisrGo 的状态仅在 BisrDone 也为 1 时有效。该连接通过配置 AdvancedOptions:bisr_pass_connection 属性实现。

BISR controller 输出信号 BisrDone 的值为 1 时,表示自主运行模式(如上电操作)已完成。该连接通过配置 AdvancedOptions:bisr_done_connection 属性实现。

当设计包含多个电源域时,需要额外连接。至少必须为每个与电源域关联的BISR控制器输入指定PowerDomainOptions:PowerDomainName:enable_from_pmu_connection属性。该输入决定了在下一次功能输入(带有repair_trigger_connection属性)的低到高转换时,是否将修复信息加载到电源域中。

还可通过其他属性来监控专用于每个组的BISR控制器输出监视器,包括PowerDomainOptions:PowerDomainName:busy_to_pmu_connection属性和PowerDomainOptions:PowerDomainName:done_to_pmu_connection属性。当对应电源域组的修复信息正在加载到BISR链中时,“busy”输出为高电平;而一旦对应电源域的修复信息成功加载到BISR链中,“done”输出将变为高电平。必须监控全局BisrGo输出以确认操作成功。

所有与控制器输入关联的属性均不可重复,而与控制器输出关联的属性均可重复,以便将同一输出连接至多个目标。

Choosing a Functional Repair Clock

用于自修复的分布式架构和保守时钟方案要求谨慎选择芯片上电时执行修复的功能性修复时钟。建议在该功能模式下采用50 MHz或更低频率的功能时钟。需注意,其他用于生产测试的模式均采用默认10 MHz的TAP时钟(TCK),这种低频设计能简化时序收敛。对于5000比特的BISR链,10 MHz时钟下自修复耗时约1毫秒,可修复数百个存储器。若需缩短修复时间,可采用更高频的功能时钟,但决策时必须考虑以下可能限制最大可实现频率的因素:

• **BISR链的时钟平衡问题**:BISR链分布在芯片各处,部分链段可能属于预设计的电路模块。为提升运行速度而对BISR时钟进行平衡可能较为困难。 • **时钟边沿不确定性**:虽然BISR寄存器间插入了重定时寄存器以避免时钟平衡需求,但这些寄存器可能限制最大可实现频率——原因是BISR时钟下降沿相对上升沿的触发时间存在不确定性。 • **BISR寄存器的分布特性**:由于BISR链贯穿整个芯片且部分链段可能集成在预制模块中,寄存器间的长走线会制约最高频率。可通过两种机制缓解时序问题:

o Pipeline Registers

• **插入流水线寄存器**:对于使用 **BisrElement** 封装的存储器实例,可在每个 BISR 寄存器前后插入流水线寄存器,并独立配置其时钟沿(上升沿或下降沿)。 • **灵活插入多级流水线**:在 **BisrSegmentOrderSpecification** 封装中通过 **`:pipeline`** 声明,可在各电源域的 BISR 链中任意位置插入多个流水线寄存器,以优化时序。

Placement-Based BISR Chain Routing

当使用 BisrSegmentOrderSpecification 封装并提供指定存储器坐标的 DEF 文件时,MemoryBIST 会根据布局优化 BISR 链的布线。您需要在运行 check_design_rules 命令前通过 read_def 命令加载 DEF 文件。如果不提供 DEF 文件,则可以手动指定 BISR 链顺序以最小化 BISR 连接长度并按电源域分组。

您还可以通过 BisrElement 和 BisrElement/Pipeline 封装独立覆盖 BISR 寄存器及相关流水线寄存器的布局,并将其插入特定的父设计实例中。此时 BISR 链的顺序将基于 DEF 文件中父设计 BISR_SI 引脚的布局信息确定。

Inserting Multiple BISR Controllers and Fuse Boxes

在某些设计场景中,您可能需要配置多个BISR控制器和fuse box。Tessent MemoryBIST并不限制设计中BISR控制器与fuse box配对的数量,但需注意eFuse制造商提出的约束条件及其在设计中布局位置对设计流程自动化的影响。 当fuse box的物理尺寸无法满足设计需求时,就需要配置多个BISR控制器。影响fuse数量的因素包括最大修复次数、BISR链数量、编程会话次数以及非内存修复用途的fuse占用等(详见"Determining the Fuse Box Size")。

此外,eFuse宏的时序要求使得单个控制器难以设计出支持多eFuse宏实例信号交互的fuse box interface。若BISR控制器的compression algorithm还需支持多eFuse宏实例,fuse box interface的复杂度会进一步增加(参考"Compression Algorithm and Fuse Box Organization"了解组织架构)。

另一种需要多控制器的情形是当某条BISR链的加载时间过长时。仅靠提高repair clock频率或为问题链分配更高优先级可能无法解决。此时可通过MemoryBisr DftSpecification中的PowerDomainOptions/power_domain_priority属性调整各BISR链电源域的编程顺序。

虽然Tessent MemoryBIST允许设计中使用任意数量的BISR控制器与fuse box配对(且各控制器在pattern generation阶段可独立控制),但制造商对多eFuse实例应用有特殊设计规则。例如可能规定芯片fuse总数上限,或限制仅允许一个eFuse宏处于编程模式。您必须仔细查阅所选eFuse宏的数据手册以掌握所有限制条件。

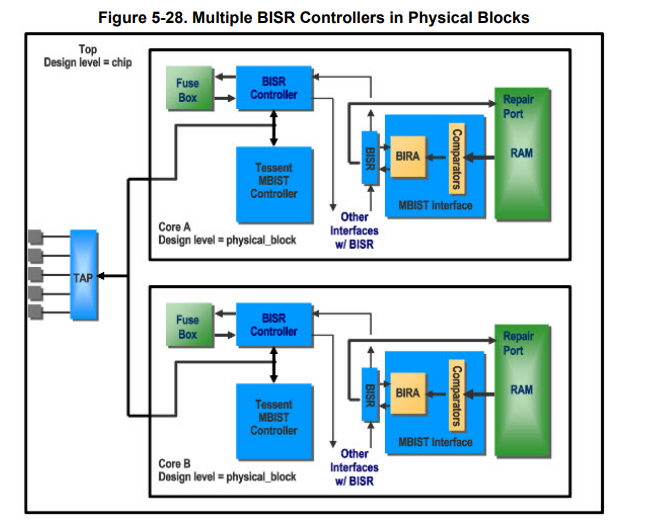

BISR Controllers in Physical Blocks

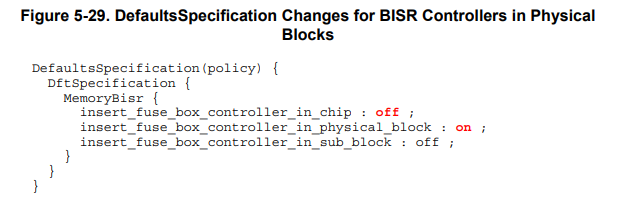

下图展示了在设计中插入多个BISR controller和fuse box配对的最简单方法——将每组配对分别插入独立的物理模块(physical block)中。

该方法实现的自动化设计流程与前述"创建并插入BISR controller"章节中描述的硬件插入流程几乎完全相同,唯一需要在实施常规设计流程前完成的操作是对MemoryBisr DefaultsSpecification中标红部分进行必要修改。这种配置方式确保了每个BISR controller都能与其对应的fuse box正确配对,同时通过标准interface与tester保持通信,而无需对整个测试架构进行额外调整。

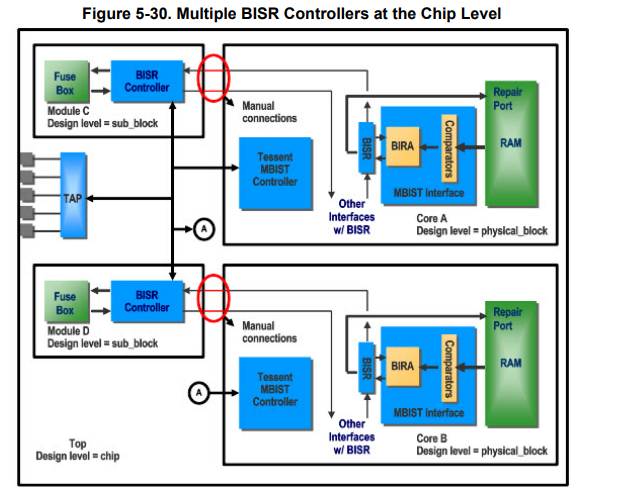

BISR Controllers at the Chip Level

根据物理设计规则的要求,可能需要将eFuse宏单元放置在芯片顶层。若需在顶层布局多个BISR controller与fuse box配对模块,将面临设计流程复杂度提升且无法完全自动化的问题。此时可采用以下设计流程:首先将多组BISR controller和fuse box配对部署在子模块中,再通过整合操作将这些子模块合并至芯片顶层,具体实施方式如下例所示

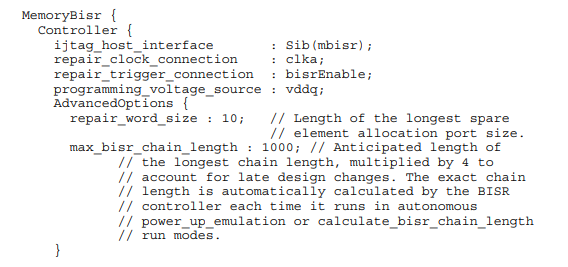

创建模块C和D的子模块步骤如下:a. 在每个子模块中实例化fuse box interface,如果FuseBoxInterface的tcd_fusebox库文件被读入设计,则BISR controller与fuse box之间的连接会自动建立;b. 在每个子模块中插入BISR controller,参考后续的DftSpecification示例。

此时Tessent Shell尚未识别BISR链,因此您必须手动配置BISR controller的AdvancedOptions封装中列出的以下属性。

预计最长链长度的4倍(用于应对后期设计变更)。实际链长度将由BISR controller在每次以自主power_up_emulation或calculate_bisr_chain_length运行模式时自动计算。

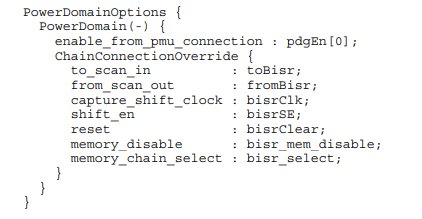

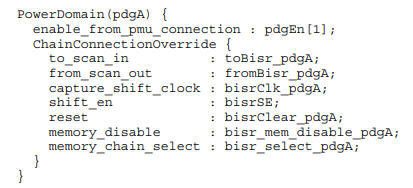

请指定工具在当前子模块设计中创建的主输入/输出端口名称。这些端口名称应在 BISR controller 的 PowerDomainOptions 封装内的 ChainConnectionOverride 封装中进行配置。您将在本流程的 步骤3 中手动将这些端口连接至父级(顶层)设计中的物理模块 BISR chain 引脚。

对于具有多链或多电源域的控制器(controller),您需要为每个电源域(power domain)指定一个额外的PowerDomain(power_domain_name)封装器,如示例中针对电源域(power domain)“pdgA”所示。

2、使用常规设计流程创建 Core A 和 Core B 的物理模块(physical blocks):

a. Insert MemoryBIST as described in “Planning and Inserting MemoryBIST”.

b. Insert the BISR chains as described in “Inserting BISR Chains in a Block”

3. Create the chip-level design:

a. Instantiate all physical blocks and sub-blocks.

b. Create manual connections between the sub-blocks and physical blocks.

You should use a process_dft_specification.post_insertion proc to create these connections. This proc will need to do the following:

i. 识别子模块中必须由BISR controller控制的带有BISR链的物理块。 • 若存在多个物理块: • 将这些物理块的BISR scan_in与scan_out端口连接以形成单一BISR链。 • 将该单一链连接至子模块的BISR to_scan_in与from_scan_out端口。

若存在多个BISR电源域,需为每个电源域创建一条独立的BISR链,并将其分别连接至对应子模块的BISR to_scan_in与from_scan_out端口。

• 子模块的BISR shift_en、capture_shift_clock和reset端口为所有物理块的BISR interface端口共用。

• 对于包含串行修复接口存储器的物理块,需将子模块的memory_disable与memory_chain_select端口连接至对应物理块。

ii. 对每个子模块重复步骤i中描述的流程。子模块的to_scan_in、from_scan_out、shift_en、capture_shift_clock、reset、memory_disable和memory_chain_select端口均在DftSpecification中定义,如步骤1b中针对单个电源域的示例所示。图5-30中用红圈标注的连接展示了此示例实现所需的手动连接。您无需干预并手动连接IJTAG网络,因为这些连接已通过process_dft_specification命令正确配置。

2108

2108

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?