Modelsim独立仿真带有vivado IP核的文件

用modelsim独立仿真带有vivado IP核的文件一共需要三个大步骤:

1.导出vivado ip核库

①在vivado中导出IP核的仿真库

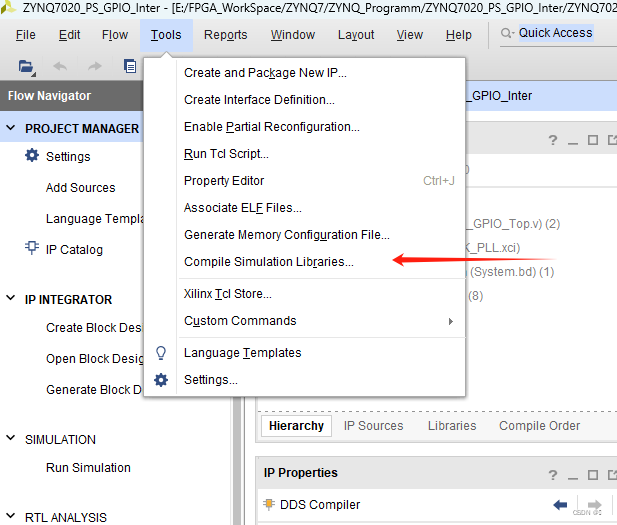

第一步首先要在vivado中导出IP核的仿真库,我使用的是vivado 2018.3。打开vivado2018.3,在工具栏找到Tool,列表中有一个Compile Simulation Libraries。

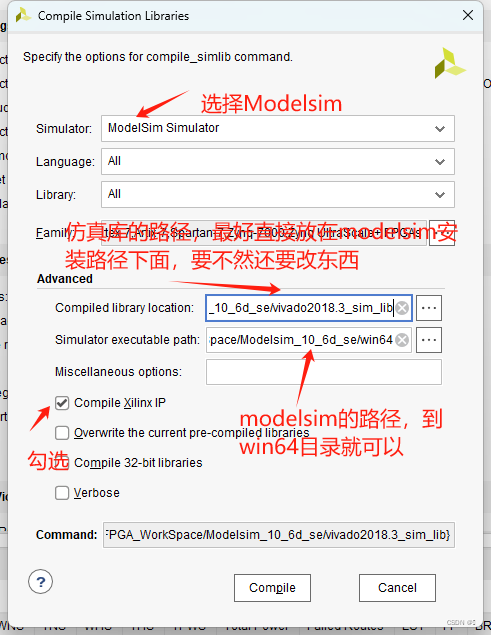

②设置导出路径

注意:仿真库导出路径Compiled library location最好放在modelsim安装路径下面,要不然导入到modelsim的时候要改很多库的路径!设置好后点击Compile,等待生成,可能要花费30分钟左右。导出完成后,可以在Tcl Console中查看生成信息。

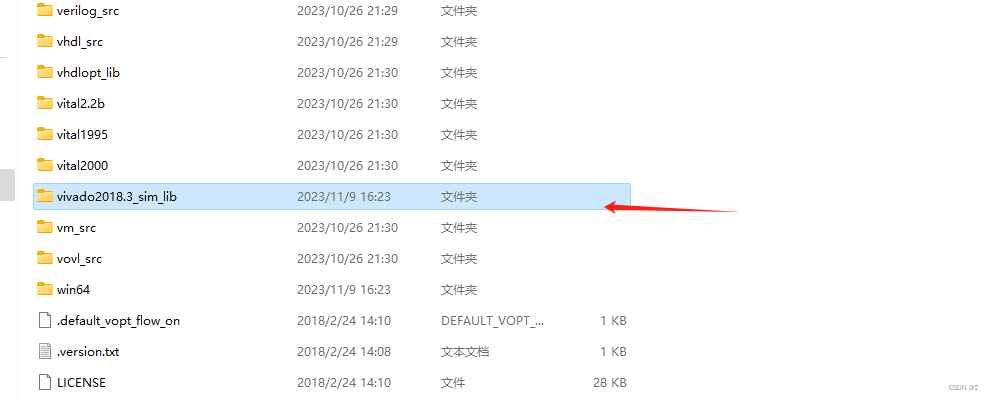

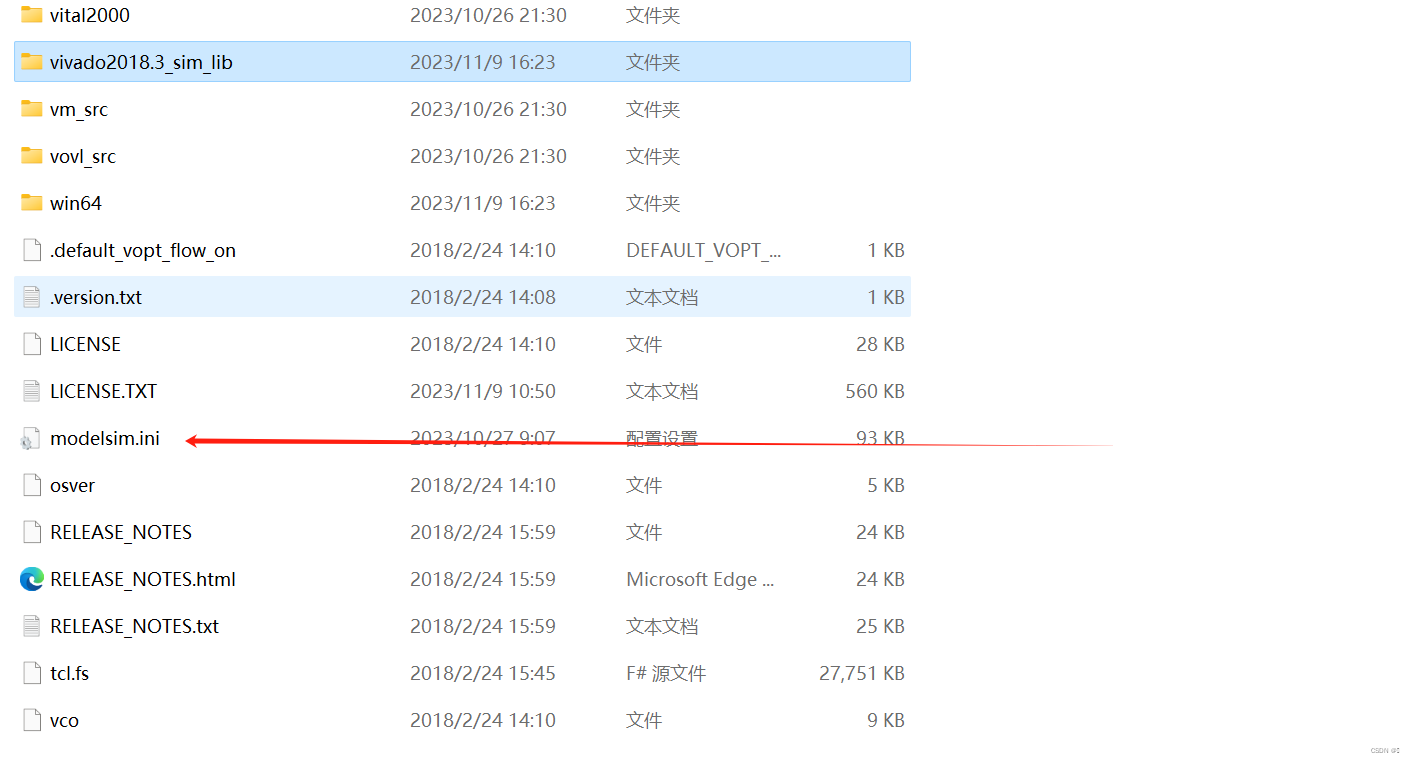

打开生成的目录,可以看到生成的vivado仿真库文件夹。

2.把viado仿真库添加进Modesim中

①vivado仿真库路径

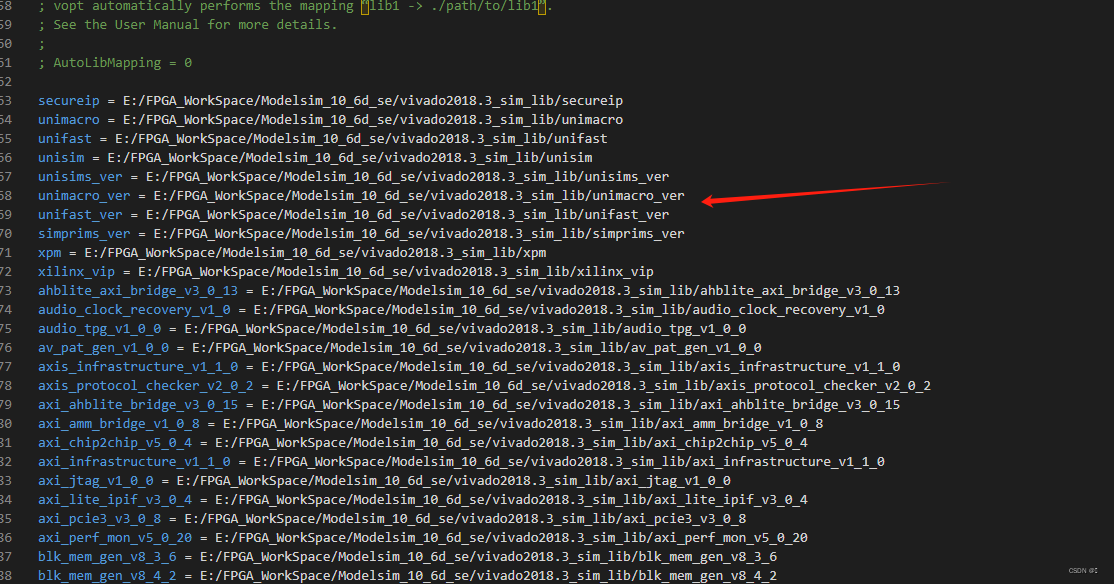

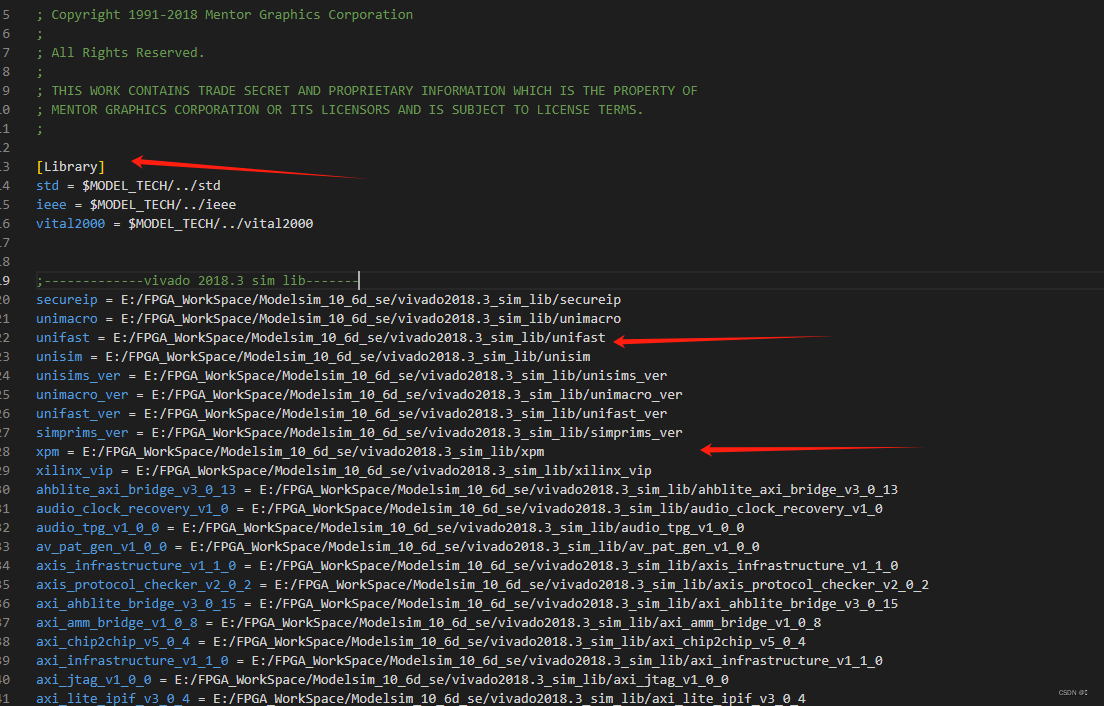

找到刚才生成好的vivado仿真库文件,在文件夹里面打开找到里面有一个modelsim.ini文件(这个.ini文件是vivado生成库里的,不是modelsim的),用记事本或者vscode打开,打开后我们可以发现各个库的路径,复制所有库的路径。

②把仿真库的路径加入到modelsim中

②把仿真库的路径加入到modelsim中

在①中复制好所有库的路径好,在modelsim安装路径下找到modelsim的.ini文件,改变只读属性。

在 [Library]下边把复制好的路径,复制进来。

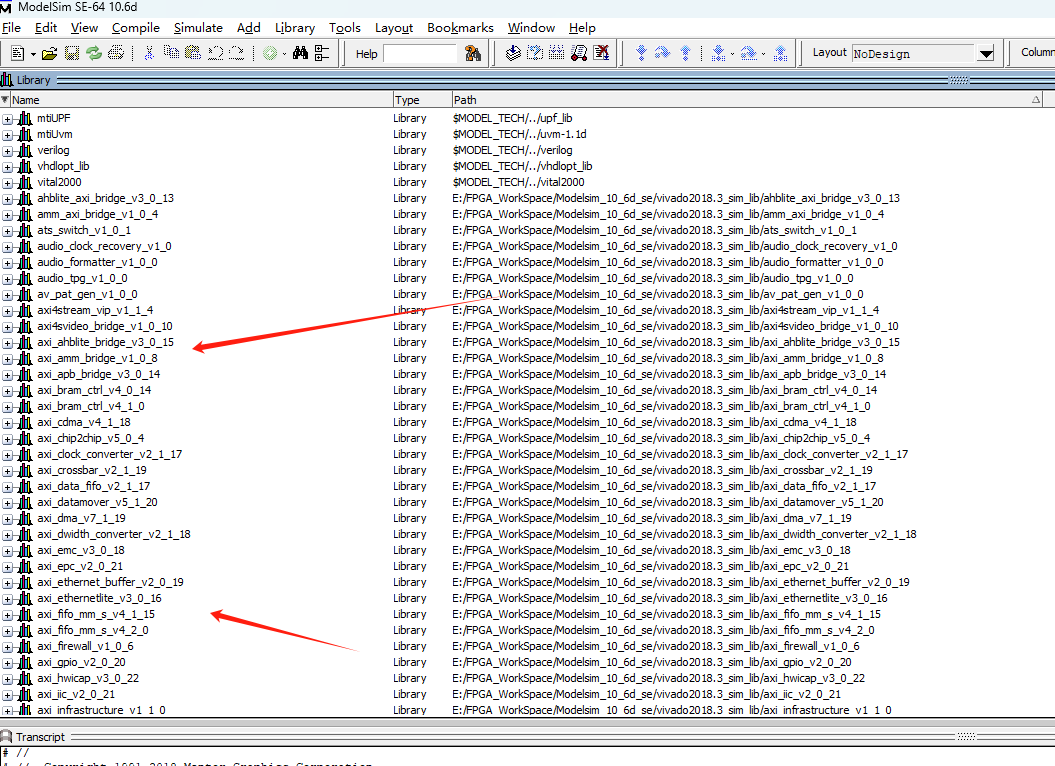

保存好后,打开Modelsim查看库是不是添加进来了。

3.搭建仿真系统

这面两步完成后,开始搭建系统文件。相比于以前,写好testbench文件后,还要做一件事情,就是把使用到的IP核的verilog代码也要加进来。

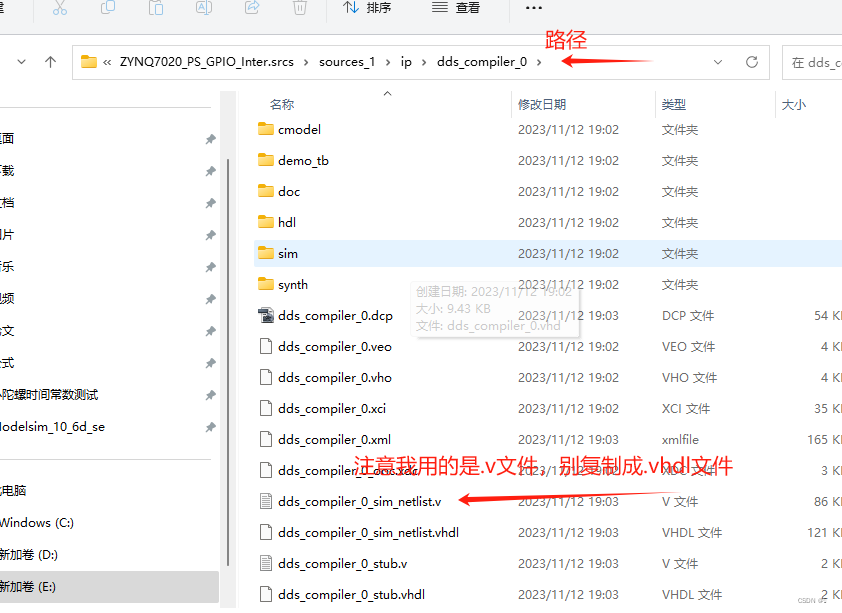

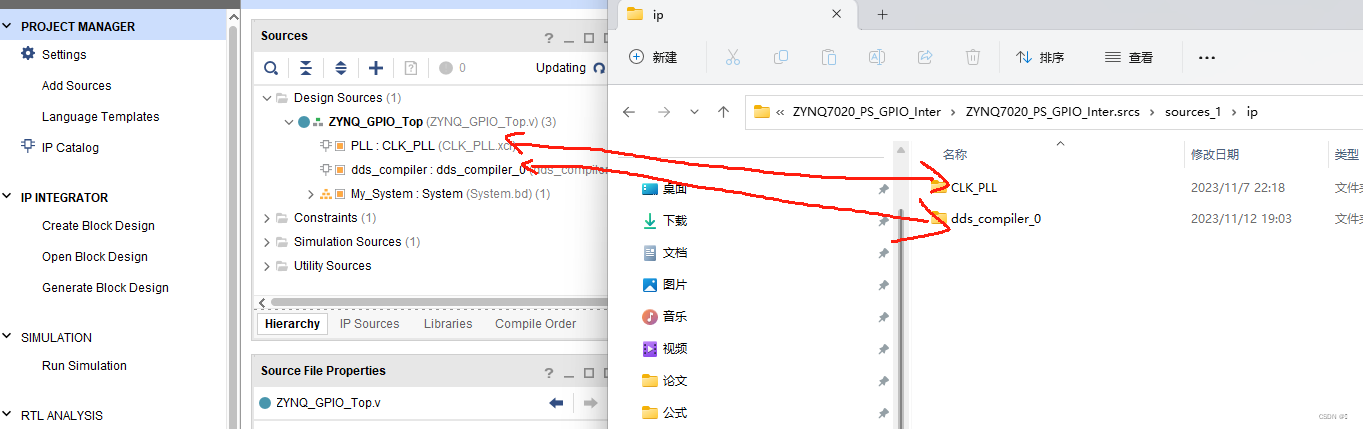

①找到所有的IP的xxx_sim_netlist.v文件

比如我们用到了一个DDS IP核和PLL IP核,我们在我们的工程里依次到以下目录中:

xxx.srcs/sources_1/ip/dds_compiler_0/dds_compiler_0_sim_netlist.v

xxx.srcs/sources_1/ip/CLK_PLL/CLK_PLL_sim_netlist.v(PLL IP 在我工程里我起的名字叫CLK_PLL)

会发现你用到了几个IP核这里就会有几个IP核。

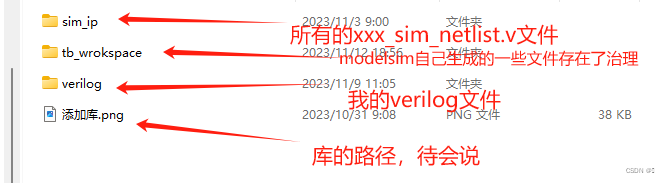

②建立仿真文件

找到所有的xxx_sim_netlist.v文件后,我的文件构成是这样的

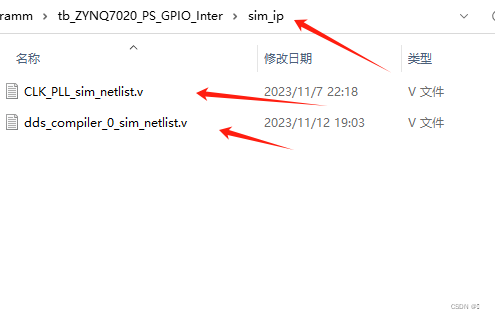

在sim_ip文件夹中,我们把在①中找到的xxx_sim_netlist.v复制进来。

在tb_workspace中存放modelsim工程

在verilog中存放我们要仿真的代码

③在Modelsim中加入仿真库文件

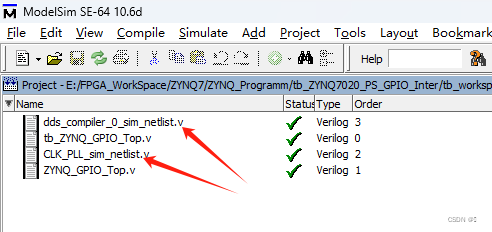

把我们自己写的tsetbench代码 以及 xxx_sim_netlist.v全部加入到Modelsim工程中

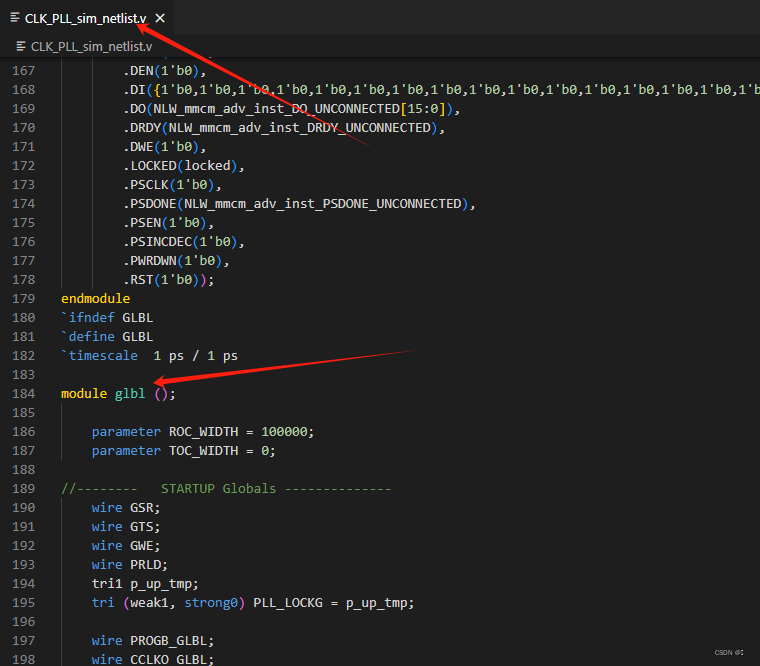

注意: xxx_sim_netlist.v仿真时间改成你头文件的`timescale

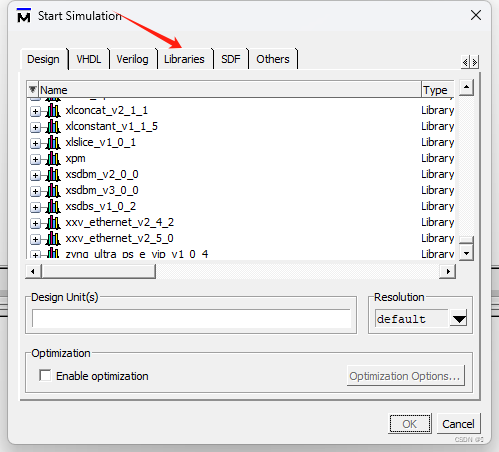

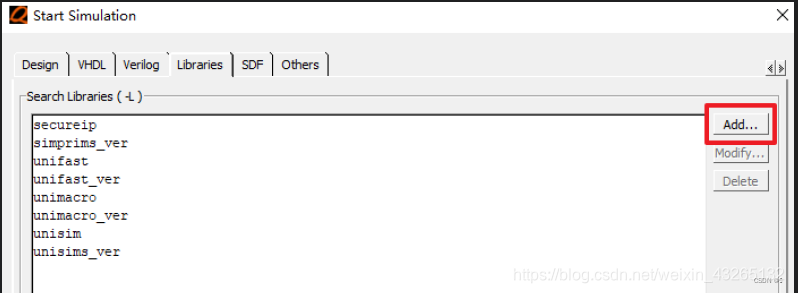

点击仿真后,点击Librasries

在你生成的vivado仿真库中文件夹下,把以下库添加进去一共8个(这个就是①中.PNG库路径,每次新的工程要重新加入一遍)。

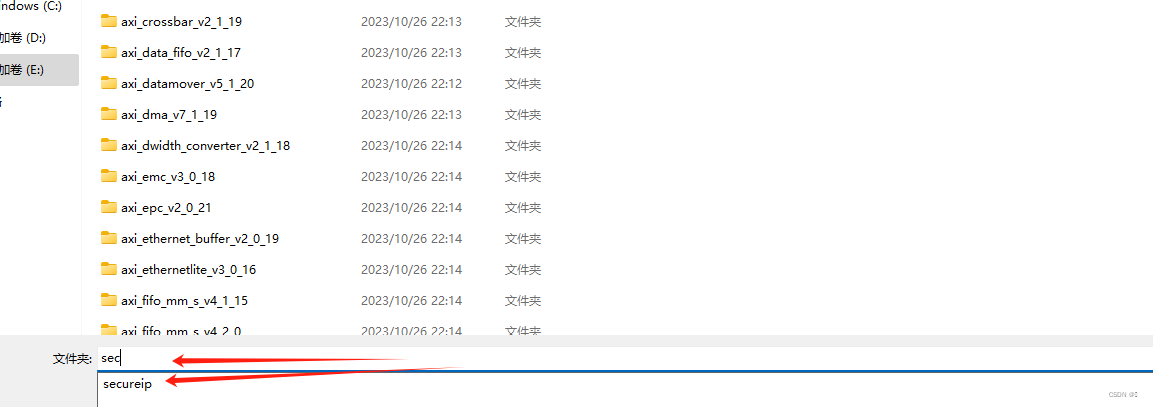

有一个小技巧,在搜索库的时候,直接在下面打字就能出来上。

添加完之后你会发现你的work里面不只有你的文件还有一些其他文件,找到你的最顶层文件,做完这些就可以进行仿真了

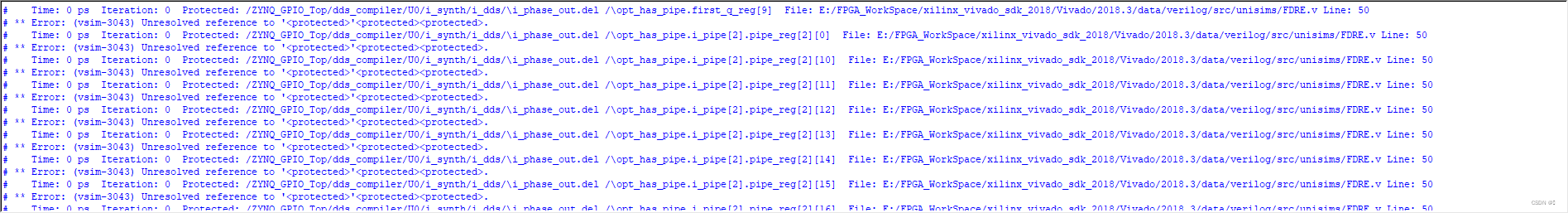

④特别注意!!!!

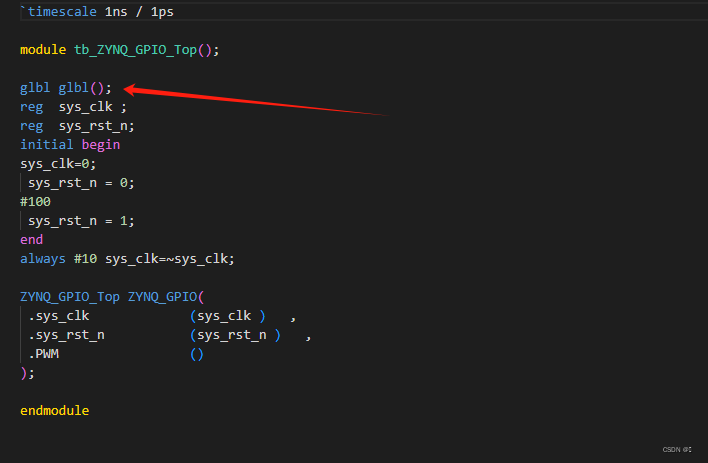

第一点 : 如果你用到了PLL会报错,这是因为PLL IP核对复位信号的时间有一定的要求,因此,你需要在你仿真顶层文件里面把glbl 例化一下。

这个glbl在哪里的,就在你PLL 的_sim_netlist.v中,所以可以直接在你仿真顶层文件里例化glbl!!

所以可以直接在你仿真顶层文件里例化glbl!!

第二点 如果你用了 PS端 你需要暂时把PS端注释掉,因为modelsim仿真不了PS端

本文详细介绍了如何在Modelsim中独立仿真带有VivadoIP核的文件,包括导出VivadoIP核仿真库、添加至Modelsim、配置timescale和处理PLL与PS端的问题。

本文详细介绍了如何在Modelsim中独立仿真带有VivadoIP核的文件,包括导出VivadoIP核仿真库、添加至Modelsim、配置timescale和处理PLL与PS端的问题。

649

649

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?