verilog介绍

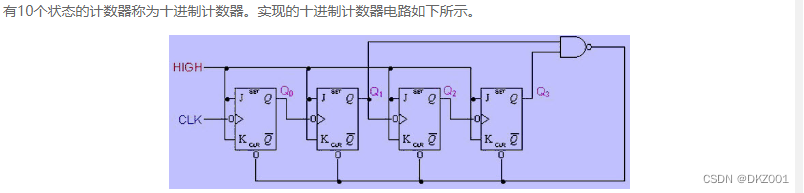

Verilog HDL 是一种硬件描述语言,HDL是 hardware description language发缩写。可以用于数字电子下系统的设计。通俗点说就是在设计数字芯片或着使用cpld 或者fpga的时候用到,比如在设计电路的时候,如果要试一下一个计数功能,不适用硬件描述语言,就需要自己亲自选择元器件进行设计,如下图所示:

但是当你选择使用verilog的时候可以通过下面的语言实现,通过用编程语言更加直观的表现运行的逻辑,并且可以尽量分离硬件和算法,减小工作的复杂度。

module Count_1

(

input clk ,

input rst_n ,

output reg [ 3:0] cnt

);

reg [ 3:0] cnt_n ;

always @(*)begin

if(cnt == 4'd9)

cnt_n = 4'd0;

else

cnt_n = cnt + 1'b1;//实现累计

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt <= 4'b0;

else

cnt <= cnt_n;// 控制时许

end

endmodule

verilog HDL 起始于1983年,后来有cadence公司收购,candence 公司对verilog 进行了公开,之后IEEE 一直对verilog 进行升级和维护,目前最新的有system verilog

VHDL语言

目前比较流行的硬件描述语言当属verilog 和VHDL,两者具体区别如下:

VHDL 开始主要是军方使用,并且VHDL 相比verilog 更加的难以学习和理解,所以现在verilog是主流,对fpga开发或者数字芯片设计的可以优先学习verilog。

工程中实际作用:

fpga 具有很强的灵活性和并行运算的能力,在很多场合普通的单片机(比如st或者ti的mcu)不能满足特点需求,在笔者从事的电机行业,如果使用普通的单片机进行电机控制,控制频率会被限制在10k的数量级,但是如果使用fpga进行控制则控制周期可以达到100k。减小系统的延迟,这可以大大的提高系统带宽,所以高端的伺服控制器都会加配FPGA。

对于数字芯片行业,在芯片实际生产前,都会需要对算法进行测试,这个时候就会用verilog语言先实现算法,然后把算法下载到fpga中,在fpga 中进行功能测试。提前发现问题,减小开发bug

4501

4501

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?