名称:象棋游戏倒计时器设计Verilog代码vivado ego1开发板(文末获取)

软件:vivado

语言:Verilog

代码功能:

象棋游戏倒计时器设计

1、具有2个选手控制按键,选手1,按下按键选手2的时间开始倒计时

2、选手2,按下控制按键选手1的时间开始倒计时

3、若对方倒计时结束,则赢得比赛

4、设置获胜指示灯,有超时提醒

5、数码管显示2个选手倒计时分钟、秒钟

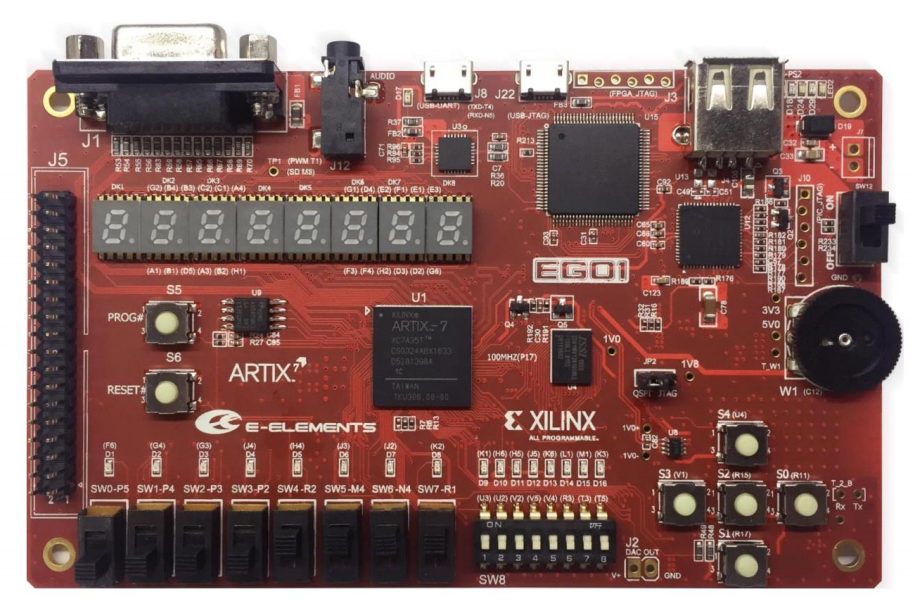

本代码已在 ego1开发板验证, ego1开发板如下,其他开发板可以修改管脚适配:

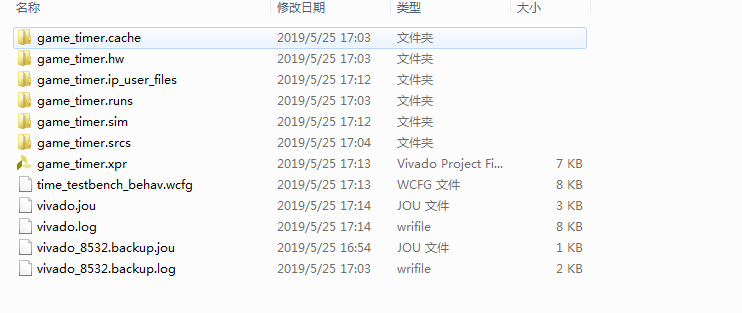

1. 工程文件

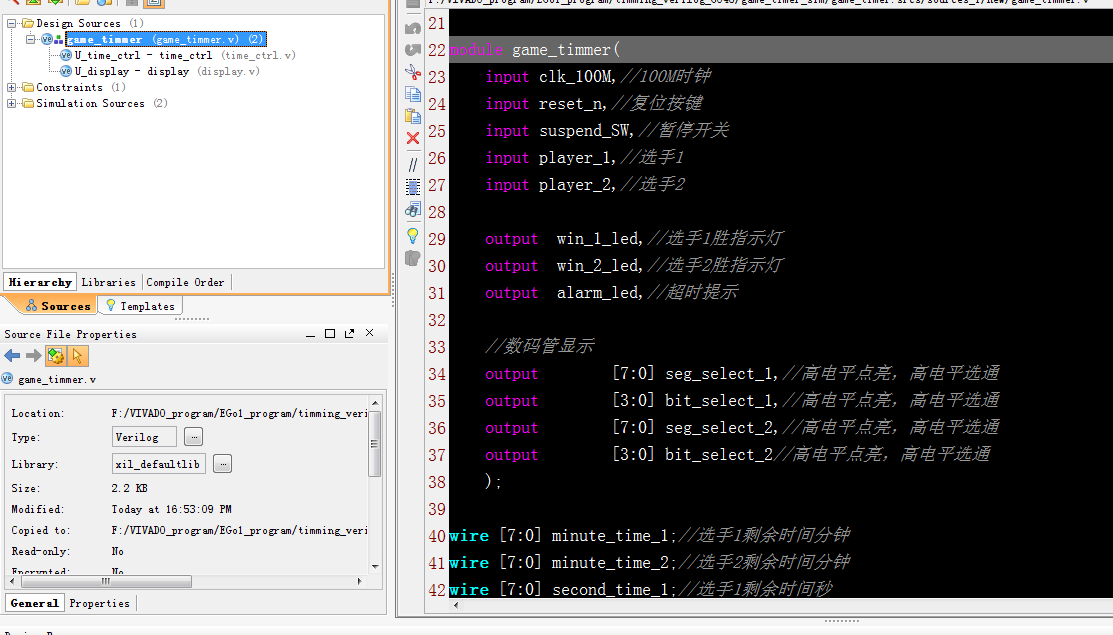

2. 程序文件

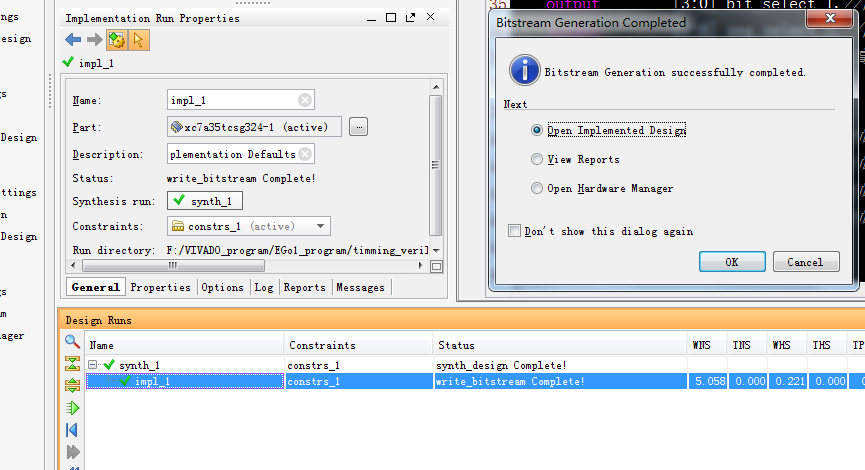

3. 程序编译

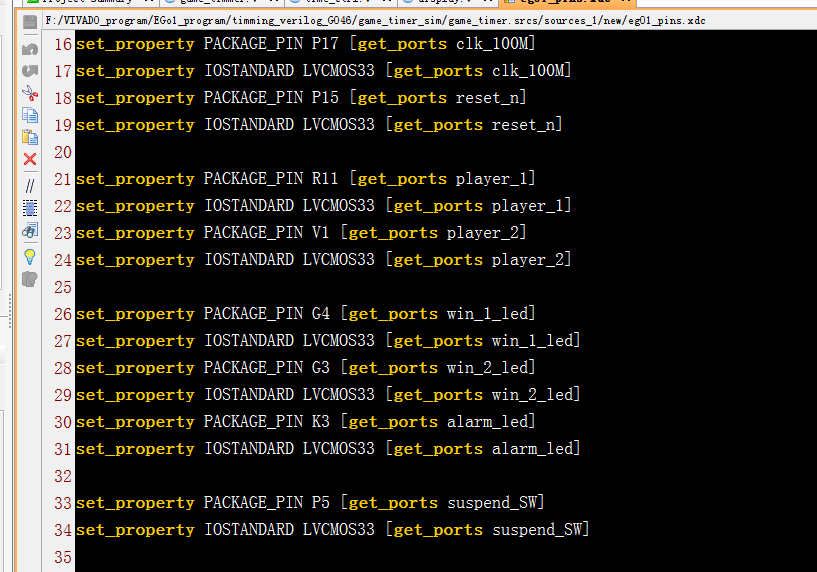

4. 管脚约束

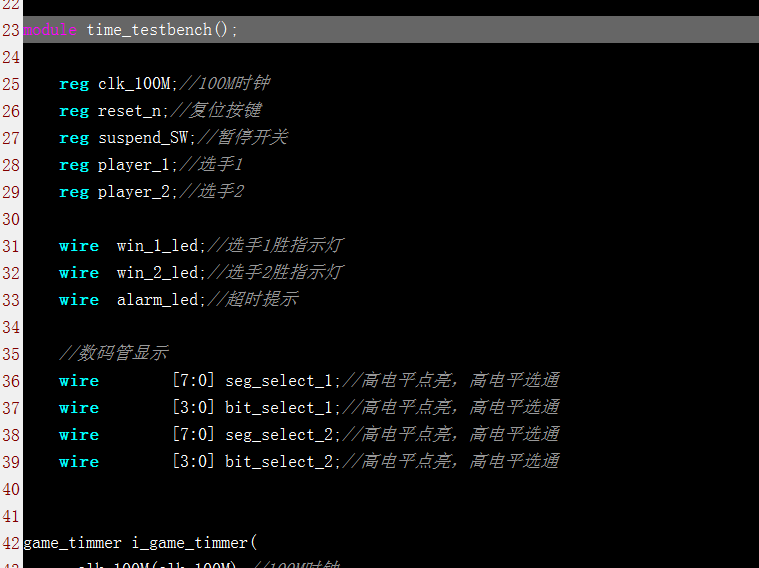

5. Testbench

6. 仿真图

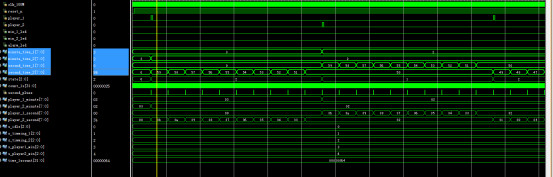

6.1 整体仿真

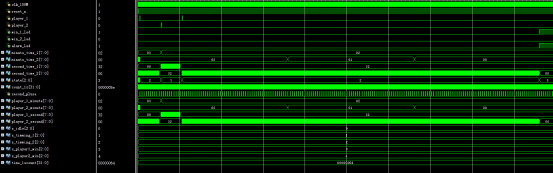

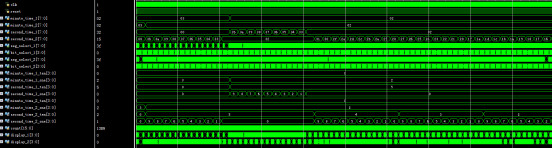

6.2 控制模块仿真

6.3显示模块仿真

部分代码展示:

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2019/05/25 14:21:45 // Design Name: // Module Name: game_timmer // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module game_timmer( input clk_100M,//100M时钟 input reset_n,//复位按键 input suspend_SW,//暂停开关 input player_1,//选手1 input player_2,//选手2 output win_1_led,//选手1胜指示灯 output win_2_led,//选手2胜指示灯 output alarm_led,//超时提示 //数码管显示 output [7:0] seg_select_1,//高电平点亮,高电平选通 output [3:0] bit_select_1,//高电平点亮,高电平选通 output [7:0] seg_select_2,//高电平点亮,高电平选通 output [3:0] bit_select_2//高电平点亮,高电平选通 ); wire [7:0] minute_time_1;//选手1剩余时间分钟 wire [7:0] minute_time_2;//选手2剩余时间分钟 wire [7:0] second_time_1;//选手1剩余时间秒 wire [7:0] second_time_2;//选手2剩余时间秒 wire ctrl_clk; assign ctrl_clk=clk_100M & suspend_SW;//suspend_SW控制暂停 time_ctrl U_time_ctrl( . clk_100M(ctrl_clk),//100M时钟 . reset_n(reset_n),//复位按键 . player_1(player_1),//选手1,按下高电平 . player_2(player_2),//选手2,按下高电平 . win_1_led(win_1_led),//选手1胜指示灯 . win_2_led(win_2_led),//选手2胜指示灯 . alarm_led(alarm_led),//超时提示 . minute_time_1(minute_time_1),//选手1剩余时间分钟 . minute_time_2(minute_time_2),//选手2剩余时间分钟 . second_time_1(second_time_1),//选手1剩余时间秒 . second_time_2(second_time_2)//选手2剩余时间秒 ); display U_display( . clk(clk_100M),//标准时钟,100MHz . reset(reset_n),//复位信号,低有效 . minute_time_1(minute_time_1),//选手1剩余时间分钟 . minute_time_2(minute_time_2),//选手2剩余时间分钟 . second_time_1(second_time_1),//选手1剩余时间秒 . second_time_2(second_time_2),//选手2剩余时间秒 . seg_select_1(seg_select_1), . bit_select_1(bit_select_1), . seg_select_2(seg_select_2), . bit_select_2(bit_select_2)//高电平点亮,高电平选通 ); endmodule

源代码

扫描文章末尾的公众号二维码

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?